Base station system (BTS) needs to meet the index requirements of signal link while meeting various standards. Este artículo introduce algunos dispositivos de enlace de señal que soportan ADCS dinámicos de alto rendimiento y dispositivos de radiofrecuencia en receptores digitales de radiofrecuencia., Por ejemplo: Convertidor analógico - digital de alto rendimiento dinámico, Amplificador de ganancia variable, Mezclador y Oscilador local, Y su aplicación en la Estación base típica se introduce en detalle., Cumplir los siguientes requisitos: Sistema de estación base de alto rendimiento dinámico, Alto rendimiento de interceptación y bajo ruido.

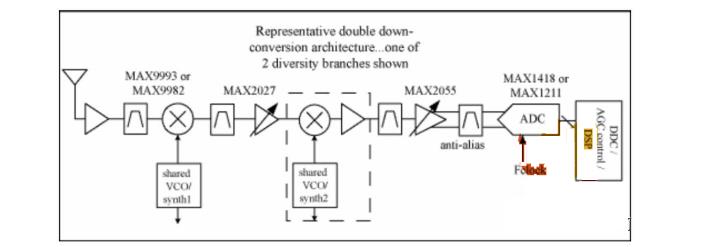

La mayoría de los receptores digitales son: Convertidor analógico a digital de alto rendimiento (ADC) Simulador. Por ejemplo:, El receptor digital de la Estación base celular necesita un rango dinámico suficiente para procesar grandes señales de interferencia, Una señal útil para desbloquear un nivel bajo. Maxim 15 bits 65msps ADC max1418 o 12 bits 65msps ADC max2121, Acoplamiento con mezclador integrado max9993 o max9982 de 2 GHz, Puede proporcionar excelentes características dinámicas para el circuito clave de dos etapas del receptor. Además, Maxim's intermediate frequency (if) digital adjustable gain amplifiers (DVGA) max2027 and max2055 can provide high third-order output cut-off point (OIP3) in many systems, Rango de ajuste de ganancia para satisfacer los requisitos del sistema.

Max1418 ADC chip y circuito

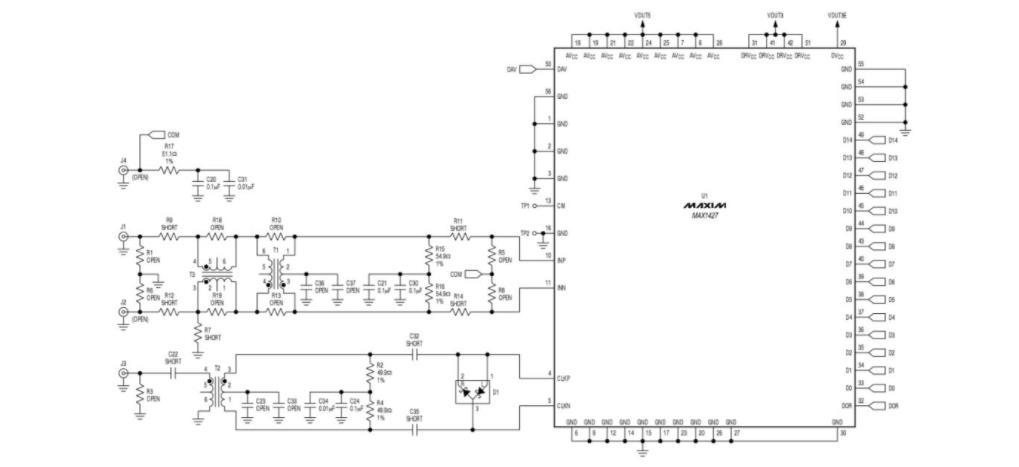

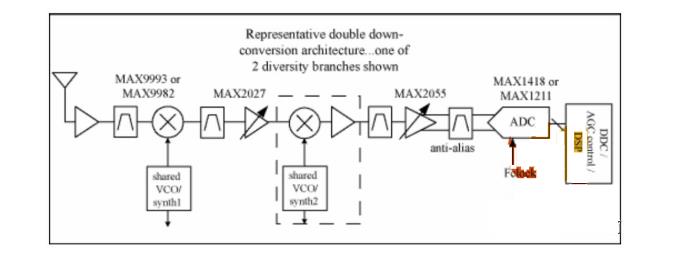

La Estación base celular (BTS: transceptor de estación base) consiste en varios módulos de hardware diferentes, uno de los cuales es el módulo transceptor (trx), que realiza las funciones de recepción de RF (RX) y transmisión (TX). En los antiguos amplificadores analógicos y tacs BTS, un transceptor sólo puede ser utilizado para manejar un portador de RF RX y TX dúplex completo. Para lograr la cobertura de llamadas requerida, muchos transceptores necesitan proporcionar suficientes portadores. Hoy en día, en todo el mundo, la tecnología analógica ha sido reemplazada por CDMA y WCDMA, y GSM fue adoptado en Europa hace una década. En CDMA, múltiples usuarios de llamadas utilizan la misma frecuencia RF, por lo que un transceptor puede procesar simultáneamente las señales de múltiples usuarios de llamadas. Hasta ahora, hay muchos esquemas de diseño CDMA y GSM. Los fabricantes de BTS también están explorando formas de reducir los costos y el consumo de energía. La optimización de la solución de un solo portador o el desarrollo de un receptor multicarrier es una solución eficaz. La figura 1 es un Diagram a de bloques de construcción de un receptor inframuestreado comúnmente utilizado en un dispositivo BTS.

Figura 1 diagrama de bloques de la estructura del receptor inframuestreado

En la figura 1, Los mezcladores Maxim max9993 y max9982 de 2 GHz proporcionan la ganancia y linealidad necesarias para muchos diseños, Y tiene un ruido de acoplamiento muy bajo, Por lo tanto, los mezcladores pasivos con alta pérdida ya no son necesarios. Max2027 y max2055 funcionan en las etapas de frecuencia media primera y segunda del receptor. OIP3 of these two devices can reach + 40dbm in the whole gain adjustment range. En el circuito mostrado en la figura 1, max1418 (15 bit, 65msps) and max1211 (12 bit, 65msps) are used as data converters. Además, Los productos de conversión de datos de Maxim también tienen otros dispositivos con tasas de muestreo, Capaz de satisfacer la mayoría de los requisitos de diseño. Si el segundo downconverter en la figura. 1 is omitted (shown in the dotted line), Circuito mostrado en la figura 1. 1 se convierte en una sola estructura de downconverter. Convertidor analógico - digital de bajo ruido Maxim: max1418.

La estructura del receptor undersampled que se muestra en la figura 1 tiene requisitos estrictos para el ruido y la distorsión del ADC. En el receptor, las señales útiles de bajo nivel se digitalizan individualmente o se acompañan de señales inútiles y de gran alcance que requieren más atención. Por lo tanto, para que el receptor funcione correctamente, el coeficiente de ruido efectivo del ADC debe calcularse sobre la base de las condiciones extremas de las dos señales, es decir, la señal útil mínima y la señal inútil máxima. Para las señales de entrada analógicas más pequeñas, el ruido térmico y el ruido de cuantificación dominan la base de ruido del ADC, que determina el coeficiente de ruido (NF) del ADC.

De hecho,, Se determina el coeficiente de ruido efectivo del ADC en condiciones de señal pequeña., and the cascade noise coefficient of analog circuit (RF or if) is determined accordingly. Este Ganancia mínima de potencia de ADC El circuito delantero debe cumplir los requisitos del coeficiente de ruido del circuito receptor. Normalmente, El valor de ganancia de potencia es el límite superior del nivel máximo de bloqueo o interferencia permitido por el receptor antes de la sobrecarga ADC. En BTS, Si no se utiliza AGC, the dynamic range of ADC can not meet the requirements of circuit noise coefficient (receiver sensitivity) and maximum blocking. El circuito AGC se puede colocar en un circuito de nivel RF o if, o el circuito AGC se puede colocar en un circuito de dos etapas.

Otros productos de la serie max1418 son especialmente adecuados para aplicaciones de Banda base con feinput = fclock / 2. Cuando los convertidores funcionan dentro de este rango de frecuencia, se obtiene un rango dinámico óptimo mediante el uso de estos dispositivos con excelentes características de Banda base. Estos productos incluyen un max1419 para una velocidad de reloj de 65 msps y un max1427 para una frecuencia de reloj de 80 msps. Su Banda base SFDR (rango dinámico no espurio) puede alcanzar 94,5 DBC.

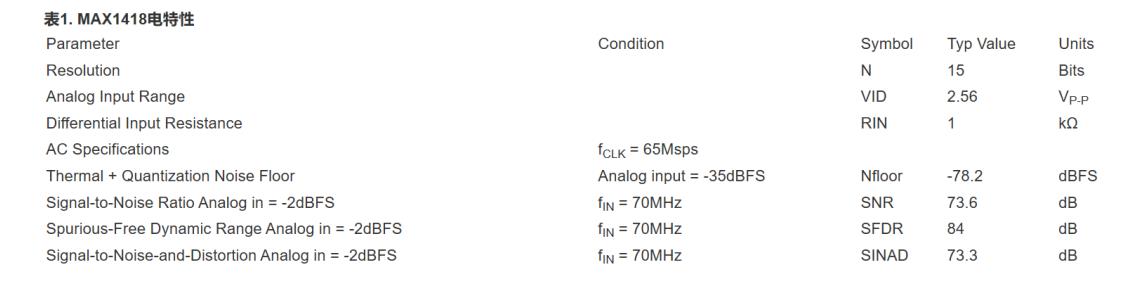

La Tabla 1 muestra los principales parámetros técnicos del max1418

El max1418 también puede trabajar con dispositivos de interfaz de 14 bits cuando el LSB no está conectado. De esta manera, el SNR se perderá ligeramente y el SFDR no se verá afectado.

La figura 2 muestra la distribución del ruido del ADC sin bloqueo. Aquí, suponiendo que el coeficiente de ruido total en cascada de todos los circuitos analógicos antes del ADC es de 3,5 DB, el objetivo de diseño es que el deterioro del coeficiente de ruido total causado por el ADC no exceda de 0,2 DB para satisfacer el requisito de sensibilidad del receptor de la Estación base CDMA. Este coeficiente de ruido debe dejar suficiente margen para la interfaz aérea, pero el resultado final depende del requisito de EB / no (relación entre la energía de bits y la densidad espectral de potencia acústica) del detector de última etapa. Basado en el sustrato de ruido de cuantificación max1418 en la Tabla 1, el coeficiente de ruido equivalente es de 26,9 DB cuando el reloj del dispositivo es de 61,44 msps (tasa de chip 50x). Debido al control de ganancia de proceso, el ruido ADC en el ancho de banda del canal CDMA de 1,23 MHz es 14 DB inferior al de Nyquist. En general, para obtener el coeficiente de ruido en cascada del receptor de 3,7 DB, la ganancia total debe ser de 36 DB.

Figura 2. Distribución del ruido ADC sin bloqueo

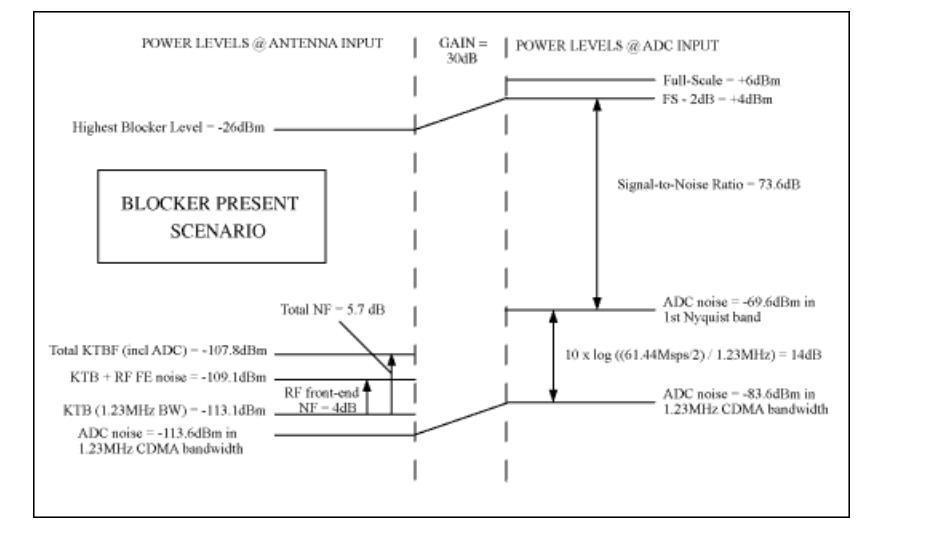

Cuando la ganancia frontal del ADC es de 36 DB, El nivel de bloqueo de tono único en el extremo de la antena superior a - 30dbm estará fuera del rango de entrada del ADC. La norma CDMA2000 - Estación base celular especifica que el nivel máximo de bloqueo permitido en el extremo de la antena es - 30dbm. En este momento, La ganancia frontal debe reducirse en 6 DB, Hacer que la señal de bloqueo máxima permitida para ser añadida al ADC sea mayor dentro de los límites permitidos por la especificación estándar. Supongamos un margen de 2db restante, El nivel máximo de bloqueo en el extremo de la antena se convertirá en - 26 DBm Señal de entrada máxima permitida para ADC will become + 4dbm when the front-end gain is reduced by 6dB (see Fig. 3). Cuando se produce un bloqueo de tono único, the cellular standard allows the total interference (noise + distortion) to deteriorate by 3dB relative to the reference sensitivity, Pero cómo distribuir 3db entre ruido y distorsión se deja al diseñador.

Supongamos que la ganancia AGC es de 6 DB en el caso de la señal bloqueada, y el diseño permite que el ruido en cascada en la parte delantera de la radiofrecuencia y la distorsión reduzcan NF en 1 dB (valor nominal 3,5 DB). Cuando la ganancia frontal del ADC es de sólo 30 DB, la relación señal - ruido del ADC determina que el coeficiente de ruido efectivo del ADC es de 29,4 DB, y el coeficiente de ruido del receptor subordinado "condición de bloqueo" es de 5,7 DB, que es 2 DB inferior al coeficiente de ruido de 3,7 DB calculado De acuerdo con la sensibilidad del receptor. Dado que no se tienen en cuenta las características espurias en este cálculo, el rango dinámico no espurio (SFDR) del ADC permite una reducción adicional de 1 Db. Cuando existe una señal de bloqueo, sinad se puede utilizar para calcular el NF efectivo, y el ruido y la base SFDR ya no se pueden calcular por separado.

Figura 3. Respuesta al ruido ADC en caso de bloqueo

Max111211 estructura de conversión permitida hacia abajo

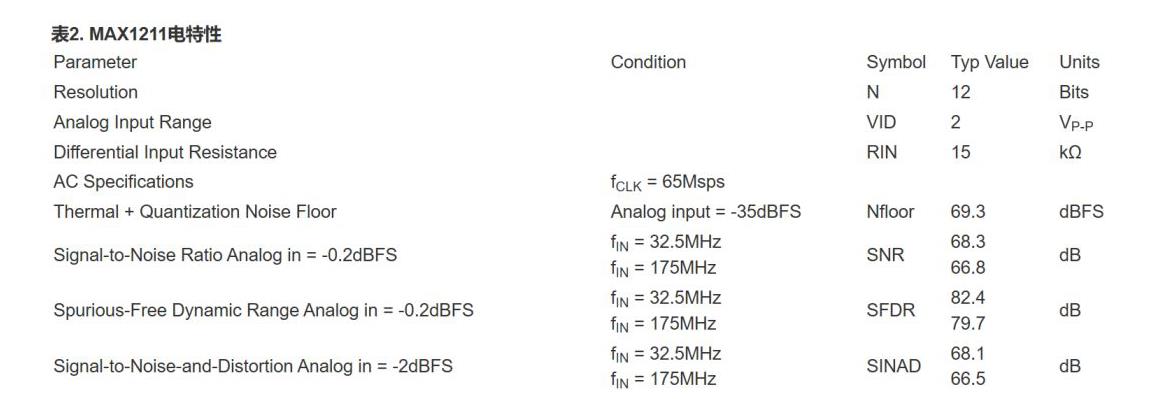

Si se pueden obtener suficientes índices SNR y SFDR en bandas de frecuencia más altas y más altas, se puede utilizar un circuito undersampled en una estructura de conversión principal hacia abajo. El convertidor max111211 de 12 bits y 65msps está diseñado con esta estructura. Sus Pines son compatibles con los próximos convertidores 80msps y 95msps. Esta serie de equipos puede muestrear directamente el número de frecuencia intermedia de la señal de entrada con una frecuencia de hasta 400 MHz. Además, tiene otras características avanzadas, como la entrada del reloj puede ser una señal diferencial o una señal de un solo extremo, y el ciclo de trabajo del reloj puede oscilar entre el 20% y el 80%. Además, tiene un indicador de validez de datos (reloj y secuencia de datos simplificados) y utiliza un pequeño paquete qfn de 40 Pines (6 mm x 6 mm x 0,8 mm), complementos binarios y formatos de salida digital de código gris. La tabla 2 muestra las características típicas de CA del max111211 con una frecuencia de entrada analógica de 175 MHz.

Figura 2. Características eléctricas del max1211

En comparación con la estructura de conversión de frecuencia secundaria, la conversión de frecuencia primaria tiene ventajas obvias. Debido a la eliminación del segundo mezclador de conversión hacia abajo, el Segundo Circuito de ganancia de frecuencia intermedia y el segundo sintetizador lo, el número de componentes y el espacio de la placa de circuito se pueden reducir en aproximadamente un 10% y el costo se puede ahorrar de $10 a $20.

Se considera la dispersión de diferentes estructuras. Si se necesita un mayor ahorro en el número de componentes, el espacio de tablero, el consumo de energía y el costo, se puede utilizar la estructura de conversión de frecuencia primaria que se muestra a continuación. Supongamos que el receptor CDMA2000 diseñado funciona en la banda de frecuencia PCS, la tasa de muestreo es de 61,44 msps, la frecuencia de referencia del sintetizador es de 30,72 MHz, el Centro de la primera frecuencia intermedia se selecciona en la Sexta banda Nyquist de 169 MHz, y el ancho de banda es de aproximadamente 1,24 MHz. Para la estructura DDS, las mismas frecuencias centrales de primera y segunda frecuencia intermedia de 169 MHz son 46,08 MHz en la banda Nyquist de segundo orden.

Características parasitarias hipotéticas de las arquitecturas SDC y DDC

En el cuadro 3 se enumeran las siguientes hipótesis: Portador de radiofrecuencia espurio Buscar cerca del extremo superior de la banda de frecuencia de PCS en un solo portador, primary down conversion (SDC) and two down frequency (DDC) structures are used. Para la estructura SDC, 134 componentes armónicos se pueden encontrar en la frecuencia de recepción de radiofrecuencia, Banda de frecuencia del espejo receptor, Banda IF y Banda espejo IF. La mayoría de estas señales espurias tienen un orden superior y no reducen el rendimiento de recepción.. Para la estructura DDC, Búsqueda espuria encontrará más de 2400 armónicos, Más de 18 veces mayor que la estructura SDC. Estos armónicos se distribuyen en la banda de frecuencia de recepción de radiofrecuencia, Banda de frecuencia del espejo receptor, Banda de frecuencia intermedia de primera etapa, Banda de espejo if de primera etapa, Banda de frecuencia intermedia de segundo nivel y Banda de imagen if de segundo nivel. Para señales espurias de armónicos de reloj de orden superior y frecuencias de referencia del sintetizador, Puede ser suprimido por una cuidadosa consideración de la disposición del tablero o añadiendo filtros al diseño. Sin embargo,, Es difícil suprimir un gran número de componentes espurios de orden inferior.

Amplificadores de frecuencia media de Maxim: max2027 y max2055

Maxim también proporciona una ganancia de control digital de 1 dB por etapa y un amplificador if de alto rendimiento. Max2027 es un amplificador de ganancia de control digital (dvga). Adopta el modo de entrada / salida única, puede funcionar en el rango de frecuencia de 50 MHz a 400 MHz, y el coeficiente máximo de ruido de ganancia es de sólo 5 DB. Max2055 es un dvga de entrada única / salida diferencial que conduce ADCS de alto rendimiento en el rango de frecuencia de 30 MHz a 300 MHz. El transformador boost se puede utilizar entre la salida diferencial del max2055 y la entrada diferencial del ADC. El transformador proporciona accionamiento diferencial, lo que facilita el equilibrio entre las señales de salida. Los dos dvga funcionan con un sesgo de 5v y tienen un oip3 de + 40 dBm en todo el rango de ajuste de ganancia. Para más detalles, consulte el sitio web de Maxim (china.maximantegrade.com). Mezclador de alta linealidad de Maxim: max9993 y max9982.

En el circuito receptor, el mezclador a menudo soporta una mayor señal de entrada, lo que requiere un rendimiento más estricto. En condiciones ideales, la amplitud y la fase de la señal de salida del mezclador son proporcionales a la amplitud y fase de la señal de entrada, y la relación de escala es independiente de la señal lo. De acuerdo con esta suposición, la respuesta de amplitud del mezclador está linealmente relacionada con la entrada de radiofrecuencia y es independiente de la señal de entrada local.

Sin embargo,, La no linealidad del mezclador producirá algunas señales de mezcla innecesarias, Esto se llama una reacción falsa., Esta es la respuesta de banda if generada por la señal que llega al puerto RF del mezclador y no se espera que aparezca. Una señal perdida inútil interferirá Señal RF útil. La frecuencia if del mezclador puede ser dada por la siguiente fórmula:

Si = ± mfrf - ± nflo, if, RF y lo son las frecuencias de señal de sus respectivos puertos, M y n son órdenes armónicas después de mezclar las señales RF y lo.

Los mezcladores de equilibrio integrados (o activos), como max9993 y max9982, han recibido mucha atención debido a su mejor rendimiento que los sistemas de mezcla pasiva. Cuando m o n es un n úmero par, el mezclador de equilibrio puede suprimir algunas respuestas espurias, y el segundo rendimiento armónico es mejor. El mezclador de doble equilibrio ideal puede suprimir todas las respuestas de m o n (o ambos) pares. En un mezclador de doble equilibrio, los puertos if, RF y lo están aislados entre sí. Los mezcladores pueden superponerse en las bandas if, RF y lo mediante el uso de transformadores de desequilibrio diseñados razonablemente. Las características de max9993 y max9982 incluyen: bajo coeficiente de ruido, Buffer lo, accionamiento lo bajo, interruptor lo que permite dos entradas lo, excelentes características de ruido lo, etc. además, los transformadores de desequilibrio RF están integrados en los puertos RF y lo.

Estos mezcladores de Maxim están incrustados en el Buffer lo y tienen un excelente rendimiento de ruido lo, lo que reduce los requisitos para la fuente de alimentación lo. En general, la combinación de ruido lo y señales de bloqueo de entrada de alto nivel reducirá la sensibilidad de recepción. Max9993 y max9982 contienen buffers lo de bajo ruido para reducir el impacto en la sensibilidad de recepción en caso de bloqueo. Por ejemplo, supongamos que el ruido de banda lateral de la señal de entrada vco es de - 145 dBc / h Z, y la característica típica del ruido de vibración local de max9993 es de - 164 dBc / Hz, por lo que el ruido de banda lateral compuesta sólo disminuye de 0,05 dBc / h a - 144,95 DBC / Z. De esta manera, el usuario no sólo proporciona una señal lo de bajo nivel para el mezclador, sino que también asegura que las características de mezcla del receptor no se degradan debido al rendimiento del Buffer lo incorporado en el max9993.

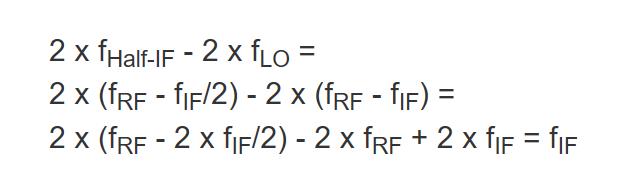

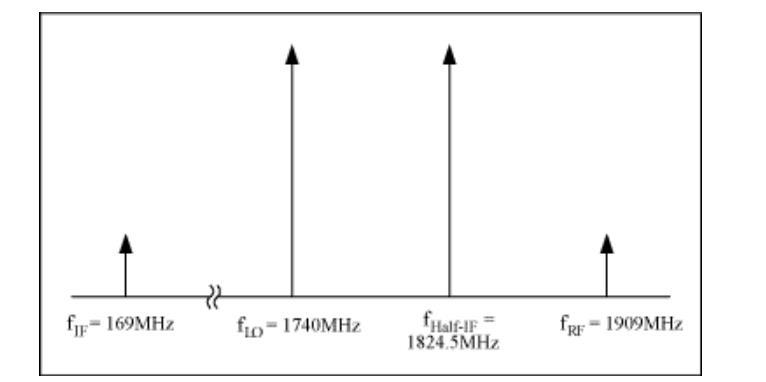

Además, hay una respuesta parasitaria difícil de segundo orden, también conocida como respuesta parasitaria de media frecuencia intermedia (1 / 2 de frecuencia intermedia). Para la inyección de extremo bajo, el orden del mezclador es: M = 2, n = - 2; Para la inyección de alta gama, el orden del mezclador es: M = - 2, n = 2. Cuando la inyección baja es baja, la frecuencia de entrada de la respuesta parasitaria de semifrecuencia intermedia es inferior a la frecuencia de radiofrecuencia requerida (figura 4). Las frecuencias de radiofrecuencia necesarias son 1909 MHz y 1740 MHz, y las frecuencias de frecuencia intermedia son 169 MHz. Aunque los portadores RF e if de CDMA tienen un ancho de banda de 1,24 MHz, se representa aquí como una señal de frecuencia única con una frecuencia portadora central. En este ejemplo, una señal inútil de 1824,5 MHz resulta en un componente de dispersión de media frecuencia de 169 MHz:

Por lo tanto, podemos obtener:

2 x 1824,5 MHz - 2 x 1740 MHz = 169 MHz

Figura 4. Posiciones de frecuencia intermedia de FRF útil, Flo, FIF y fhalf inútil

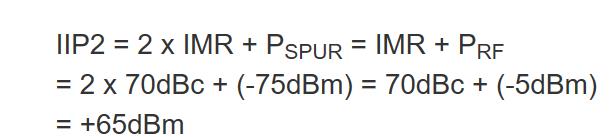

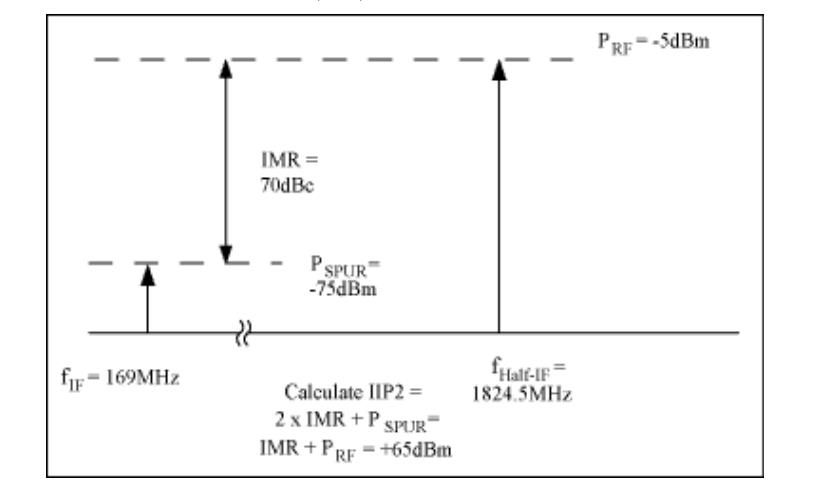

La supresión total (también conocida como respuesta espuria 2x2) se puede predecir a partir del segundo punto de corte ip2 del mezclador. La figura 5 muestra un IMR 2x2 o un valor espurio (datos max9993 de Maxim). Nota: el nivel de señal en la figura es el nivel de entrada del mezclador calculado por el rendimiento de la entrada ip2 (iip2). La fórmula de cálculo es la siguiente:

Dado que la respuesta típica espuria 2rf - 2Lo proporcionada por el filtro activo Maxim max9982 900mhz es de 65 DBC, el iip2 se calcula de la siguiente manera:

Figura 5. Cálculo del segundo punto de corte de la señal de entrada del mezclador iip2

Cuando el requisito de ganancia del receptor no es alto, El ADC max1418 de 15 bits de Maxim tiene un excelente rendimiento de ruido, Por lo tanto, puede soportar un alto nivel de bloqueo o interferencia con un AGC mínimo. Los productos de la serie max1211 ADC son adecuados para la estructura de recepción de conversión de frecuencia primaria, Su primera frecuencia de entrada de frecuencia intermedia puede alcanzar 400 MHz. Además, Los mezcladores max9993 y max9982 de Maxim proporcionan la linealidad requerida, Bajo coeficiente de ruido y alta ganancia de potencia, Por lo tanto, el filtro pasivo puede ser omitido en el diseño del receptor.. The typical value of OIP3 of max2027 and max2055 DVGA in the whole gain adjustable range is about + 40dbm. Los receptores compuestos por estos componentes pueden mejorar el rendimiento de las soluciones de bajo costo a un nivel superior. Este artículo introduce algunos equipos de enlace de señales Convertidor analógico - digital de alto rendimiento dinámico Y dispositivos de radiofrecuencia en receptores digitales de radiofrecuencia, Si tiene alguna pregunta, por favor póngase en contacto con nosotros. IPCB.