Skema skematik papan salinan litar PCB ralat biasa

1. Ralat umum dalam skema PCB:

(1) Tiada isyarat tersambung ke pin laporan ERC:

Atribut A. I/O ditakrif untuk pins apabila pakej dicipta;

B. Ubahsuai atribut grid tidak konsisten bila mencipta komponen atau meletakkan komponen, dan pin dan baris tidak disambung;

C. Bila mencipta komponen, arah pin diputar, dan ia mesti disambung ke hujung nama bukan pin.

(2) Komponen keluar dari sempadan lukisan: tiada komponen dicipta di tengah kertas diagram dalam perpustakaan komponen.

(3) Jadual rangkaian fail projek yang dicipta hanya boleh diimport sebahagian ke dalam PCB: apabila mencipta senarai rangkaian, ia tidak dipilih sebagai global.

(4) Apabila menggunakan komponen berbilang-bahagian yang dicipta oleh diri sendiri, jangan guna anotasi.

2. Ralat umum dalam PCB:

(1) Dilaporkan bahawa NODE tidak ditemui bila memuatkan rangkaian:

A. Komponen dalam diagram skematik menggunakan pakej yang tidak berada dalam perpustakaan PCB;

B. Komponen dalam diagram skematik menggunakan pakej dengan nama yang tidak konsisten dalam perpustakaan PCB;

C. Komponen dalam diagram skematik menggunakan pakej dengan nombor pin tidak konsisten dalam perpustakaan PCB. Contohnya, tiga: nombor pins dalam sch ialah e, b, c, dan nombor pin dalam PCB ialah 1, 2, 3.

(2) Ia tidak sentiasa boleh dicetak pada satu halaman bila mencetak:

A. Ia bukan asal bila mencipta perpustakaan PCB;

B. Komponen telah dipindahkan dan diputar banyak kali, dan terdapat aksara tersembunyi diluar sempadan papan PCB. Pilih untuk papar semua aksara tersembunyi, mengurangkan PCB, dan kemudian alih aksara ke sempadan.

(3) Rangkaian laporan DRC dibahagi ke beberapa bahagian:

bermakna rangkaian ini tidak tersambung. Lihat fail laporan dan gunakan CONNECTEDCOPPER untuk mencarinya.

Selain itu, mengingatkan rakan-rakan untuk menggunakan WIN2000 sebanyak mungkin untuk mengurangi peluang skrin biru; eksport fail beberapa kali untuk membuat fail DDB baru untuk mengurangkan saiz fail dan peluang untuk membeku PROTEL. Jika anda membuat rancangan yang lebih rumit, cuba untuk tidak menggunakan kabel automatik.

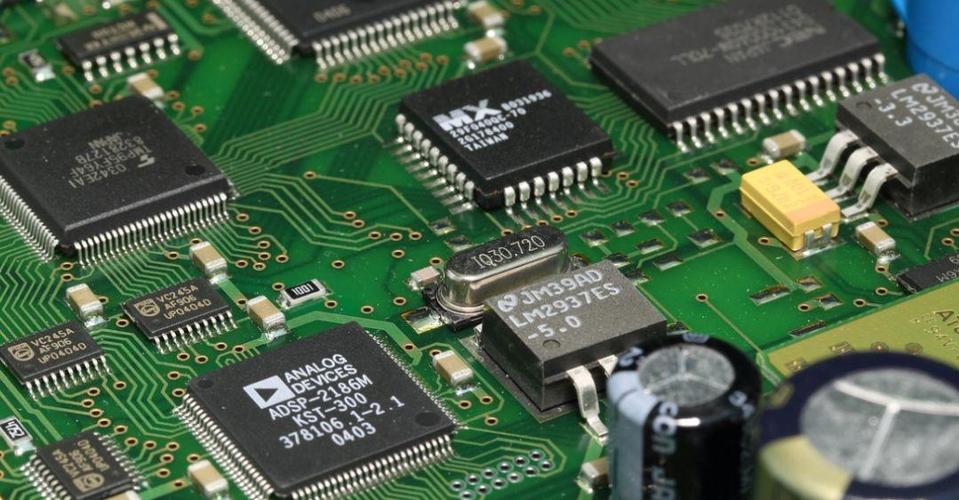

Dalam rancangan PCB, kabel adalah langkah penting untuk menyelesaikan rancangan produk. Ia boleh dikatakan bahawa persiapan sebelumnya dilakukan untuk ia. Dalam seluruh PCB, proses desain wayar adalah yang paling terbatas, kemahiran adalah yang paling kecil, dan muatan kerja adalah yang terbesar. Kabel PCB termasuk kabel satu sisi, kabel dua sisi dan kabel berbilang lapisan.

Ada juga dua cara kabel: kabel automatik dan kabel interaktif. Sebelum kabel automatik, anda boleh guna interaktif untuk prakabel baris yang lebih ketat. Pinggir akhir input dan akhir output patut dihindari bersebelahan dengan selari untuk menghindari gangguan refleksi.

Isolasi wayar tanah patut ditambah bila diperlukan, dan kabel dua lapisan bersebelahan patut bertentangan satu sama lain. Pemasangan parasit mungkin berlaku secara selari.