[Pembuat Substrate IC] keseluruhan proses dari desain cip IC, memproduksi ke pakej

1, Proses reka cip IC komplikasi

Proses penghasilan cip adalah seperti membina rumah dengan LEGO. Selepas wafer digunakan sebagai dasar, dan kemudian proses penghasilan cip ditampung lapisan demi lapisan, cip IC yang diperlukan boleh dihasilkan (ini akan diperkenalkan kemudian). Bagaimanapun, tanpa lukisan rancangan, ia tidak berguna untuk mempunyai kapasitas penghasilan yang kuat. Oleh itu, peran arkitek sangat penting. Tapi siapa arkitek dalam desain IC? Seterusnya, kertas ini akan memperkenalkan desain IC.

Dalam proses produksi IC, kebanyakan IC dirancang dan dirancang oleh syarikat reka IC profesional, seperti MediaTek, Qualcomm, Intel dan pembuat lain yang dikenali, semua merancang cip IC mereka sendiri dan menyediakan cip dengan spesifikasi dan efisiensi yang berbeza untuk pembuat turun untuk memilih. Kerana IC dirancang oleh setiap kilang, reka IC bergantung pada teknologi jurutera, dan kualiti jurutera mempengaruhi nilai sebuah perusahaan. Bagaimanapun, apabila jurutera merancang cip IC, apa langkah? Proses desain boleh dibahagikan kepada berikut.

Proses Pembuat IC

Raka Langkah Pertama dan Tetapkan Tujuan

Dalam rekaan IC, langkah yang paling penting adalah spesifikasi. Langkah ini adalah seperti memutuskan berapa banyak bilik dan bilik mandi yang diperlukan sebelum merancang bangunan, apa peraturan bangunan yang perlu dipenuhi, dan merancang selepas menentukan semua fungsi, sehingga tidak menghabiskan masa tambahan pada perubahan berikutnya. Design IC juga perlu melalui langkah yang sama untuk memastikan cip yang direka tidak akan mempunyai sebarang ralat.

Langkah pertama dalam bentuk spesifikasi adalah menentukan tujuan dan efisiensi IC dan tetapkan arah umum. Langkah berikutnya ialah untuk melihat protokol mana yang perlu dipenuhi. Contohnya, cip kad rangkaian tanpa wayar perlu mematuhi spesifikasi IEEE 802.11 dan spesifikasi lain. Jika tidak, cip tidak akan sesuai dengan produk di pasar, membuat ia tidak dapat disambung dengan peranti lain. Yang terakhir adalah untuk menetapkan kaedah pelaksanaan IC, mengalokasi fungsi berbeza ke unit berbeza, dan menetapkan kaedah sambungan antara unit berbeza, untuk menyelesaikan formulasi spesifikasi.

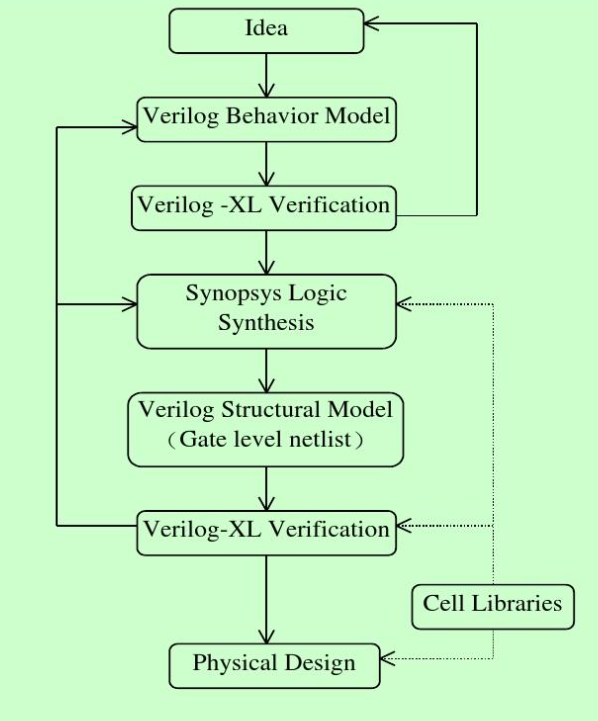

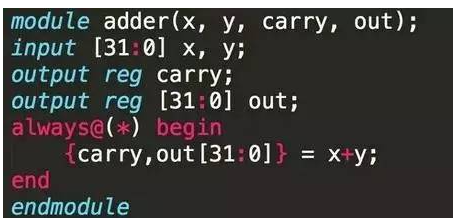

Selepas merancang spesifikasi, perincian merancang cip diikuti. Langkah ini adalah seperti menulis rancangan arkitektur awalnya dan melukis garis luar keseluruhan untuk kesehatan lukisan berikutnya. Dalam cip IC, bahasa keterangan perkakasan (HDL) digunakan untuk menggambarkan sirkuit. HDL yang biasa digunakan termasuk Verilog, VHDL, dll. fungsi IC boleh mudah diungkap dengan kod. Kemudian periksa kebijaksanaan fungsi program dan teruskan mengubahsuainya sehingga ia memenuhi fungsi yang diinginkan.

Contoh Verilog bagi penambah 32 bit

Dengan komputer, semuanya menjadi mudah

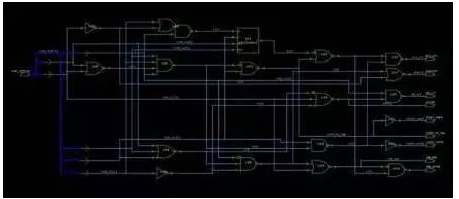

Dengan rancangan lengkap, langkah berikutnya adalah untuk melukis cetakan reka papan. Dalam reka IC, langkah sintesis logik adalah untuk meletakkan kod HDL yang ditentukan ke dalam alat automatasi reka elektronik (alat EDA), dan biarkan komputer menukar kod HDL ke dalam sirkuit logik untuk menghasilkan diagram sirkuit berikut. Kemudian, mengulang-ulang menentukan sama ada lukisan lukisan pintu logik memenuhi spesifikasi dan mengubahsuainya sehingga fungsi adalah betul.

Hasil sintesis unit kawalan

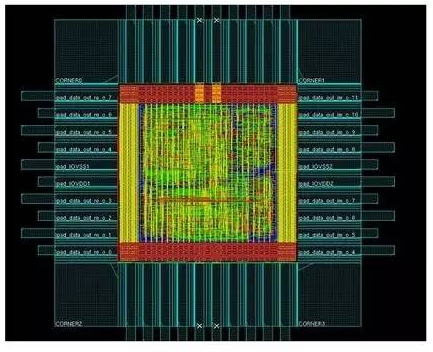

Akhirnya, letakkan kod sintesis ke dalam set lain alat EDA untuk bentangan sirkuit dan tempat dan laluan. Selepas pengesan terus menerus, diagram sirkuit berikut akan bentuk. Dalam gambar, anda boleh melihat warna yang berbeza seperti biru, merah, hijau dan kuning. Setiap warna berbeza mewakili topeng cahaya. Bagaimana menggunakan topeng?

layout dan winding

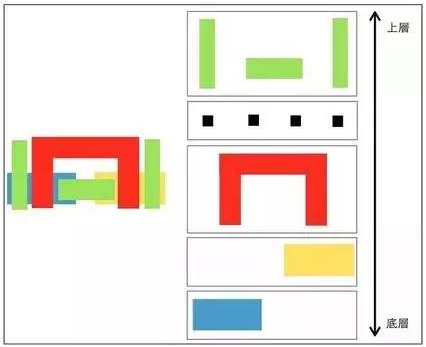

Lapisan topeng, tumpukan cip

Pertama-tama, ia diketahui bahawa IC akan menghasilkan topeng berbilang. Topeng ini mempunyai lapisan atas dan bawah, dan setiap lapisan mempunyai tugasnya sendiri. Figur berikut adalah contoh topeng sederhana. Mengambil CMOS, unsur paling as as dalam sirkuit terintegrasi, sebagai contoh, nama penuh CMOS adalah semikonduktor oksid logam komplementar, iaitu, menggabungkan NMOS dan PMOS untuk membentuk CMOS. Adakah yang demikian ialah setengah-setengah konduktor oksid logam (MOS)? Komponen semacam ini yang digunakan secara luas dalam cip adalah sukar untuk dijelaskan, dan ia sukar bagi pembaca biasa untuk memahami. Saya takkan belajar lagi di sini.

Dalam figur di bawah, sisi kiri ialah diagram sirkuit yang terbentuk selepas bentangan sirkuit dan membelakang. Ia telah diketahui bahawa setiap warna mewakili topeng. Di sebelah kanan ialah penyebaran tiap-tiap topi. Penghasilan adalah untuk bermula dari bawah, mengikut kaedah yang diusulkan dalam artikel sebelumnya tentang penghasilan cip IC, membuat lapisan demi lapisan, dan akhirnya menghasilkan cip yang diinginkan.

Sejauh ini, kita perlu mempunyai pemahaman awal tentang rekaan IC. Secara keseluruhan, ia jelas bahawa desain IC adalah khusus yang sangat kompleks. Terima kasih kepada kemampuan perisian yang diberi bantuan komputer, desain IC boleh dipantau. Fabrik desain IC bergantung dengan kebijaksanaan jurutera. Setiap langkah yang diterangkan di sini mempunyai keahlian sendiri dan boleh dibahagikan secara independen menjadi beberapa kursus profesional. Contohnya, menulis bahasa keterangan perkakasan tidak mudah. Ia hanya perlu dikenali dengan bahasa pemrograman, tetapi juga perlu memahami bagaimana sirkuit logik berfungsi dan bagaimana untuk menukar algoritma yang diperlukan ke program Bagaimana perisian sintetik menukar program ke gerbang logik.

2, apa itu wafer?

Dalam berita semikonduktor, kita sentiasa menyebutkan kilang wafer yang ditandai oleh saiz, seperti kilang wafer 8 inci atau 12 inci. Namun, apa yang disebut wafer? Bahagian mana 8 inci? Seberapa sukar untuk menghasilkan wafer besar? Berikut adalah perkenalan langkah demi langkah kepada asas yang paling penting Semiconductors - apa yang adalah "wafer".

Wafers adalah dasar untuk memproduksi semua jenis cip komputer. Kita boleh membandingkan penghasilan cip dengan membina rumah dengan blok Lego, dan menyelesaikan bentuk yang kita inginkan (iaitu, semua jenis cip) dengan menumpuk lapisan demi lapisan. Bagaimanapun, jika tidak ada dasar yang baik, rumah yang dibina akan gagal, yang bukan apa yang anda mahu. Untuk membuat rumah yang sempurna, anda perlu plat asas yang stabil. Untuk memproduksi cip, substrat ini adalah wafer yang akan diterangkan selanjutnya.

Pertama-tama, mari kita ingat bahawa apabila kita bermain dengan blok-blok tinggi sebagai kanak-kanak, akan ada projeksi bulatan kecil di permukaan blok-blok. Dengan struktur ini, kita boleh menusuk dua blok bersama-sama tanpa menggunakan lem. Penghasilan chip juga menetapkan atom yang ditambah kemudian dan substrat bersama-sama dengan cara yang sama. Oleh itu, kita perlu mencari substrat dengan permukaan yang bersih untuk memenuhi syarat yang diperlukan untuk penghasilan berikutnya.

Dalam bahan kuat, terdapat struktur kristal istimewa - kristal tunggal. Ia mempunyai karakteristik bahawa atom ditetapkan secara dekat satu per satu, dan boleh membentuk permukaan atom rata. Oleh itu, keperluan di atas boleh dipenuhi dengan menggunakan kristal tunggal untuk membuat wafer. Bagaimanapun, bagaimana untuk menghasilkan bahan seperti itu? Ada dua langkah utama: pembersihan dan lukisan kristal, dan kemudian bahan seperti itu boleh selesai.

Bagaimana membuat wafer kristal tunggal

Pembersihan dibahagikan menjadi dua tahap. Langkah pertama adalah pembersihan metalurgi. Proses ini adalah terutama untuk menambah karbon dan mengubah oksid silikon menjadi silikon dengan kesucian lebih dari 98% dengan cara pengurangan oksidasi. Kebanyakan penarafan logam, seperti besi atau tembaga, menggunakan kaedah ini untuk mendapatkan logam yang bersih yang cukup. Namun, 98% masih belum cukup untuk memproduksi cip dan perlu diperbaiki lebih lanjut. Oleh itu, proses Siemens akan digunakan lagi untuk pembersihan. Dengan cara ini, polisilikon bersih tinggi yang diperlukan oleh proses semikonduktor akan diperoleh.

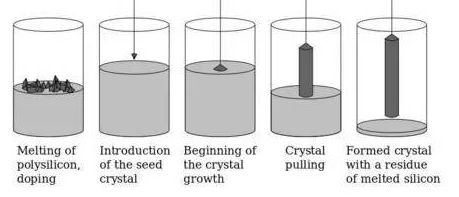

Proses penghasilan lajur silikon

Langkah berikutnya adalah lukisan kristal. Pertama, polisilikon bersih tinggi yang diperoleh di atas dicair untuk membentuk silikon cair. Kemudian, hubungi permukaan cair dengan satu benih kristal dan perlahan-lahan menariknya semasa berputar. Sebab kenapa silikon kristal tunggal diperlukan, ia adalah kerana pengaturan atom silikon adalah sama seperti orang-orang dalam baris. Ia akan memerlukan pemimpin untuk memberitahu orang kemudian bagaimana untuk mengatur dengan betul. Benih silikon adalah pemimpin penting untuk membiarkan atom kemudian tahu bagaimana untuk berturut-turut. Akhirnya, selepas atom silikon meninggalkan permukaan cair kuat, lajur silikon monokristal yang diatur dengan baik telah selesai

Lajur silikon monokristalin

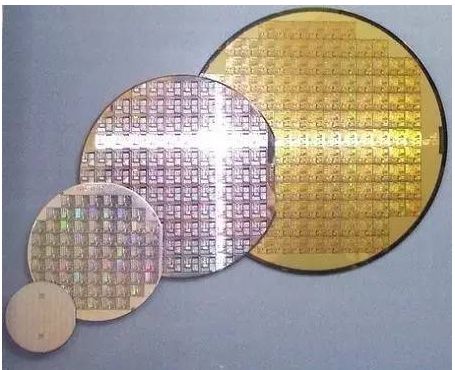

Namun, apa yang 8 inci dan 12 inci mewakili? Dia merujuk kepada diameter lajur kristal yang dihasilkan oleh kita, yang kelihatan seperti bahagian pemegang pensil. Permukaan diperlakukan dan dipotong menjadi potongan putih tipis. Apa kesulitan membuat wafer besar?

Seperti yang disebutkan di atas, proses penghasilan lajur kristal adalah seperti membuat gula-gula kapas, berputar dan membentuk pada masa yang sama. Jika anda pernah membuat marshmallow, anda perlu tahu bahawa ia sangat sukar untuk membuat marshmallow besar dan kuat, dan proses lukisan kristal adalah sama. Kelajuan putaran dan kawalan suhu akan mempengaruhi kualiti lajur kristal. Oleh itu, semakin besar saiz, semakin tinggi keperluan untuk kelajuan dan suhu. Oleh itu, lebih sukar untuk membuat wafer kualiti tinggi 12 inci daripada wafer 8 inci.

Namun, seluruh lajur silikon tidak boleh dibuat menjadi substrat untuk penghasilan cip. Untuk menghasilkan wafer silikon satu per satu, perlu memotong lajur silikon secara mengufuk ke wafer dengan pisau berlian, dan kemudian wafer boleh dipolis untuk membentuk wafer silikon yang diperlukan untuk memproduksi cip. Selepas begitu banyak langkah, penghasilan substrat cip selesai. Langkah berikutnya adalah untuk tumpukan rumah, iaitu, memproduksi cip. Macam mana nak buat cip?

Lapisan cip tumpukan

Selepas memperkenalkan apa wafer silikon, saya juga tahu bahawa memproduksi cip IC adalah seperti membina rumah dengan blok Lego, mencipta bentuk yang diinginkan dengan tumpukan lapisan demi lapisan. Namun, terdapat beberapa langkah untuk membina sebuah rumah, dan juga penghasilan IC. Apa langkah untuk menghasilkan IC? Kertas ini akan memperkenalkan proses penghasilan cip IC.

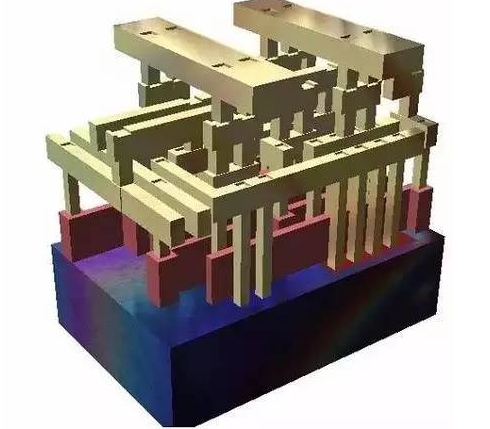

Sebelum kita mulakan, kita perlu pertama-tama memahami apa cip IC. IC, nama penuh sirkuit terintegrasi, boleh dilihat dari namanya bahawa ia menggabungkan sirkuit yang direka dalam cara tertentu. Dengan kaedah ini, kita boleh mengurangi kawasan yang diperlukan untuk menyambung sirkuit. Figur berikut adalah diagram 3D sirkuit IC. Ia boleh dilihat bahawa strukturnya adalah seperti sinar dan lajur rumah, tumpukan lapisan demi lapisan, itulah sebabnya penghasilan IC dibandingkan dengan membina rumah.

Profil 3D cip IC

Dari profil 3D cip IC dalam figura di atas, bahagian biru gelap di bawah adalah wafer yang diperkenalkan dalam artikel sebelumnya. Dari angka ini, kita boleh tahu lebih jelas betapa pentingnya substrat wafer bermain dalam cip. Adapun bahagian merah dan khaki, mereka akan selesai semasa produksi IC.

Pertama-tama, bahagian merah boleh dibandingkan dengan lorong di tingkat pertama bangunan tinggi. Hall di tingkat pertama adalah pintu gerbang rumah. Inilah tempat orang masuk dan keluar. Ia biasanya mempunyai lebih fungsi di bawah kawalan lalu lintas. Oleh itu, dibandingkan dengan lantai lain, pembangunan akan lebih kompleks dan memerlukan lebih banyak langkah. Dalam litar IC, lorong ini adalah lapisan pintu logik, yang merupakan bahagian yang paling penting dari seluruh IC. Pelbagai pintu logik digabung untuk menyelesaikan cip IC dengan fungsi lengkap.

Bagian kuning seperti lantai umum. Berbanding dengan tingkat pertama, ia tidak akan mempunyai struktur terlalu kompleks, dan setiap tingkat tidak akan berubah banyak semasa pembinaan. Tujuan lapisan ini adalah untuk menyambungkan pintu logik dalam bahagian merah bersama-sama. Alasan mengapa begitu banyak lapisan diperlukan adalah bahawa terdapat terlalu banyak garis untuk disambungkan bersama. Apabila lapisan tunggal tidak dapat mengakomodasi semua baris, perlu tumpukan beberapa lapisan untuk mencapai tujuan ini. Dalam proses ini, garis lapisan berbeza akan disambung ke atas dan ke bawah untuk memenuhi keperluan kawat.

Pembangunan lapisan dan lapisan mengikut struktur lapisan

Selepas mengetahui struktur IC, kita akan memperkenalkan cara untuk membuatnya. Bayangkan jika kita mahu membuat lukisan yang baik dengan sprei cat, kita perlu memotong plat penutup figura dan menutupinya di kertas. Kemudian semburkan cat secara bersamaan di atas kertas. Selepas cat itu kering, buang penutup. Selepas mengulang langkah ini, grafik bersih dan kompleks boleh selesai. Manufacturing IC adalah untuk tumpukan lapisan demi lapisan dengan meliputi dengan cara yang sama.

Apabila membuat IC, ia boleh dibahagi menjadi empat langkah di atas. Walaupun langkah dan bahan yang digunakan adalah berbeza dalam penghasilan sebenar, prinsip yang sama secara umum diterima. Proses ini agak berbeza dari lukisan cat. Penghasilan IC terlebih dahulu ditutup dan kemudian ditutup, sementara lukisan cat terlebih dahulu ditutup dan kemudian dicat. Setiap proses diterangkan di bawah.

-Splash logam: sempurnakan bahan logam yang digunakan pada wafer untuk membentuk filem tipis.

-Penutup foto: tempat pertama bahan foto pada wafer, lewat melalui topeng (prinsip topeng akan dijelaskan lain kali), memukul sinar pada bahagian yang tidak diinginkan, dan menghancurkan struktur bahan foto. Kemudian, bahan yang rosak dicuci dengan bahan kimia.

- Teknologi mengetuk: wafer silikon tanpa perlindungan photoresist dicetak oleh sinar ion.

-Pembuangan fotoresist: melenyapkan fotoresist yang tersisa menggunakan penyelesaian pembuangan fotoresist, untuk menyelesaikan proses.

Akhirnya, banyak cip IC akan selesai pada seluruh wafer. Seterusnya, selagi cip IC kuasa dua telah dipotong, ia boleh dihantar ke kilang pakej untuk pakej. Apa kilang pakej? Saya akan jelaskan nanti.

Comparison wafers of various sizes

3, Apa proses nanofabrikasi?

Samsung dan TSMC sangat panas dalam proses pembuatan semikonduktor maju. Mereka berdua ingin memimpin di wafer foundry untuk memenangkan arahan. Ia hampir menjadi perdebatan antara 14 nm dan 16 nm. Namun, apa maknanya dua nombor 14nm dan 16nm, dan bahagian mana ia merujuk? Apa manfaat dan masalah yang akan ia bawa ke masa depan selepas mengurangi proses? Kami akan menjelaskan proses nano di bawah.

Betapa halus Nano?

Sebelum kita mulakan, kita patut faham apa maknanya. Secara matematik, nanometer adalah 0.000000001 meter, tetapi ini adalah contoh yang sangat buruk. Lagipun, kita hanya boleh melihat banyak sifar selepas titik perpuluhan, tetapi kita tidak mempunyai perasaan praktik. Jika tebal paku dibandingkan, ia mungkin lebih jelas.

Jika and a benar-benar mengukur dengan peraturan dan ukuran, anda boleh tahu bahawa tebal paku adalah kira-kira 0.0001 meter (0.1 mm), iaitu, cuba memotong sisi paku ke dalam 100000 baris, dan setiap baris adalah kira-kira sama dengan 1 nm. Oleh itu, anda boleh bayangkan betapa kecil 1 nm.

Selepas mengetahui betapa kecil nano, kita juga perlu memahami niat mengurangi proses. Tujuan utama untuk mengurangi transistor adalah untuk masukkan lebih banyak transistor ke dalam cip yang lebih kecil, sehingga cip tidak akan menjadi lebih besar kerana peningkatan teknologi; Kedua, ia boleh meningkatkan efisiensi operasi pemproses; Selain itu, mengurangi volum juga boleh mengurangi konsumsi kuasa; Akhirnya, selepas saiz cip dikurangkan, lebih mudah untuk memasukkannya ke dalam peranti bimbit untuk memenuhi keperluan ringan di masa depan.

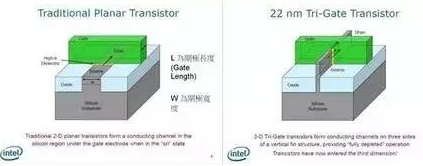

Kemudian kembali untuk mengeksplorasi apa proses nano. Ambil 14 nm sebagai contoh. Proses merujuk kepada bahawa wayar paling kecil dalam cip boleh menjadi 14 nm. Figur berikut menunjukkan penampilan transistor tradisional sebagai contoh. Tujuan utama untuk mengurangkan transistor adalah mengurangkan konsumsi tenaga, tetapi bahagian mana yang perlu dikurangkan untuk mencapai tujuan ini?

L di bawah kiri adalah bahagian yang kita harapkan untuk berkurang. Dengan mengurangi panjang gerbang, semasa boleh guna laluan yang lebih pendek dari hujung pembuangan hingga hujung sumber (jika anda berminat, anda boleh guna Google untuk mencari MOSFET, yang akan dijelaskan secara terperinci).

Selain itu, komputer berfungsi pada 0 dan 1. Bagaimana transistor boleh memenuhi tujuan ini? Kaedah adalah untuk menilai sama ada transistor mempunyai aliran semasa. Apabila tekanan disediakan di terminal gerbang (Green Square), arus akan mengalir dari terminal pembuangan ke terminal sumber. Jika tiada tenaga dibekalkan, arus tidak akan mengalir, jadi ia boleh mewakili 1 dan 0 (Sebab kenapa kita gunakan 0 dan 1 untuk penghakiman, jika anda berminat, anda boleh semak algebra brin. Kami gunakan kaedah ini untuk membuat komputer.)

Pengurangan saiz mempunyai had fizikal

Namun, proses penghasilan tidak boleh dikurangkan tanpa batas. Apabila kita mengurangkan transistor kepada kira-kira 20 nm, kita akan menghadapi masalah dalam fizik kuantum, sehingga transistor mempunyai kebocoran, mengurangi keuntungan yang diperoleh apabila l dikurangkan. Sebagai kaedah penambahan, konsep FinFET (tiga pintu) diperkenalkan, seperti yang dipaparkan dalam figur kanan atas. Dalam penjelasan sebelumnya yang dibuat oleh Intel, boleh diketahui bahawa penemuan teknologi ini boleh mengurangi kebocoran disebabkan oleh fenomena fizikal.

Yang lebih penting, kaedah ini boleh meningkatkan kawasan kenalan antara hujung pintu dan lapisan bawah. Dalam latihan tradisional (di atas kiri), permukaan kenalan hanya mempunyai satu pesawat, tetapi selepas menggunakan teknologi FinFET (tiga pintu gerbang), permukaan kenalan akan menjadi tiga dimensi, yang boleh mudah meningkatkan kawasan kenalan. Dengan cara ini, hujung pembuangan sumber boleh dibuat lebih kecil sementara menjaga kawasan kenalan yang sama, yang sangat membantu untuk mengurangi saiz.

Akhirnya, itulah sebabnya beberapa orang mengatakan bahawa kilang utama akan menghadapi tantangan yang cukup berat apabila memasuki proses 10 nm. Alasan utama ialah saiz atom adalah kira-kira 0.1 nm. Dalam kes 10 nm, terdapat hanya kurang dari 100 atom dalam garis, yang agak sukar untuk dihasilkan, dan selama ada cacat satu atom, seperti atom yang jatuh atau kotoran dalam proses penghasilan, akan ada fenomena yang tidak diketahui, yang akan mempengaruhi hasil produk.

Jika anda tidak dapat membayangkan kesulitan, anda boleh melakukan eksperimen kecil. Garis 10 dengan 100 kacang di atas meja * 10 kuasa dua, dan potong kertas untuk menutupi kacang, kemudian berus off kacang berikutnya dengan berus kecil, dan akhirnya membuat dia membentuk 10 * segiempat 5. Dengan cara ini, kita boleh tahu kesulitan yang dihadapi oleh kilang besar dan betapa sukarnya untuk mencapai tujuan ini.

Sebagaimana Samsung dan TSMC akan menyelesaikan produksi massa 14 nm dan 16 nm FinFET dalam masa depan yang dekat, mereka berdua mahu bersaing untuk OEM cip iPhone generasi seterusnya Apple. Kita akan melihat pertandingan komersial yang indah dan mendapatkan lebih simpanan kuasa dan telefon bimbit ringan. Terima kasih kepada keuntungan yang dibawa oleh undang-undang Moore.

4, memberitahu anda apa kumpulan adalah

Pengepasan, perlindungan akhir dan integrasi cip IC

Selepas proses yang panjang, dari desain ke penghasilan, kita akhirnya mendapat cip IC. Namun, cip agak kecil dan tipis. Jika ia tidak dilindungi di luar, ia akan mudah dicakar dan rosak. Selain itu, kerana saiz cip kecil, ia tidak mudah untuk meletakkannya secara manual pada papan sirkuit tanpa shell yang lebih besar. Oleh itu, kertas ini akan menjelaskan dan memperkenalkan pakej berikutnya.

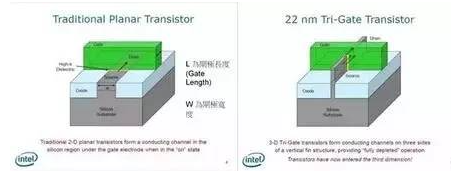

Pada masa ini, terdapat dua pakej biasa, satu adalah pakej dip biasa dalam mainan elektrik, yang kelihatan seperti centipede dalam hitam, dan yang lain adalah pakej BGA biasa bila membeli CPU kotak. Macam pada kaedah pakej lain, PGA (array grid pin) digunakan oleh CPU awal; Array grid pin) atau QFP yang diperbaiki (plastik square flat pack) dip. Kerana terdapat banyak kaedah pakej, pakej dip dan BGA akan diperkenalkan di bawah.

Pakej tradisional, kekal

Perkara pertama untuk memperkenalkan adalah pakej dalaman dua; Dip), seperti yang boleh dilihat dari figura di bawah, cip IC dengan pakej ini akan kelihatan seperti centipede hitam pada kaki sambungan baris ganda, yang mengesankan. Kaedah pakej ini adalah teknologi pakej IC yang paling awal, yang mempunyai keuntungan dari biaya rendah dan sesuai untuk cip kecil tanpa terlalu banyak wayar. Namun, kerana kebanyakan daripada mereka adalah plastik, kesan penyebaran panas adalah lemah, yang tidak dapat memenuhi keperluan cip kelajuan tinggi semasa. Oleh itu, kebanyakan cip yang menggunakan pakej ini adalah cip yang kekal, seperti op741 dalam figur di bawah, atau cip IC dengan keperluan yang kurang untuk kelajuan operasi, cip yang lebih kecil dan kurang lubang sambungan.

Paparan melintas pelampur

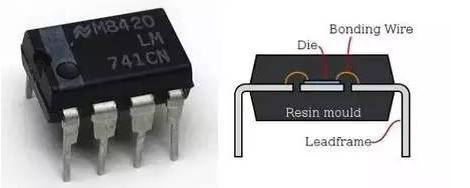

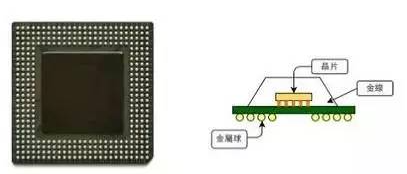

Bagi pakej tata grid bola (BGA), dibandingkan dengan dip, volum pakej lebih kecil dan mudah ditempatkan ke dalam peranti yang lebih kecil. Selain itu, kerana pin ditempatkan di bawah cip, ia boleh mengakomodasi lebih banyak pin logam daripada dip, yang cukup sesuai untuk cip yang memerlukan lebih banyak kenalan. Namun, kaedah pakej ini mempunyai kaedah sambungan yang tinggi dan kompleks, jadi ia kebanyakan digunakan dalam produk dengan harga unit yang tinggi.

Diagram skematik BGA menggunakan pakej cip balik

Dengan peningkatan peranti bimbit, teknologi baru telah melompat ke panggung

Namun, menggunakan kaedah pakej ini akan memakan volum yang besar. Contohnya, peranti bimbit dan peranti yang boleh dipakai sekarang memerlukan pelbagai komponen. Jika setiap komponen dikumpulkan secara bebas, ia akan memakan banyak ruang untuk dikombinasikan. Oleh itu, terdapat dua kaedah untuk memenuhi keperluan mengurangi volum, iaitu SOC (sistem pada cip) dan SIP (sistem dalam paket).

Pada permulaan naik telefon pintar, terma SOC boleh ditemui dalam majalah keuangan utama. Namun, apa itu SOC? Secara singkat, ia adalah untuk mengintegrasikan IC dengan fungsi yang berbeza ke dalam satu cip. Kaedah ini tidak hanya boleh mengurangi volum, tetapi juga mengurangi jarak antara ICs yang berbeza dan meningkatkan kelajuan pengiraan cip. Adapun kaedah penghasilan, ia adalah untuk meletakkan ICs yang berbeza bersama-sama dalam tahap desain IC, dan kemudian membuat topeng melalui proses desain yang diterangkan sebelumnya.

Namun, SOC tidak hanya mempunyai keuntungan. Rancang SOC memerlukan kerjasama teknikal yang besar. Apabila cip IC dikemas, ia dilindungi oleh pakej luar, dan jarak antara IC dan IC jauh, jadi tiada gangguan antara satu sama lain. Bagaimanapun, apabila semua ICs berkemas bersama-sama, ia adalah permulaan mimpi buruk. Fabrik desain IC patut berubah dari IC desain sederhana asal ke IC yang memahami dan mengintegrasikan berbagai fungsi, meningkatkan muatan kerja jurutera. Selain itu, akan ada banyak situasi, seperti isyarat frekuensi tinggi cip komunikasi mungkin mempengaruhi IC fungsi lain.

Selain itu, SOC juga perlu mendapatkan kebenaran IP (properti intelektual) dari pembuat lain untuk meletakkan komponen yang dirancang oleh orang lain ke SOC. Kerana pembuatan SOC memerlukan perincian rancangan seluruh IC untuk membuat topeng lengkap, yang juga meningkatkan kos rancangan SOC. Beberapa orang mungkin bertanya mengapa tidak merancang satu sendiri? Kerana merancang beberapa ICs memerlukan banyak pengetahuan berkaitan dengan IC, hanya syarikat yang mempunyai banyak wang seperti apel boleh mempunyai anggaran untuk merekrut jurutera terbaik dari syarikat yang dikenali untuk merancang IC yang baru. Ia lebih berkesan untuk bekerja sama dan membenarkan daripada untuk mengembangkan IC mereka sendiri.

Kompromi, SIP muncul

Sebagai alternatif, SIP melompat ke panggung mengintegrasi cip. Berbeza dari SOC, ia membeli berbagai IC dan merampasnya untuk kali terakhir, sehingga menghapuskan langkah kebenaran IP dan mengurangkan banyak kos desain. Selain itu, kerana mereka adalah ICs independen, darjah gangguan antara satu sama lain adalah jauh dikurangi.

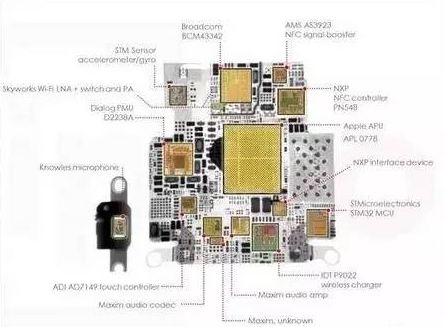

Jam Apple menggunakan teknologi SIP untuk pakej

Produk paling terkenal menggunakan teknologi SIP adalah jam apel. Kerana ruang dalaman jam terlalu kecil, ia tidak boleh mengadopsi teknologi tradisional, dan kos desain SOC terlalu tinggi, SIP telah menjadi pilihan pertama. Dengan teknologi SIP, ia tidak hanya boleh mengurangi volum, tetapi juga mengurangi jarak antara setiap IC, yang telah menjadi kompromi yang boleh dilakukan. Figur berikut adalah diagram struktur cip jam Apple. Anda boleh melihat bahawa sejumlah besar ICs yang termasuk di dalamnya.

Diagram konfigurasi dalaman cip S1

Selepas pakej selesai, perlu memasuki tahap ujian. Pada tahap ini, perlu mengesahkan sama ada IC pakej berfungsi secara biasa. Selepas ia betul, ia boleh dihantar ke kilang pemasangan untuk membuat produk elektronik yang kita lihat. Sejauh ini, industri setengah konduktor telah menyelesaikan seluruh tugas produksi.