Gelişmiş s üreçlerin yanında, gelişmiş paketleme Moore'un yasasını devam etmek için anahtar bir teknoloji oldu. 2.5D, 3D ve Chiplets gibi teknolojiler son yıllarda yarı yönetici endüstrisinde sıcak temalar oldu. Nasıl, tam olarak, gelişmiş paketleme Moore'un yasasını devam etmekte önemli bir rol oynuyor? 2.5D, 3D ve Chiplets gibi paketleme teknolojilerin özellikleri nedir?

Yasal zeka (AI), araba interneti, 5G ve diğer uygulamalar ortaya çıktı ve hepsi hızlı hesaplama, yüksek hızlı transmisi, düşük latenci ve düşük enerji tüketimleri ile gelişmiş fonksiyonel çipleri kullanmalı. Ancak, hesaplama talebi birçok kez arttığı için Moore'un yasasını nasıl devam etmek yarı yönetici endüstri için bir zorluk.

Çip mikroskaları daha zorlaştığında, heterogenel integrasyon doğdu.

Diğer sözlerde, yarı yönetici gelişmiş süreçler 7 nm, 5 nm ve sonra 3 nm ve 2 nm'e taşınıyor. Transistor boyutları bu yüzden atomların fiziksel volum sınırlarına yaklaşıyor. Elektronik ve fiziksel sınırlar ayrıca gelişmiş süreçler gelişmeye devam etmek ve gelişmeye devam etmek için daha zorlaştırır.

Sonuç olarak gelişmiş süreçler geliştirmeye devam etmek üzere yarı yönetici endüstri de çipinleri küçük ve etkili tutmak için diğer yollar arıyor. Çip tasarımı, sonra Moore'un yasasını devam etmek için yeni bir çözüm oluyor ve Heterogeneous Integration Design Architecture System (HIDAS) konsepti tarihi anında ortaya çıkıyor ve ICchips'in yenileme hareketi oluyor.

Böyle denilen heterogenel integrasyon, geniş olarak konuşurken, hafıza + lojik çip, fotoelektrik + elektronik komponentler gibi iki farklı çip integrasyonudur. Diğer sözleriyle, farklı süreçler ve farklı özellikler ile iki çip integrasyonu heterogenel integrasyon denilebilir.

Çünkü uygulama pazarı daha çeşitlidir, her ürünün maliyeti, performans ve hedef nüfusu farklıdır, bu yüzden gereken heterogenel integrasyon teknolojisi de farklıdır ve pazar odaklanması yavaşça ortaya çıktı. Bu yüzden IC foundry, manufacturing and semiconductor equipment industry has invested in heterogeneous integration development, 2.5D, 3D packaging, Chiplets and other popular packaging technology, are based on the heterogeneous integration idea, such as bamboo sprout after a spring spring.

2.5D paketi çip üretiminin maliyetini etkili olarak azaltır

Geçmişte, çipleri birlikte birleştirmek için, sistemin çoğunu, PiP (Paket Paket) paketi, PoP (Paket Paket) paketi gibi bir Paket (SiP) teknolojisinde kullanılır. Ancak akıllı telefonlar, AIoT ve diğer uygulamalar olarak, sadece yüksek performansı gerekmez, ama da küçük boyutta, düşük enerji tüketimine ihtiyacımız var. Böylece bir durumda, volumu azaltmak için daha fazla çip toplamak için bir yol bulmalıyız. Bu yüzden, orijinal SiP'nin yanında şu anki paketleme teknolojisi, ayrıca üç boyutlu paketleme teknolojinin geliştirmesine doğru.

Önceki plastik "kablo taşıyıcısı" kullanmak yerine silikon karşılaştırıcısı (silikon karşılaştırıcısı) ile doğrudan silikon taşıyıcısı kullanmak ve farklı fonksiyonlarla birkaç çip paketlemek anlamına gelir. Diğer s özleriyle, silikon çiplerini silikon üzerinde eklemek, sürecin maliyetini ve fiziksel sınırlarını arttıran şekilde Moore'un yasasını hayatta tutar.

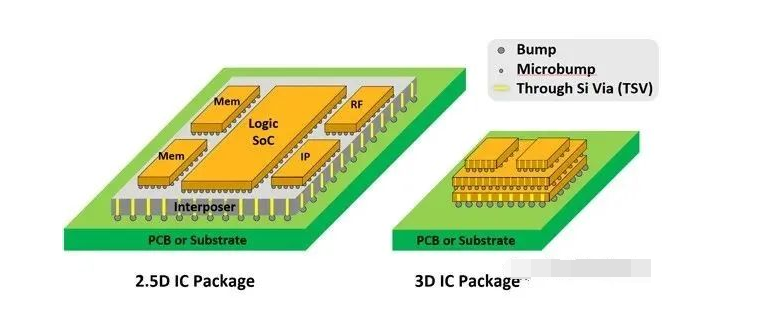

Ve stereoskop paketi 2.5D ve 3D paketi ile daha tanıtır. Burada 2.5D paketlerinden başlarız. Böyle denilen 2.5D paketi, ana konsepti Silicon Interposer (Silicon Interposer) üzerinde işlemciler, hafıza veya diğer çipler ayarlamak, mikro Bump tarafından bağlanmış, böylece Silicon Interposer içindeki metal kabloları farklı çiplerin elektronik sinyallerini bağlayabilir. Sonra, TSV a şağıdaki metal Bump'u bağlamak için kullanılır, ve kablo taşıyıcı tabağı çip, çip ve paketleme altını arasındaki daha yakın bir bağlantı sağlamak için dış metal topu bağlamak için kullanılır.

2.5D ve 3D paketleme popüler stereo paketleme teknolojisi. (Kaynak: ANSYS)

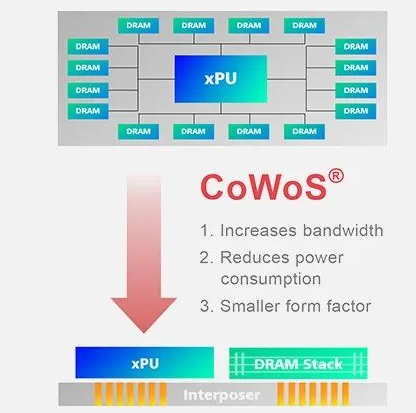

Şu anda iyi bilinen 2.5D paketleme teknolojisi TSMC'nin CoWoS'dan başka bir şey değil. CoWoS teknolojisinin konsepti, işlemciler, hafıza, etkinliği gibi, silikon ortalama katmanına yerleştirmek ve sonra onları Wafer (CoW) üzerindeki Chip'in paketleme süreci üzerinden aşağı altın altına bağlamak. Diğer sözleriyle, Chip ilk olarak Wafer (CoW) Chip'in paketleme süreci ile silikon Wafer ile bağlantılı, sonra CoW Chip substrat ile bağlantılı ve CoWoS'e bağlanmış. Bu paketleme modunu kullanarak, çoklu çip birlikte paketlenebilir ve Si Interposer aracılığıyla, küçük paketleme volumunun etkisini, düşük enerji tüketiminin ve daha az pinlerin etkisini sağlayabilir.

TSMC CoWos paketleme teknoloji konsepti. (Kaynak: TSMC)

CoWos'un yanında, hayranlık düzeyi paketleme de 2.5D paketleme yöntemi olarak klasifik edilebilir. Fan-out wafer-level paketinin prensipi, sıfır yarı yöneticinin ucundan paketlemek için yeniden dağıtma katına kadar gerekli devreleri çekmek. Bu yüzden, yükleme tabağını, Wire, Bump'u mühürlemeye gerek yok. Bu üretim maliyetini %30'a düşürebilir ve aynı zamanda çip küçük yapabilir. Aynı zamanda, çip alanı çok azaltılabilir. Ayrıca silikon perforasyonu ile daha yüksek maliyeti değiştirebilir, paketleme teknolojisi ile farklı komponentleri integrasyon amacını ulaştırmak.

Tabii ki stereo paketleme teknolojisi sadece 2,5D değil, ALSO 3B paketleme var. Peki, ikisinin ve SEMICONDUCTOR endüstri arasındaki fark nedir?

2.5D paketinin karşısında, 3B paketi çip üzerinde bir transistor (CMOS) yapısı oluşturarak ve silikon perforasyonlarını kullanarak, üstünde ve a şağıda farklı çip sinyallerinin elektronik sinyallerini bağlamak için çalışıyor, böylece hafıza ya da diğer çipların doğrudan vertikal üzerinde yerleştirilebilir.

Üç boyutlu paketleme doğrudan bir paket çip. (Kaynak: Hedef)

TSMC ve Intel, 3D paketleme teknolojisini aktif geliştirir

Intel (INTC) ve Taiwan Semiconductor (TSMC) 3 boyutlu paketleme için kendi teknolojileri var. Mantık "Foveros" 3D paketleme teknolojisini kullanıyor. Bu, operasyonları yönetmek için heterogenel stack logik kullanıyor ve her mantıklı çip birlikte koyabilir. Bu, ilk defa, geleneksel pasif silikon ortamlarından çip toplaması ve cpus, grafik ve AI işlemcilerine benzer yüksek etkileşimli mantıklı ürünlere, hafıza toplaması demek oluyor. Geçmişte, sıkıştırma sadece hafıza için kullanıldı, ama şimdi heterogenel sıkıştırma farklı hafıza ve hesap çiplerinin birleşmesini sağlamak için kullanılır.

Ayrıca, Intel üç yeni teknoloji geliştiriyor, yani birlikte EMIB, ODI ve MDIO. İki ya da fazla Foveros komponentlerinin bağlantısını sağlayabilir. Tasarımcılar da çok yüksek bandwidth ve çok düşük enerji tüketiminde simülatörler, hafıza ve diğer modüller birleşebilir. ODI teknolojisi küçük ve orta boyutlu çipler arasındaki tüm yönde bağlantı iletişimleri için daha fleksibillik sağlar. En yüksek çip, EMIB teknolojisi gibi diğer küçük çip ile iletişim kurabilir ve Foveros teknolojisi gibi silikon tarafından (TSV) delikten a şağıdaki aşağıdaki çıplak çip ile dikey olarak iletişim kurabilir.

Intel Foveros teknoloji konsepti. (Kaynak: Hedef)

Teknoloji aynı zamanda yüksek dikey deliklerden kullanır ki, paketleme altından en üst sol tabağa doğrudan güç sağlayan yüksek çukurlardan kullanır. Bu büyük delikler geleneksel silikon deliklerinden daha büyük ve daha düşük direnişle daha stabil bir güç transmisini sağlar. Ve yüksek bandwidth ve düşük latenci elde etmek için bir grup aracılığıyla. Bu yaklaşım temel çipinde gereken deliklerden silikon sayısını azaltır, aktif eleman için daha fazla alanı boşaltır ve çıplak çarşaf boyutunu iyileştirir.

On the other hand, TSMC is proposing a "3D multi-chip and system integrated chip" (SoIC) integration solution. Sistem-integral on-chip çözümü farklı boyutlarda, süreç teknolojilerinin ve materyallerin doğrudan birbirinin üstünde bilinen iyi çıplak kristallerini birleştirir.

TSMC, sistemin integral çiplerinin mikrobumpları kullanan geleneksel 3D integral devre çözümlerinden çok kez daha yüksek yumuşak yoğunluğu ve hızlığı vardır. Ayrıca, sistem integrasyonu çiplar paketlemeden önce iki ya da daha çıplak kristal bağlayan integrasyon çözümleri ön süreç sürecidir; Sonuç olarak sistem integrasyon çipsi şirketin InFO ya da CoWoS'in geri dönüş gelişmiş paketleme teknolojisini diğer çipleri daha fazla integre etmek için, güçlü bir "3D*3D" sistem seviyesi çözümü oluşturabilir.

Ayrıca TSMC 3DFabric'i başlattı. Bu da hızlı arttığı 3DIC sistemi integrasyon çözümlerini daha fazla fleksibilitçe sağlayacak ve güçlü sistemler yaratmak için güçlü çip bağlantısıyla birleştiriyor. 3 DFabric müşterilerin çoklu mantıklı çipleri birlikte, hatta tandem yüksek frekans geniş hafıza (HBM) veya analog, INPUT/çıkış ve rf modulları gibi heterogenel küçük çipleri ile birlikte bağlanmasına yardım eder. 3DFabric 3 boyutlu ve ön 3D çözümleri birleştirir ve sistem performansını ve fonksiyonluluğunu sürekli geliştirmek için transistor miniyeterlerini uygular, büyüklüğü ve görünümü azaltır ve ürün zamanını pazara hızlandırır.

2.5D ve 3D'den sonra Chiplets yarı yönetici endüstrisine çarpmak için en gelişmiş paketleme teknolojisinden biridir. Sonunda Chiplets'in özelliklerinin ve faydalarının kısa bir tasvir.

Chiplets kullanmak için üç faydası var. Çünkü gelişmiş süreç maliyeti çok yüksektir, özellikle analog devre ve ben/O süreç teknolojisi ile küçük olmak için daha zorlaşıyor. Chips devreleri bağımsız küçük çiplere bölüyor, fonksiyonlarını, süreç teknolojilerini ve boyutlarını güçlendirir ve sonunda onları birlikte birleştir ki süreç küçük çiplerinin çözümünü üstlenmek için. Ayrıca Chiplets de geliştirme ve doğrulama maliyetlerini azaltmak için mevcut olgun çipleri kullanabilir.

Şu anda çoğu yarı yönetici üreticileri çips şeklinde yüksek performans ürünlerini tanıttı. Örneğin, Intel's Intel Stratix 10 GX 10m FPGA, daha yüksek komponent yoğunluğunu ve kapasitesini ulaştırmak için çiplarla tasarlanmış. Mevcut Intel Stratix 10 FPGA mimarına ve Intel'in gelişmiş çoklu çip bağlantı teknolojisine dayanılan, ürün emib teknolojisini kullanır, iki yüksek yoğunlukta Intel Stratix 10 GX FPGA çekirdek lojik çipleri ve I / O birimleri ile ilişkilendirmek için kullanır. Aynı şey AMD'nin ikinci nesil epyc seri işlemcileri için doğru. Hafıza ve I/O'nun 14 nm CPU oluşturması için ilk nesilden farklı, ikinci nesil I/O'yu ve hafızayı bir çip haline ayırmak ve 7 nm CPU'yu 8 çip haline ayırmak.

Bir kelime içinde, geçmişte, çip etkisizliği yarı yönetici sürecinin geliştirmesi tarafından geliştirildi, fakat komponent boyutu fiziksel sınıra yaklaştığında, çip miniaturasyonu daha da zorlaştı. Küçük boyutlu ve yüksek etkileşimli çip tasarımını korumak için yarı yönetici endüstri sadece gelişmiş süreçler geliştirmeye devam etmedi, ama aynı zamanda çip tasarımını orijinal tek katından geliştirmek için, çoklu katı takımına dönün. Bu nedenle gelişmiş paketleme de Moore'un kanunu geliştirmek için önemli s ürücülerden biri oldu, yarı yönetici endüstrisinin trenini yönetmek için.

Gelecek zeki laboratuvarının ana çalışması: AI istihbarat sistemi IQ değerlendirme sistemi oluşturma ve dünya AI IQ değerlendirmesi; İnternet (şehir) bulut beyin araştırmaları plan ını yapın, İnternet (şehir) bulut beyin teknolojisini ve şirket haritasını inşa edin ve şirketler, endüstri ve şehirlerin istihbarat seviyesini geliştirmek için hizmet edin.