Fabricante de sustratos de encapsulamiento ic: lista de tecnologías de encapsulamiento de chips

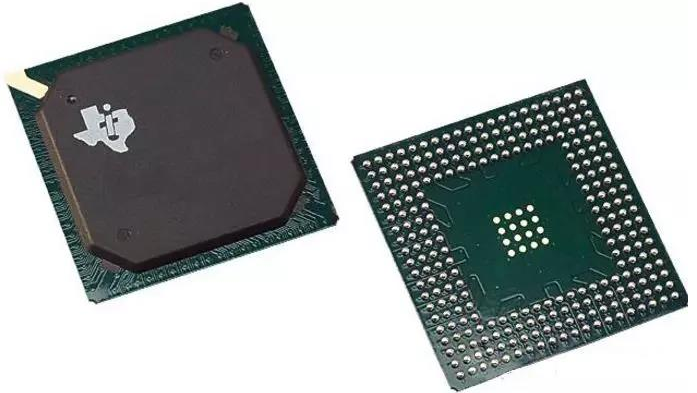

1. bga Ball grid array

También conocido como CPAC (global Top PAD Array carrier). Pantalla de contacto esférico, uno de los envases de montaje de superficie. La parte posterior del PCB IC produce protuberancias esféricas en forma de pantalla para reemplazar el pin. El chip LSI se ensambla en la parte delantera del PCB y luego presiona el modelo en resina natural o se sella mediante vertido. También se llama soporte de visualización de punto de partida convexo (pac). Tiene más de 200 Pines y es un encapsulamiento para el LSI de varios pines. El cuerpo del encapsulamiento también se puede hacer en un tamaño más pequeño que qfps (encapsulamiento plano de cuatro pines). Por ejemplo, el bga de 360 Pines con una distancia entre el núcleo de 1,5 mm es de solo 31 mm cuadrados; El qfps del 304 pin con una distancia entre el núcleo del pin de 0,5 mm es de 40 mm cuadrados. Bga no tiene que preocuparse por variantes de pin similares a qfps.

El paquete, desarrollado por la compañía estadounidense motorola, fue descubierto inicialmente para dispositivos como teléfonos portátiles y pronto se popularizó en computadoras personales. Inicialmente, la distancia entre los núcleos de los pines (protuberancias) de bga era de 1,5 mm, y el número de pines era de 225. Ahora también hay algunos fabricantes de LSI que están desarrollando bga de 500 pines. El problema de bga es la inspección visual después de la soldadura de retorno. La compañía estadounidense de motocicletas ola presionó el modelo en un embalaje sellado con resina natural llamado MPAC y lo llamó GPAC por su método de sellado.

2.C. (cerámica)

Una marca utilizada para representar el encapsulamiento de la porcelana. Por ejemplo, cdip representa DIP cerámica. Este es un símbolo que se utiliza a menudo en la práctica.

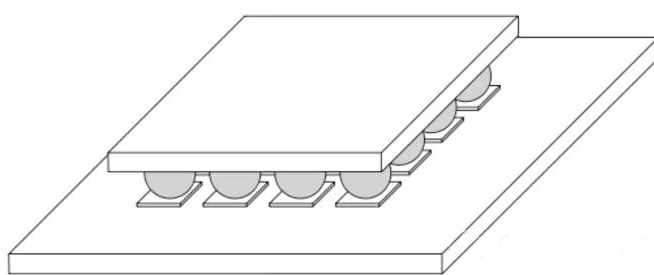

3. cob (chip a bordo)

Chip en el tablero

El encapsulamiento de chips en el tablero es una de las tecnologías de instalación de chips desnudos. El Chip Semiconductor se adhiere a la placa de circuito impreso, y la conexión eléctrica del chip con el sustrato se realiza con éxito a través del método de costura de alambre, y la fiabilidad se cubre con resina natural. Aunque el cob es la tecnología de instalación de hojas desnudas más simple, su densidad de encapsulamiento es mucho menor que la de Tab y la tecnología de soldadura inversa.

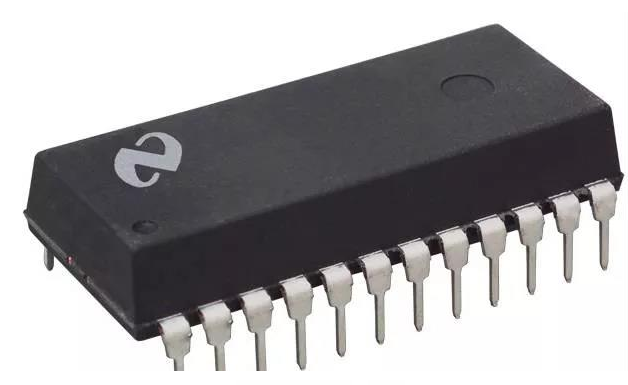

4. DIP (encapsulamiento en línea de doble línea)

Encapsulamiento en línea de doble línea. Los pines se sacan de ambos lados del paquete. Los materiales de embalaje son plásticos compuestos moleculares y cerámica. El fabricante de semiconductores Europa utiliza dil. DIP es el encapsulamiento plug - in más popular para aplicaciones como IC de pensamiento estándar, LSI de almacenamiento, circuitos de señalización, etc. la distancia entre los núcleos de PIN es de 2,54 mm y el número de PIN es de 6 a 64. El ancho del encapsulamiento suele ser de 15,2 mm. algunos encapsulamientos de 7,52 mm y 10,16 mm de ancho se llaman SK - DIP (skinny Dual in - line package) y sl - DIP (slim Dual in - line package) de cuerpo estrecho dip. Pero la mayoría de las cosas se llaman colectivamente dip. Además, el DIP cerámico, que está herméticamente sellado con vidrio de bajo punto de fusión, también se llama cerdip.

4.1 TIC (encapsulamiento cerámico en línea de doble línea)

Otro nombre de DIP (encapsulado en vidrio) en la carcasa de cerámica.

4.2 cerdip:

Encapsulamiento en línea de cerámica de doble fila encapsulado en vidrio para circuitos eclram, DSP (procesador de señal digital). Cerdip con ventana de vidrio para EPROM de borrado ultravioleta y circuitos de señalización con EPROM en el interior, entre otros. distancia entre los núcleos de pin de 2,54 mm, números de pin de 8 a 42. En toyo, este encapsulamiento se expresa como DIP - G (g significa vidrio estrechamente cerrado).

4.3 sdip (encapsulamiento en línea de doble línea reducido)

Reducir dip. Un encapsulamiento en caja, el mismo que el dip, pero con una distancia del núcleo del Pin (1778 mm) inferior al DIP (2,54 mm)

Así se llama. El número de pines está entre 14 y 90. Hay dos tipos: cerámica y plástico compuesto molecular. También conocido como SH - DIP (encapsulamiento en línea de doble fila reducido)

5. pasar página

Soldadura inversa del chip. Una de las técnicas de encapsulamiento de chips desnudos en la que se fabrican protuberancias metálicas en el área de electrodos del chip LSI y luego se unen al área de electrodos del sustrato impreso mediante soldadura a presión. El tamaño del plano ocupado o la superficie del objeto encapsulado es básicamente el mismo que el tamaño del chip. Es el más pequeño y delgado de todas las tecnologías de encapsulamiento. Sin embargo, si el coeficiente de expansión térmica del sustrato no es el mismo que el del chip lsi, la reacción se producirá en la unión, por lo que la fiabilidad de la Unión se verá afectada. Esto se debe a que los chips LSI deben reforzarse con resina natural y utilizar el coeficiente de expansión térmica del material básico del sustrato.

6, FPS (encapsulamiento plano)

Embalaje plano. Uno de los envases instalados externamente. Qfps o SOP (ver qfps y sop). Los fabricantes locales de semiconductores usan este nombre porque lo consideran apropiado.

7, H (con disipador de calor)

Indica la marca con el disipador de calor. Por ejemplo, hsop representa un SOP con un disipador de calor.

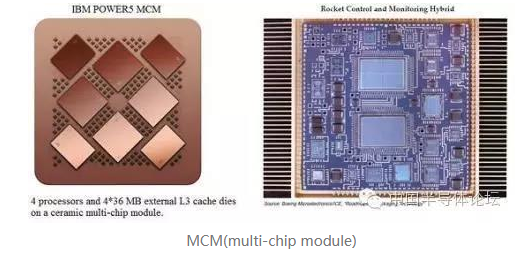

8. componentes multichip de MCM (módulo multichip)

9, P (plástico)

En los envases de plástico se indica el marcado de los compuestos moleculares. Por ejemplo, el plástico compuesto Molecular DIP expresado por pdip.

10. espalda de cerdito

El paquete ha sido cargado. Encapsulamiento cerámico, con enchufe, con formas similares a dip, qfps, qfn. Se utiliza para desarrollar instalaciones identificadas para reconocer claramente el funcionamiento de los procedimientos de reputación. Por ejemplo, inserte el EPROM en el enchufe para ajustarse. Este tipo de embalaje es básicamente un producto fijo, y el mercado no circula mucho.

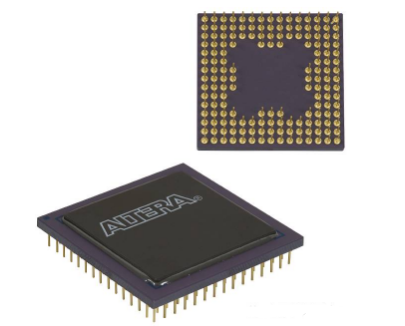

11. qpm (quad Flat package) encapsulamiento plano de cuatro lados de pin

Encapsulamiento plano cuadrilateral

Como encapsulamiento montado en el exterior, el pin se extrae de cuatro lados en forma de gaviota (l). Hay tres tipos de sustratos: cerámica, metal y plástico compuesto molecular. En términos de cantidad de envases de plástico, los compuestos moleculares representan la gran mayoría. Cuando el material no está especialmente expresado, en la mayoría de los casos es un plástico compuesto molecular qfps. El plástico compuesto molecular qfps es el paquete LSI de varios Pines más popular. No solo se utiliza en circuitos LSI de leyes de pensamiento digital como microprocesadores y pantallas de puerta, sino también en circuitos LSI analógicos como procesamiento de señales VTR y procesamiento de señales de audio. La distancia entre los núcleos de perno es de 1,0 mm, 0,8 mm, 0,65 mm, 0,5 mm, 0,4 mm, 0,3 mm y otras especificaciones. El número máximo de pines en la especificación de distancia del núcleo de 0,65 MM es de 304.

Algunos fabricantes de LSI se refieren específicamente a qfps con una distancia del núcleo del pin de 0,5 mm como qfps reducidos o qfps, vqfps. Pero algunos fabricantes juntan 0,65 mm y 0,4 mm de distancia Pin - core qfps (también conocido como qfps) para confundir un poco el nombre.

De acuerdo con los estándares jedec (comité de instalaciones electrónicas), el qfps adicional con una distancia entre el pin y el núcleo de 0,65 mm y un espesor del cuerpo principal de 3,8 mm a 2,0 mm se llama mqfps (encapsulamiento de cuatro planos métricos). Qfps de menos de 0,65 mm, como 55 mm, 0,4 mm y 0,3 mm, se llaman qfps (fps) (distancia fina qfps), y la distancia entre los núcleos pequeños es qfps. También se llama fqfps (encapsulamiento de cuatro planos de espaciamiento fino). Pero ahora la implementación de las especificaciones de forma qpm de la Asociación de la industria de maquinaria electrónica de Toyo tiene una nueva reputación. No hay diferencia en la distancia del núcleo del pin, pero se divide en tres tipos según el grosor del encapsulamiento: qfps (2,0 mm a 3,6 mm de espesor), lqfps (1,4 mm de espesor) y tqfps (1,0 mm de espesor).

La desventaja del qfps es que cuando la distancia del núcleo del perno es inferior a 0,65 mm, el perno se dobla fácilmente. para evitar la deformación del perno, han surgido varias variedades mejoradas de qfps. Por ejemplo, bqfps con un dedo de árbol en las cuatro esquinas del embalaje para aliviar la almohadilla de conflicto (véase 11.1); Gqfps utiliza resina natural y trata de cuidar los anillos que cubren la parte delantera de la comercialización; El tpqfps se puede probar colocando el punzón de prueba en el cuerpo del paquete y colocándolo en una pinza especial para evitar la deformación del pin. En términos de reglas de pensamiento lsi, muchos productos de I + D y productos de alta fiabilidad están encapsulados en qfps cerámicos multicapa. También se ofrecen productos con una distancia mínima del núcleo de 0,4 mm y un número máximo de pin de 348. Además, hay un qfps de cerámica encapsulada en vidrio (ver 11.9).

11.1 bqfps (encapsulamiento de cuatro planos con parachoques)

Bqfps

Nuestro embalaje plano de pin lateral y almohadilla de alivio de conflictos. En una de las encapsulaciones qfps, las cuatro esquinas del cuerpo encapsulado están equipadas con protuberancias (almohadillas de alivio de conflictos) para evitar que los pines se dobleguen durante el transporte. Los fabricantes estadounidenses de semiconductores utilizan adecuadamente este encapsulamiento principalmente en circuitos como microprocesadores y asic. La distancia del núcleo del PIN es de 0635 mm, y el número de pin varía de 84 a unos 196.

11.2 qic (encapsulamiento cerámico de cuatro líneas)

Otro nombre para la cerámica qfps. El nombre que el fabricante local de semiconductores considere adecuado.

11.3 qip (envases de plástico de cuatro líneas)

Otro nombre para el plástico compuesto molecular qfps. El nombre que el fabricante local de semiconductores considere adecuado.

11.4 pfpfpf (envases planos de plástico)

Embalaje plano de plástico compuesto molecular. Otro nombre para el plástico compuesto molecular qfps. El nombre que el fabricante local de LSI considere adecuado.

11.5 qfh (encapsulamiento alto de cuatro planos)

El fuselaje grueso de los cuatro lados está empaquetado plano. Un compuesto molecular del plástico qfps, que se hace más grueso para evitar la desconexión del cuerpo del embalaje. El nombre que el fabricante local de semiconductores considere adecuado.

11.6 cqfps (cuatro paquetes Fiat con anillos protectores)

Embalaje plano con perno de cuatro lados, con el mejor anillo de Cuidado. Plástico compuesto molecular qfps, uno de los pines utiliza resina natural, tratando de cuidar el blindaje del anillo y evitar la deformación de pandeo. Antes de ensamblar el LSI en el sustrato impreso, se corta el pin del mejor anillo de cuidado y se convierte en forma de alas de gaviota (en forma de l). Este embalaje se ha producido en masa en la empresa estadounidense de motocicletas ola. La distancia entre los núcleos de los pines es de 0,5 mm, y el número máximo de pines es de aproximadamente 208.

11,7 mquad (cuadrilátero metálico)

La compañía estadounidense Olin ha desarrollado un paquete qfps. El sustrato y la tapa se consideran adecuados y se utilizan aluminio, bien sellados con un adhesivo. En condiciones naturales de refrigeración por aire, la Potencia puede alcanzar 2,5w a 2,8w. Toyo New Light Power Industry Company obtuvo una concesión para producir en 1993

11,8 litros - cuatro cilindros

La cerámica es una de las qfps. Como sustrato de encapsulamiento, el nitruro de aluminio tiene una conductividad térmica de 7 a 8 veces mayor que el aluminio y el oxígeno, y tiene una mejor disipación de calor. El marco del encapsulamiento es alúmina, y el chip está herméticamente sellado a través del encapsulamiento, lo que limita los costos. Es un paquete de software desarrollado para la Ley del pensamiento LSI que permite el uso de la Potencia W3 en condiciones naturales de enfriamiento por aire. Se han desarrollado 208 Pines (0,5 mm de distancia entre núcleos) y 160 Pines (0,65 mm de distancia entre núcleos) de encapsulamiento LSI mindrule, y la producción en masa comenzó en octubre de 1993.

11.9 cerquad

Un embalaje exterior, es decir, bajo un qfps cerámico estrechamente cerrado, se utiliza para encapsular circuitos LSI que piensan en leyes como el dsp. El cerquad con Windows se utiliza para encapsular circuitos eprom. Su rendimiento de disipación de calor es mejor que el plástico compuesto molecular qfps, que puede permitir una potencia de 1,5 a 2w en condiciones naturales de refrigeración por aire. Pero el costo del embalaje es de 3 a 5 veces mayor que el del plástico compuesto molecular qfps. La distancia entre los núcleos de perno es de 1,27 mm, 0,8 mm, 0,65 mm, 0,5 mm 0,4 mm y otras especificaciones. El número de pines está entre 32 y 368.

12. qfg (quad Flat J - Leaded package) encapsulamiento plano de cuatro lados con pin j

Uno de los envases instalados externamente. El PIN sale de los cuatro lados del paquete en forma de J hacia abajo. Es el nombre prescrito por la Asociación de la industria de maquinaria electrónica de toyo. La distancia entre los núcleos de perno es de 1,27 mm. los materiales son plásticos compuestos moleculares y cerámica.

La mayoría de los plásticos compuestos moleculares qfj se llaman plcc (portadores de chips de alambre de plástico) y se utilizan en circuitos como señalización, visualización de puertas, dram, assp y otp. El número de pines va de 18 a 84.

El qfj cerámico también se llama clcc (portador de chip de alambre cerámico) y jlcc (portador de chip de alambre J - leaded). El encapsulamiento de la ventana se utiliza para EPROM de borrado ultravioleta y circuitos de chip de logotipo con eprom. El número de pines oscila entre 32 y 84.

13.qfn (encapsulamiento sin alambre de cuatro planos)

El encapsulamiento plano sin pin de cuatro lados es un encapsulamiento de montaje externo para encapsulamiento IC de alta velocidad y alta frecuencia. Ahora se llama comúnmente lcc. Qfn es el nombre prescrito por la Asociación de la industria de maquinaria electrónica de toyo. Los cuatro lados del paquete están equipados con contactos de electrodos, ya que no hay pin, por lo que el tamaño del soporte ocupa la superficie del plano u objeto, es más pequeño que el tamaño del qfps y la altura es inferior a la del qfps. Sin embargo, cuando la tensión inicial entre el sustrato impreso y el paquete no se puede liberar en el contacto del electrodo. Debido a que este contacto de electrodos no es tan fácil como los pines qfps, generalmente de unos 14 a 100.

Hay dos tipos de materiales: cerámica y plástico compuesto molecular. Cuando está marcado con lcc, es en su mayoría cerámica qfn. La distancia entre los núcleos de los contactos de los electrodos es de 1,27 mm. el plástico compuesto molecular qfn es un paquete de sustrato de impresión de vidrio - Gas Epóxido - resina natural de bajo costo. Además de la distancia entre los núcleos de los contactos de los Electrodos de 1,27 mm, hay dos tipos: 0,65 mm y 0,5 mm. este encapsulamiento también se conoce como plástico compuesto molecular lcc, pclc, P - lcc, etc.

13.1 pclp (encapsulamiento sin alambre de placa de circuito impreso)

La placa de circuito impreso está encapsulada sin alambre. Toyo Fujitsu considera que el plástico compuesto molecular qfn (plástico compuesto molecular lcc) es el nombre de uso adecuado. La distancia del núcleo del perno tiene dos especificaciones: 0,55 mm y 0,4 mm. Hasta ahora se encuentra en fase de desarrollo.

13.2 P - LCC (portador de chips sin desgarro de plástico) (biblioteca de chips de alambre de plástico)

A veces plástico compuesto molecular qfj, a veces qfn (plástico compuesto molecular lcc) (ver qfj y qfn). Los fabricantes locales de LSI utilizan plcc para representar encapsulamientos con cables y P - LCC para representar encapsulamientos sin cables para mostrar diferencias.

14. qfi (quad Flat I - Leaded packgage) encapsulamiento plano de cuatro lados de I Pin

Uno de los envases instalados externamente. El broche se dibuja desde los cuatro lados del paquete y se dibuja hacia abajo hasta la palabra I. También se llama MSP (mini embalaje cuadrado). Colocación e impresión de sustratos para soldadura conjunta. Debido a que el pin no tiene parte de la punta, el tamaño de la base que ocupa el plano o la superficie del objeto es menor que el qfps. Hitachi Production ha desarrollado y utilizado este encapsulamiento para IC de simulación de archivos de vídeo. Además, el pll IC de Toyo Motorola también se considera adecuado para usar este encapsulamiento. La distancia entre los núcleos de los pines es de 1,27 mm, y los números de los pines son de 18 a 68.

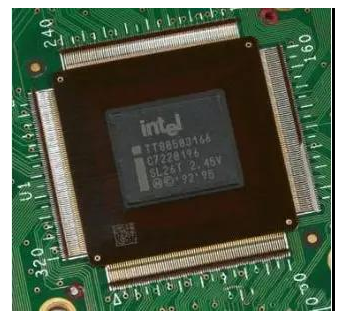

15. tecnología TCP encapsulada por película TCP (tape Carrier pack)

TCP

Se utiliza principalmente para Intel Mobile Pentium mmx. Las CPU encapsuladas adecuadamente con TCP tienen mucho menos calor que las CPU ordinarias de matriz de pin pga, que se pueden utilizar en computadoras portátiles para reducir el tamaño de los radiadores adicionales y mejorar la utilización del espacio del host, algo más común en unos pocos supercomputadoras. Pero debido a que el encapsulamiento TCP solda la CPU directamente a la placa base, porque el usuario promedio no es fácil de reemplazar.

15.1 DTCP (encapsulamiento de doble banda)

Doble pin con paquete de carga. Uno de los TCP (con encapsulamiento de carga). Los pines se fabrican en cintas aislantes y se sacan de ambos lados del paquete. Debido a la tecnología Tab (soldadura semiautomática de carga), el embalaje es muy delgado. Suele usarse para impulsar el LSI a través de la exposición lcd, pero la mayoría son productos personalizados.

Además, se está desarrollando un paquete de libros LSI de 0,5 mm de espesor para el almacenamiento. En toyo, según el estándar eiaj (toyo Electronic Machinery industry), DTCP se llama dtp.

15.2 qtcp (encapsulamiento con cuatro bandas)

Pin de cuatro lados con paquete de carga. Uno de los encapsulamientos TCP que forma un pin en la Cinta aislante y se retira de los cuatro lados del encapsulamiento. Es un embalaje delgado con tecnología tab. En toyo, se llama Qud tape Carrier package.

15.3 tecnología de unión semiautomática de cinta adhesiva automática (tab)

El enlace semiautomático de cinta adhesiva (tab) es un chip de circuito integrado a gran escala (ic) con múltiples pines de conexión que ya no utiliza encapsulamientos tradicionales para convertirse en un individuo completo, sino que utiliza un soporte Tab y pega el chip sin sellar directamente a la superficie de la placa. El uso de una cinta suave de "poliimida" y un pin interno y externo grabado en lámina de cobre como soporte hace que el chip grande se adhiera primero al pin interno. Después de la prueba semiautomática, el montaje se completa uniendo la placa de circuito al "pin externo". Un nuevo método de construcción para este embalaje y montaje, el método tab.

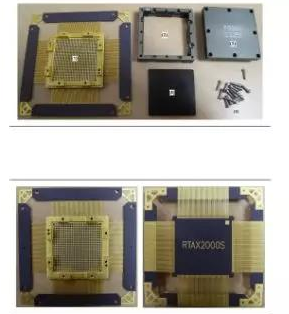

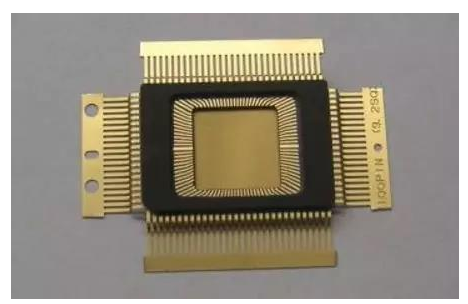

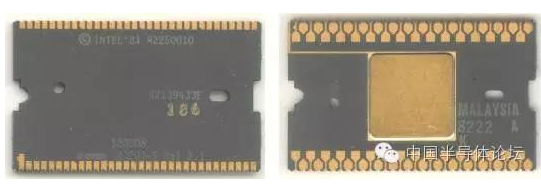

16. PGA (matriz de rejillas de agujas)

PGA

Muestra el paquete de pin. Uno de los encapsulamientos de la Caja en el que la venta directa en la parte inferior muestra la disposición del patrón. Los sustratos encapsulados se consideran generalmente adecuados y se utilizan sustratos cerámicos multicapa. Cuando el nombre del material no está especificado, la mayoría son PGA cerámicos, que se utilizan en circuitos LSI de leyes de pensamiento a gran escala de alta velocidad. El costo es muy alto. La distancia entre los núcleos de los pines es generalmente de 2,54 mm, la longitud de los pines es de aproximadamente 3,4 mm, y el número de pines varía de 64 a aproximadamente 447. Para reducir costos, el sustrato de impresión de resina natural de gas Epóxido de vidrio se puede reemplazar por el sustrato de embalaje.

El plástico PGA también tiene un compuesto molecular de 64 a 256 pines. además, hay una distancia de núcleo de 1,27 mm y un PGA de montaje de superficie de pin corto de 1,5 mm a 2,0 mm de longitud de pin (pga de soldadura al tacto), la mitad más pequeña que el PGA enchufable, por lo que el encapsulamiento no se puede hacer mucho y el número de pines es mayor que el enchufable (250 a 528).

17. lga (matriz de redes terrestres)

Lga

Paquete de exhibición de contactos. Es decir, hacer un paquete con una matriz de contactos de electrodos de ranura en el lado inferior. Solo hay que insertarlo en el enchufe para ensamblarlo. El lga cerámico con 227 contactos (distancia entre núcleos de 1,27 mm) y 447 contactos (distancia entre núcleos de 2,54 mm) se ha aplicado a los circuitos LSI de reglas de pensamiento de alta velocidad. En comparación con qfps, lga puede acomodar más pines de entrada y salida en paquetes más pequeños. Además, el cable es adecuado para el LSI de alta velocidad debido a su baja resistencia.

18. encapsulamiento de cables en el chip

Tecnología de encapsulamiento lsi, una estructura que coloca la parte delantera del marco de alambre por encima del chip, crea puntos de soldadura convexos cerca del núcleo del CHIP y sutura el alambre para la programación colaborativa eléctrica. En el mismo volumen de encapsulamiento, el ancho del chip puede ser de aproximadamente 1 mm en comparación con la estructura original en la que el marco de alambre se coloca cerca del lado del chip.

19. prueba (traje de cuatro líneas)

Quad - in line es un encapsulamiento en línea de cuatro Pines llamado quill. Los pines salen de ambos lados del paquete y se doblan hacia abajo en cuatro filas a intervalos cruzados. La distancia del núcleo del PIN es de 1,27 mm, y cuando se inserta el sustrato impreso, la distancia del núcleo se convierte en 2,5 mm. porque esto se aplica a las placas de circuito impreso estándar. Es un encapsulamiento más pequeño que el DIP estándar. Toyo Electric ha utilizado algunos encapsulamientos adecuados en los chips de logotipo de sus productos de escritorio y electrodomésticos. Hay dos tipos de materiales: cerámica y plástico compuesto molecular. Número de pin 64.

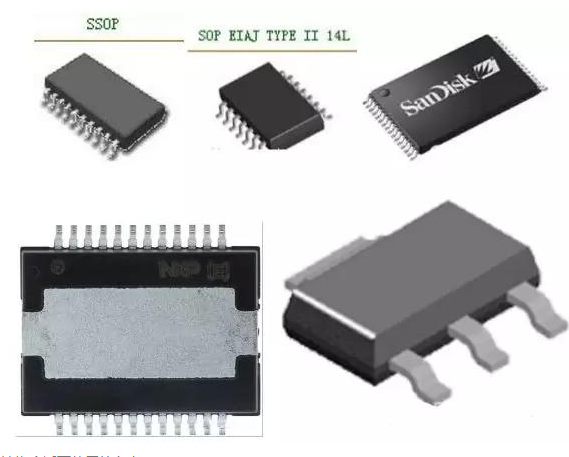

20. SOP (embalaje exterior de pequeñas líneas de producción)

Envases pequeños. Como embalaje montado en el exterior, los pines se sacan de ambos lados del embalaje en forma de alas de gaviota (en forma de l). Los materiales son plásticos compuestos moleculares y cerámica. También conocido como sol (small out Line l Leaded package), DFP (dual Flat package), soic (small out Line Integrated circuit), dso (dual small) out lint), este nombre es utilizado por muchos fabricantes de semiconductores extranjeros.

SOP no solo se aplica a la memoria lsi, sino que también es ampliamente utilizado en pequeños circuitos assp. El SOP es el encapsulamiento de montaje de superficie más popular en áreas en las que los terminales de entrada y salida no superan los 10 a 40. El núcleo del pin está a 1,27 mm de distancia y el número del PIN es de 8 a 44.

A medida que avanza el sop, se entrega gradualmente:

Ssop con una distancia de núcleo de aguja inferior a 1,27 mm (de SOP grande a SOP pequeño);

La altura de montaje es inferior a 1,27 mm tsop (embalaje pequeño delgado);

Vsop (embalaje ultrapequeño); Tssop (thin from big to Small sop);

Sot (transistor de Unión pequeña); El SOP con disipador de calor se llama hsop;

Los fabricantes locales de semiconductores se refieren a SOP como fin sonf sin disipador de calor (pequeñas aletas no disipadoras de calor);

El fabricante local dice que el SOP de cuerpo ancho (tipo J ancho) Sow

21. MFP (mini paquete plano) pequeño paquete plano

Alias SOP o ssop de plástico compuesto molecular. El nombre que el fabricante local de semiconductores considere adecuado.

22. SIMM (módulo de memoria de una sola columna)

Componentes de almacenamiento de una sola línea. Componentes de almacenamiento equipados con electrodos solo cerca de un lado del sustrato impreso. Generalmente se refiere a los componentes que se insertan en el enchufe. El SIMM estándar tiene un electrodo de 30 electrodos con una distancia entre núcleos de 2,54 mm y 72 electrodos con una distancia entre núcleos de 1,27 mm. el SIMM encapsulado en soj de 1 y 4 megabytes DRAM en uno o ambos lados del sustrato impreso se ha utilizado ampliamente en computadoras privadas, estaciones de oficinas y otras instalaciones. Al menos entre el 30% y el 40% de las DRAM se ensamblan en simm.

23, DIMM (módulo de memoria en línea de doble línea

Es muy similar al simm, pero los dedos de oro del DIMM no se comunican entre sí en ambos extremos como el simm. Por el contrario, los dedos de oro de DIMM se comunican de forma independiente entre sí en ambos extremos, ya que esto puede satisfacer las necesidades de transmisión de una gran cantidad de señales de datos. Asimismo, se considera que la idoneidad y el uso del dimm, la interfaz SDRAM y la interfaz de memoria DDR son ligeramente diferentes, el DIMM SDRAM es una estructura DIMM de 168pin, el dedo de oro es de 84pin por lado y el dedo de oro tiene dos tarjetas para evitar la inserción en la ranura, la memoria no se inserta correctamente en la dirección opuesta y causa daños en la quema; DDR DIMM cree que es apropiado usar la estructura DIMM de 184pin, con 92pin a ambos lados del dedo dorado y solo una bayoneta en la cabeza del dedo dorado. El número de bayonetas es diferente y es la diferencia más superficial entre los dos.

DDR2 DIMM es una estructura DIMM de 240 pin, con 120pin a ambos lados del dedo dorado. Al igual que el DIMM ddr, solo hay una tarjeta en la cabeza del dedo dorado, pero la posición de la tarjeta es ligeramente diferente a la del DIMM ddr, porque la memoria DDR no se puede insertar en el DIMM ddr. La memoria DDR no se puede insertar en el DIMM DDR porque la placa base con DIMM DDR y DIMM DDR no mostrará el problema de que la Memoria se inserta en la ranura equivocada.

24, sip (encapsulamiento de una sola línea)

Encapsulamiento en línea única. La mayoría de los fabricantes europeos de semiconductores utilizan el nombre SIL (línea única) cuando lo consideran apropiado. Los pines se dibujan desde un lado del paquete y se colocan en una línea recta. Cuando se ensambla en un sustrato impreso, el paquete se encuentra en una posición transversal. La distancia entre los núcleos de los pines es generalmente de 2,54 mm, y el número de pines varía de 2 a 23, la mayoría de los cuales son productos personalizados. Los estilos de embalaje son diferentes. Algunas personas también se refieren al mismo estilo que los paquetes zip como sip.

25. SMd (dispositivos de montaje de superficie)

Chip SMd

Apariencia para instalar piezas. A veces, algunos fabricantes de semiconductores clasifican SOP como smd.

26. soi (encapsulamiento de pequeños cables I salientes)

Clavo pequeños envases. Uno de los envases instalados externamente. Los pines salen de ambos lados del paquete, en forma de I hacia abajo, con una distancia de núcleo de 1,27 mm. el soporte ocupa el plano o la superficie de un objeto más pequeño que el sop. Hitachi utilizó el paquete en la imitación del IC (ic de robo impulsado por motores). Número de pin 26.

27. soj (encapsulamiento de pequeños cables J salientes)

Embalaje pequeño de aguja J. Uno de los envases instalados externamente. Los pines tienen forma de J hacia abajo desde ambos lados del paquete, por lo que reciben su nombre. Suele estar hecho de plástico molecular y se utiliza principalmente en circuitos LSI de memoria como DRAM y sram, pero principalmente en dram. Muchos de los componentes DRAM encapsulados en soj se ensamblan en simm. La distancia entre los núcleos de los pines es de 1,27 mm, y el número de pines está entre 20 y 40 (ver simm).

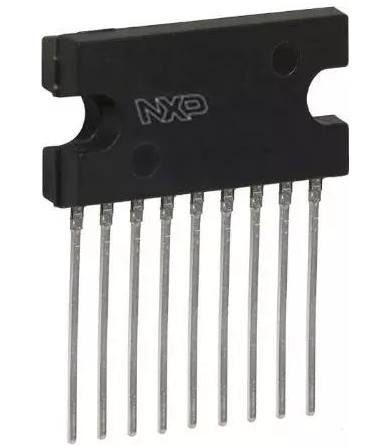

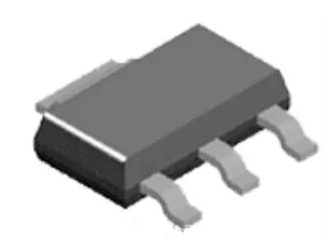

28, al embalaje hasta

To packageto

Su chasis es una placa metálica redonda y luego se calienta con un pequeño trozo de vidrio. después de que el vidrio se derrite, el alambre se fija en el agujero. el agujero y el alambre se combinan en el asiento de la cabeza, por lo que primero se dorada la cabeza en el asiento de la cabeza. debido a que la parte inferior de la placa de circuito integrado está dorada, se puede soldar con cera de soldadura de oro y germanio. Al soldar, precaliente el asiento de la cabeza para que la cera de soldadura colocada allí se derrita definitivamente, y luego coloque la placa de circuito sobre la cera de soldadura, enfriando para formar una buena unión entre los dos.