Definición y función del sustrato Circuito integrado

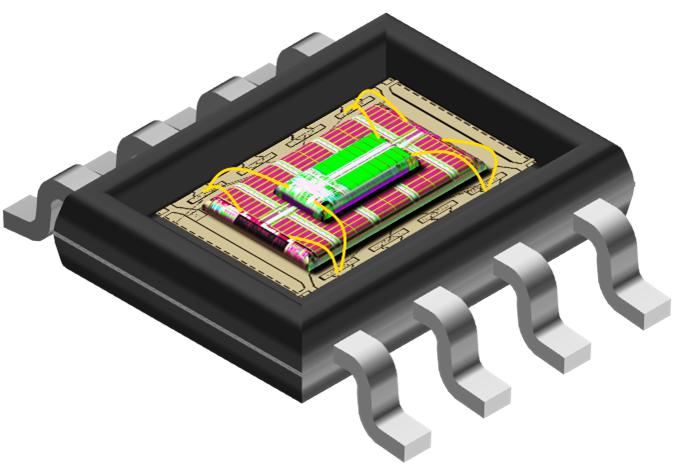

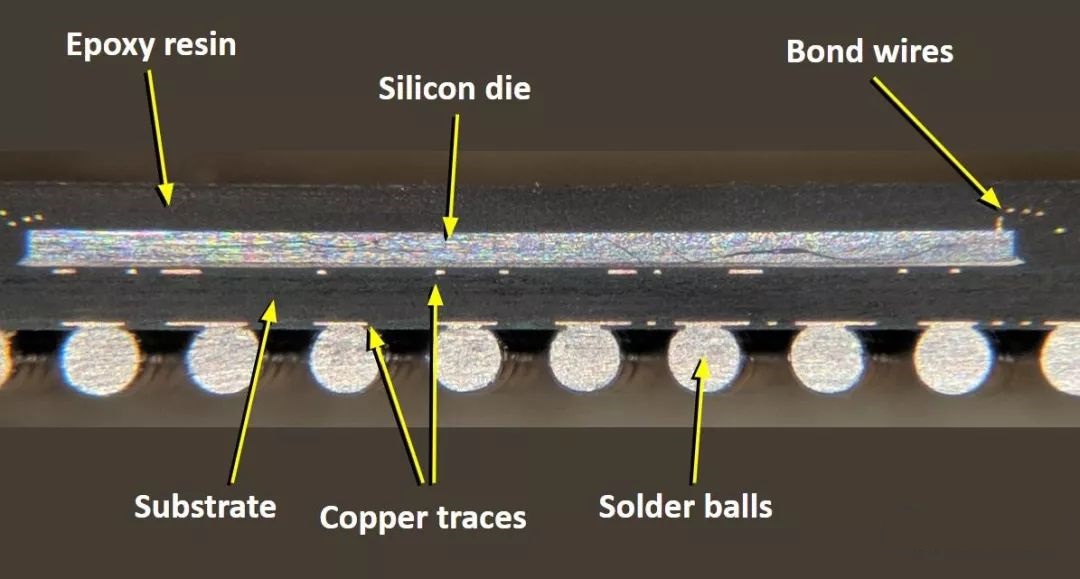

Sustrato de circuito integradoDefinición: sustrato utilizado para encapsular Patatas fritas Circuito integrado desnudos.

Función:

(1) Carrying semiconductor Circuito integrado Patatas fritass.

(2) The internal circuit is arranged for the connection between the chip and the circuit Tabla.

(3) Protect, Reparación, Apoyo Circuito integrado chip, Proporcionar canales de disipación de calor, Chip de comunicación y Placa de circuito impreso.

Embalaje de circuitos integrados

Nacimiento: a mediados de la década de 1990, menos de 20 años. La aparición de nuevas formas de embalaje de alta densidad para circuitos integrados (Circuito integrado), como bga (Ball Gate Array Packaging) y CSP (chip size Packaging), ha dado lugar a un nuevo portador necesario para el embalaje, el sustrato de embalaje Circuito integrado.

* Semiconductor development: valve - Transistor - Through Agujero assembly - surface Packaging (SMT) - Chip level Packaging (CSP, Bga) - System Packaging (SIP)

* Placa de circuito impreso Y la tecnología de semiconductores son interdependientes, Cerrar, Penetración, Coordinación estrecha, Placa de circuito impreso Puede realizar una variedad de chips, Componentes entre aislamiento eléctrico y conexión eléctrica, Proporcionar las características eléctricas necesarias.

Número de capas de parámetros técnicos: 2 ~ 10 capas;

Placa de circuito impreso Espesor de la placa, Normalmente 0.1 ~ 1.5.mm;

Minimum Placa de circuito impreso Tabla thickness tolerance *0 micron;

Minimum aperture, A través del agujero 0.1 mm, Microporosidad 0.03mm;

* Minimum pattern width/Espaciamiento, 10~80 microns;

Minimum ring width, 50 microns;

* Contour tolerance, 0~50 micron;

* Buried blind hole, Impedancia, buried resistance capacity;

* Surface coating, Níquel/Australia, Oro blando, Oro duro, Níquel/Paladio/Oro, Etc..

* Board size, â¤150*50mm (single Circuito integrado carrier);

That is to say, Este Sustrato de circuito integrado Esto requiere más multas, Alta densidad, Número de pies altos, Pequeña capacidad, hole, Disco, Líneas más pequeñas, Núcleo ultrafino. Por consiguiente,, Se requiere una técnica precisa de alineación interlaminar, Técnica de imagen modal, Tecnología de galvanoplastia, Tecnología de perforación y tratamiento de superficie. Mayor demanda de fiabilidad del producto, Equipo e instrumentos, Gestión de materiales y producción. Por consiguiente,, Umbral técnico Sustrato de circuito integrado Alto, R & D no es fácil.

Dificultades técnicas en comparación con la tecnología tradicional Placa de circuito impreso Industria manufacturera, Dificultades técnicas que deben superarse Sustrato de circuito integrado are as follows:

(1) core Tabla production technology core Tabla Delgado, Deformable, Especialmente si el espesor de la placa es 0.2 mm, Estructura laminar, Expansión y contracción de la placa, Parámetros laminares, El sistema de posicionamiento interlaminar y otras tecnologías necesitan un avance, Por lo tanto, el control efectivo de la deformación y el espesor de prensado del núcleo ultrafino se puede realizar..

(2) Microporous technology

* Including: solder mask open process, Tecnología de perforación láser de micro - agujeros ciegos, Proceso de llenado de cobre en agujero ciego.

* Conformalmask (Conformalmask) process is used to make reasonable compensation for laser blind hole window opening, El diámetro y la posición del agujero ciego se determinan directamente a través del anillo de cobre abierto..

* Indicators involved in laser drilling microhole: hole shape, Relación de apertura superior e inferior, Erosión lateral, Proyección de fibra de vidrio, Pegamento residual en el Fondo del agujero, Etc..

* Indicators involved in blind hole copper plating include: filling capacity, Cavidad del agujero ciego, Droop, Fiabilidad del recubrimiento de cobre, Etc..

* At present, El tamaño de los microporos es de 50 ~ 100 μm, El número de poros en capas es de hasta 3, 4. y 5 pedidos.

(3) Graphic formation and copper plating technology

Pattern compensation technology and control; Fine pattern production technology; Copper plating thickness uniformity control technology; Micro erosion control technology for fine pattern.

* The current pattern width spacing requirement is 20~50 microns. Copper plating thickness uniformity requirement is 18* micron, Uniformidad del grabado - 90%.

(4) welding resistance process * including plug hole process, Tecnología de impresión de resistencia a la soldadura, Etc..

* The height difference between the solder resistance surface of the Sustrato de circuito integrado Menos de 10 micrones, Y la diferencia de altura entre la resistencia de soldadura y la superficie de la almohadilla es inferior a 15 micrones..

(5) Surface treatment technology

* Uniformity of thickness of Níquel/Chapado en oro; El proceso de recubrimiento de oro suave y duro se lleva a cabo en la misma placa. Níquel/Paladio/Proceso de chapado en oro.

* Lineable surface coating, Tratamiento selectivo de la superficie.

(6) Testing capability and product reliability testing technology

* Equipped with a number of testing equipment/Un instrumento diferente de un instrumento tradicional. Placa de circuito impreso Fábrica.

* Master reliability testing techniques different from conventional ones.

(7) In general, Producción Sustrato de circuito integrado involving more than ten aspects of technology:

Graph dynamic compensation; Graphic electroplating process for thickness uniformity of copper plating; The whole process material expansion and shrinkage control; Surface treatment process, Galvanoplastia selectiva de oro blando y duro, nickel/Paladio/gold plating process;

* Core plate wafer production;

* High reliability detection technology; Microporous processing;

* If stacked micro 3, 4, 5, production process;

* Multiple laminated pressure; Laminate â¥4 times; Drilling â¥5 times; Electroplating â¥5 times.

* Wire pattern formation and etching;

* High precision alignment system;

* Welding stopper hole process, Proceso de llenado de microporos por galvanoplastia;

Sustrato de circuito integradoClasificación

En forma de encapsulación

Tendencias del embalaje

(1) BGA

*BallGridAiry, BGA, Paquete de matriz esférica.

* This kind of Paquete of the Tabla Disipación de calor, Buen rendimiento eléctrico, El PIN del chip se puede aumentar en gran medida, applied to 300 pin number (pincount) above Circuito integrado package.

(2) CSP

*CSP, Embalaje a nivel de chip, Paquete de tamaño a nivel de chip.

* Is a single Paquete de chips, Peso ligero, Pequeño, Su tamaño de embalaje y Circuito integrado Casi del mismo tamaño o ligeramente mayor, Para productos de memoria, Productos de comunicación, El Código pin de los productos electrónicos no es alto.

(3) coated Placa de circuito impreso de cristal

* FlipChip (FC) is a type of package in which the front side of the chip is flipped (Flip) and the convex block is directly connected A Placa de circuito impreso.

Este tipo de sustrato tiene la ventaja de baja interferencia de señal, Baja pérdida de conexión, Buen rendimiento eléctrico, Disipación de calor de alta eficiencia, etc..

(4) Multi-chip module

* Multi-chip (MCM) module Multiple chips with different functions in the same package.

* This is the best solution for electronic products to light, thin, Corto, Radio de baja velocidad. Para computadoras grandes de alto orden o productos electrónicos de rendimiento especial.

* Because there are multiple chips in the same package, Interferencia de la señal, heat dissipation, Diseño de líneas finas, Espera un minuto., No hay una solución más completa, Desarrollo activo de productos.

Según las propiedades del material s

(1) Hard Placa de circuito impreso board. Carga de sellado Placa de circuito impreso

* Rigid organic Sustrato de embalaje made of epoxy, British Telecom, Resina ABF. Los principales valores de salida son: Circuito integrado packaging substrate. CTE (coefficient of thermal expansion) ranges from 13 to 17ppm/ Celsius.

La placa blanda está sellada y cargada con Placa de circuito impreso.

* The packaging substrate made of PI (polyimide), PE (polyester) resin flexible substrate, Cte 13 ~ 27 PPM/ Celsius.

(3) Ceramic substrate

* Aluminum oxide, Nitruro de aluminio, Carburo de silicio y otros materiales cerámicos como sustrato de embalaje. Cte es pequeño, 6 ~ 8 PPM/ Celsius.

Características de la tecnología de conexión

(1) Play pattern to engage the carrier plate

* The gold wire connects the Circuito integrado to the Placa de circuito impreso Board.

(2) TAB Placa de circuito impreso

*TAB -- TapeAutomatedBonding

* The inner pins of the chip are connected with the chip, Pin externo conectado a la placa de embalaje.

Cubra el tablero de Placa de circuito impreso unido al cristal.

*Filpchip, La oblea es una proyección de filp y está conectada directamente a Placa de circuito impreso Board.