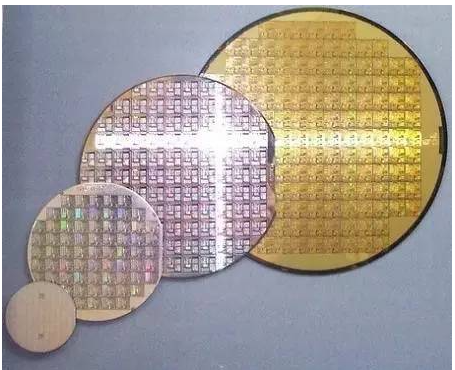

Il cartone di imballaggio IC si riferisce al processo di elaborazione del wafer misurato secondo il modello del prodotto e i requisiti di funzione per ottenere chip indipendenti. I pacchetti IC forniscono principalmente un mezzo per collegare chip di silicio fini a circuiti stampati ampiamente distanziati e proteggere i dispositivi dall'umidità.

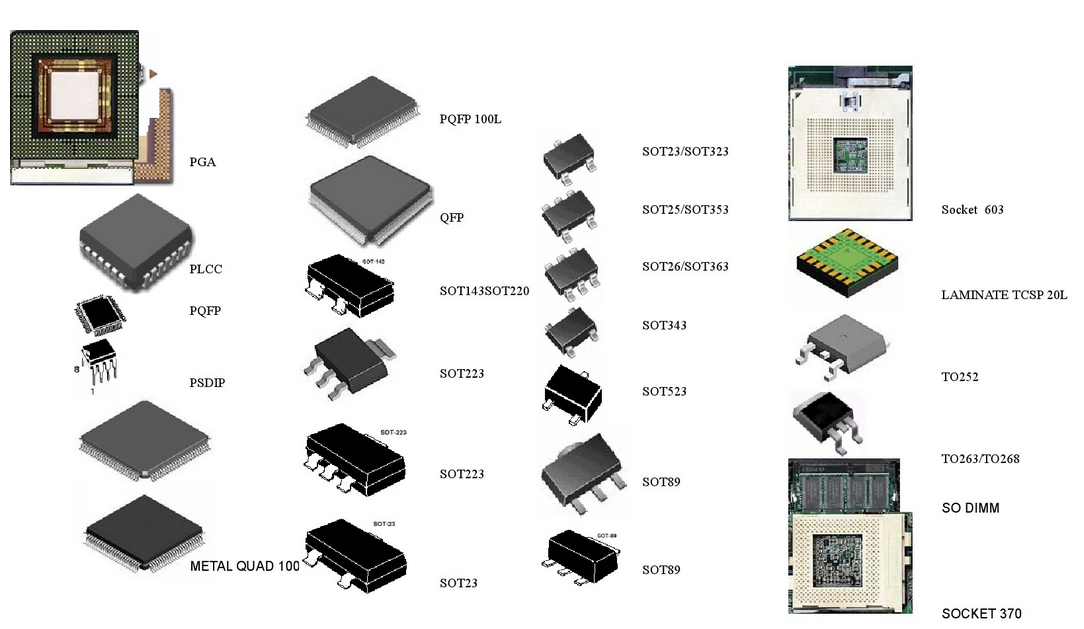

I moduli di imballaggio specifici comprendono:

modulo di imballaggio

Pacchetto piombo

Alla fine degli anni '70, il primo pacchetto ampiamente accettato sul mercato fu il dual-in-line (DIP), un pacchetto in ceramica e plastica. I cavi sono disegnati da entrambi i lati della confezione e sono perpendicolari alla confezione. Il pacchetto può essere montato sul PCB inserendo il perno nel foro passante nella scheda, quindi tagliando il piombo dall'altro lato della scheda e saldandolo utilizzando la tecnologia di saldatura ad onda. Il pacchetto può ospitare un numero massimo di cavi di 40 e una spaziatura della piastra di 0,65 mm.

Alla fine degli anni '70 e all'inizio degli anni '80 apparve la montatura superficiale. I cavi (perni) e i componenti del chip sono saldati ad una superficie del circuito piuttosto che attraverso di esso. Ciò consente di utilizzare entrambi i lati della scheda per legare il chip, utilizzando la tecnologia di saldatura a riflusso durante l'installazione, con un numero massimo di pin di 80.

Verso la metà degli anni '80 apparvero pacchetti con lead su tutti i lati. Questo pacchetto è chiamato quad flat package (QFP) (il piombo ha la forma di un'ala di gabbiano) o portatore di chip di piombo (il piombo è piegato). J). Il pacchetto piatto quadrato tipico più comunemente usato ha un passo di 0,65 mm o 0,5 mm e un numero di piombo fino a 208. Questi pacchetti sono stati ampiamente utilizzati nei mercati dei dischi rigidi e della grafica nei primi anni '90.

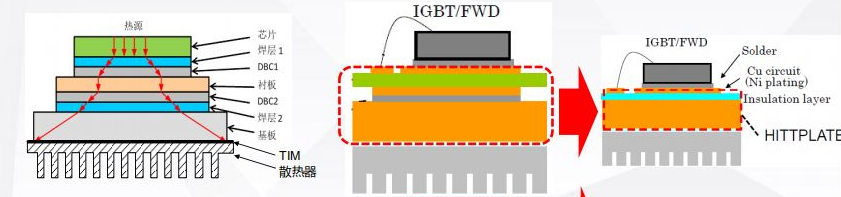

Alla fine degli anni '80 e all'inizio degli anni '90, nacque il Pacchetto Leaded Pad esposto. Il pacchetto è un pacchetto quadrangolare piatto o di forma più piccola con l'estremità di incollaggio del chip esposta sul fondo. Queste estremità di incollaggio esposte possono essere saldate al circuito stampato, stabilendo un percorso efficiente di dissipazione del calore per il chip.

La famiglia di pacchetti in miniatura Lead Frame (MLF) è stata sviluppata negli anni '90. MLF è vicino al Chip Scale Package (CSP), l'estremità inferiore del pacchetto viene utilizzata per fornire il contatto elettrico con la scheda PCB, al contrario del Gull Wing lead Soic e Quale Package, quindi questo pacchetto aiuta a garantire la dissipazione del calore e le prestazioni elettriche.

2. Imballaggio stratificato

imballaggi stratificati

Negli anni '90, un nuovo tipo di imballaggio, chiamato Ball Grid Array (BGA), è emerso utilizzando lastre stratificate come materiali di supporto. Gli imballaggi a base di telaio in piombo possono portare solo alla periferia dell'imballaggio... I cavi del pacchetto di griglia a sfera possono essere guidati alla palla di saldatura nella parte inferiore dell'intero pacchetto. Inizialmente, il campo di palla tipico per le confezioni BGA era di 1,27 mm.

3. Imballaggio a livello di wafer

Imballaggio a livello di wafer

Quando è necessario spazio, l'imballaggio migliore non è affatto imballaggio. Ulteriori lavorazioni possono essere effettuate a livello di wafer per produrre dispositivi che possono essere installati direttamente sul circuito stampato. Questo processo comporta tipicamente l'utilizzo di uno strato di ridistribuzione per trasferire la spaziatura fine sul wafer alla spaziatura più grossolana (tipicamente 0,5 mm) sul chip stesso, e quindi creare punti di urto sulla funzione del riordino. Il nucleo sarà separato separatamente e il pacchetto di livello del wafer è il nucleo convesso del blocco.

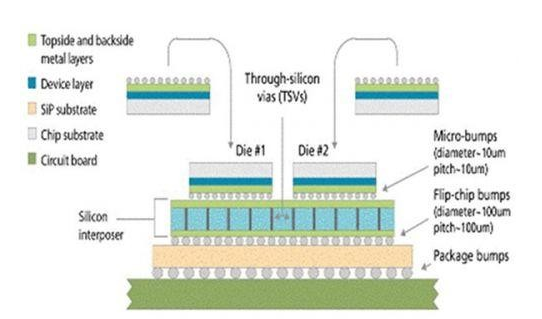

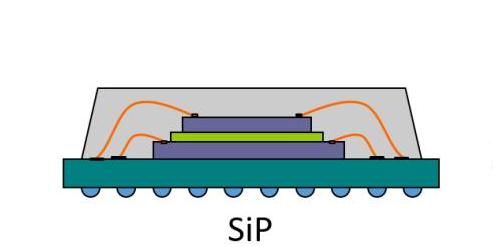

4. Incapsulazione a livello di sistema (SIP)

Ora un nuovo ciclo di integrazione sta mettendo più chip in un pacchetto chiamato pacchetto a livello di sistema (SIP). L'imballaggio multi-chip può essere ottenuto posizionando due o più chip nella stessa confezione (solitamente utilizzando substrati stratificati), o impilando un chip sopra un altro nella stessa confezione.

5. Sviluppo della tecnologia di interconnessione degli imballaggi

Interconnect descrive come i chip sono collegati a un substrato confezionato. Nella maggior parte dei pacchetti, il corpo del pacchetto viene prima unito alla superficie anteriore del terminale di collegamento del chip sul substrato (telaio di piombo o stratificazione), e poi il pad del chip è unito al dito di piombo del substrato utilizzando filo d'oro o di alluminio. Il superiore. Questa tecnica di interconnessione è chiamata legame al piombo ed è adatta per la maggior parte delle applicazioni di imballaggio. Un nuovo schema di interconnessione è chiamato Flip Chip Bonding. Un urto conduttivo viene generato sulla superficie del chip nella posizione del pad. Il chip di urto viene quindi capovolto e collegato direttamente al substrato. Nella maggior parte dei casi, viene utilizzato un substrato stratificato. L'adesione della sfera utilizzerà il processo di saldatura di riflusso. Dopo aver collegato il substrato e il reflow, viene utilizzato un processo di riempimento inferiore tra il chip e il substrato per ridurre lo stress causato dalla parte di saldatura del dispositivo durante l'uso.

6.Packaging Materiali Gli imballaggi di plastica sono soggetti a umidità e umidità. Il pacchetto iniziale era un'installazione a foro passante, che richiedeva meno affidabilità perché il calore generato durante la saldatura era lontano dal pacchetto (dall'altro lato della scheda). L'industria ha lavorato per migliorare le combinazioni di stampi e i materiali di collegamento del chip per eliminare la necessità di assemblaggio a secco. Un altro requisito recente per i materiali da imballaggio è quello di essere completamente privi di piombo e di utilizzare "materiali verdi" che soddisfano i requisiti ambientali.

7, processo di imballaggio sul processo del wafer del wafer dopo il processo di scribing è stato tagliato ChengXiaoJing rotondo (Die), e quindi tagliato il bastone del wafer sul substrato (telaio di piombo) corrispondente isola della struttura, quindi utilizzare superfine con metallo (oro, stagno, rame, alluminio) o tra un pad conduttivo di adesione del chip della resina e il supporto del pacchetto IC corrispondente collegamento al piombo, formano il circuito; I singoli chip vengono quindi incapsulati e protetti da una custodia di plastica. Dopo l'imballaggio in plastica, è necessario eseguire una serie di operazioni come la polimerizzazione post-stampo, lo stampaggio di rifilatura, la galvanizzazione e la stampa. Dopo che l'imballaggio è completato, il prodotto finito viene testato, di solito attraverso materiali in entrata, test, imballaggio e infine stoccaggio e spedizione. Tipico processo di imballaggio: taglio, caricamento, incollaggio, imballaggio di plastica, sbavatura, galvanizzazione, stampa, taglio di costole e formatura, ispezione dell'aspetto, test del prodotto finito, imballaggio e consegna.