1. Via

Via è uno dei componenti importanti del PCB multistrato, e il costo della perforazione di solito rappresenta dal 30% al 40% dei costi di produzione del PCB. In poche parole, ogni foro sul PCB può essere chiamato via. Dal punto di vista funzionale, i vias possono essere suddivisi in due categorie: una viene utilizzata per i collegamenti elettrici tra strati; l'altro è utilizzato per il fissaggio o il posizionamento di dispositivi. In termini di processo, questi vias sono generalmente divisi in tre categorie, vale a dire vias ciechi, vias sepolti e vias attraverso. I vias ciechi si trovano sulla superficie superiore e inferiore del circuito stampato e hanno una certa profondità. Sono utilizzati per collegare la linea superficiale e la linea interna sottostante. La profondità del foro di solito non supera un certo rapporto (apertura). Foro sepolto si riferisce al foro di collegamento situato nello strato interno del circuito stampato, che non si estende alla superficie del circuito stampato. I due tipi di fori sopra menzionati sono situati nello strato interno del circuito stampato e sono completati da un processo di formatura del foro passante prima della laminazione e diversi strati interni possono essere sovrapposti durante la formazione del via. Il terzo tipo è chiamato un foro passante, che penetra l'intero circuito stampato e può essere utilizzato per l'interconnessione interna o come foro di posizionamento di montaggio del componente. Poiché il foro passante è più facile da implementare nel processo e il costo è inferiore, la maggior parte dei circuiti stampati lo utilizza invece degli altri due tipi di fori passanti. I seguenti fori, se non diversamente specificato, sono considerati fori passanti.

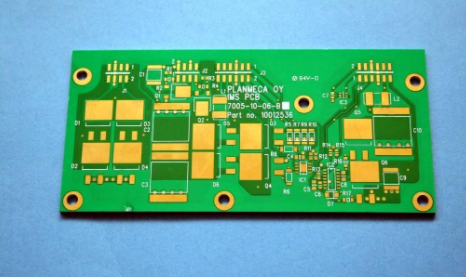

Dal punto di vista della progettazione, una via è composta principalmente da due parti, una è il foro del trapano nel mezzo e l'altra è l'area del pad intorno al foro del trapano, come mostrato nella figura sottostante. La dimensione di queste due parti determina la dimensione della via. Ovviamente, nel design PCB ad alta velocità e ad alta densità, i progettisti sperano sempre che più piccolo è il foro passante, meglio è, in modo che possa essere lasciato più spazio di cablaggio sulla scheda. Inoltre, più piccolo è il foro via, la capacità parassitaria propria. Più piccolo è, più adatto ai circuiti ad alta velocità. Tuttavia, la riduzione delle dimensioni dei fori comporta anche un aumento dei costi e le dimensioni dei vias non possono essere ridotte indefinitamente. È limitato da tecnologie di processo come foratura e placcatura: più piccolo è il foro, più foratura Più lungo il foro richiede, più facile è deviare dalla posizione centrale; e quando la profondità del foro supera 6 volte il diametro del foro forato, non si può garantire che la parete del foro possa essere placcata uniformemente con rame. Ad esempio, lo spessore (attraverso la profondità del foro) di una normale scheda PCB a 6 strati è di circa 50Mil, quindi il diametro minimo di perforazione che i produttori di PCB possono fornire può raggiungere solo 8Mil.

In secondo luogo, la capacità parassitaria della via

La via stessa ha una capacità parassitaria al suolo. Se è noto che il diametro del foro di isolamento sullo strato di terra della via è D2, il diametro del pad via è D1, lo spessore della scheda PCB è T e la costante dielettrica del substrato della scheda è ε, quindi la capacità parassitaria della via è approssimativamente:

C=1,41εTD1/(D2-D1)

L'effetto principale della capacità parassitaria della via sul circuito è quello di estendere il tempo di salita del segnale e ridurre la velocità del circuito. Ad esempio, per un PCB con uno spessore di 50Mil, se viene utilizzata una via con un diametro interno di 10Mil e un diametro del pad di 20Mil e la distanza tra il pad e l'area di rame macinato è 32Mil, allora possiamo approssimare la via utilizzando la formula di cui sopra La capacità parassitaria è approssimativamente: C=1.41x4.4x0.050xx.020/(0.032-0.020)=0.517pF, Il cambiamento del tempo di salita causato da questa parte della capacità è: T10-90=2.2C(Z0/2)=2.2 x0.517x(55/2)=31.28ps. Si può vedere da questi valori che anche se l'effetto del ritardo di risalita causato dalla capacità parassitaria di una singola via non è evidente, se la via viene utilizzata più volte nella traccia per passare tra strati, il progettista dovrebbe comunque considerare attentamente.

In terzo luogo, l'induttanza parassitaria della via

Allo stesso modo, ci sono induttanze parassitarie insieme alla capacità parassitaria dei vias. Nella progettazione di circuiti digitali ad alta velocità, il danno causato dall'induttanza parassitaria dei vias è spesso maggiore dell'impatto della capacità parassitaria. La sua induttanza di serie parassitaria indebolirà il contributo del condensatore bypass e indebolirà l'effetto filtrante dell'intero sistema di alimentazione. Possiamo semplicemente calcolare l'induttanza parassitaria di una via con la seguente formula:

L=5.08h[ln(4h/d)+1] dove L si riferisce all'induttanza della via, h è la lunghezza della via, e d è il diametro del foro centrale. Si può vedere dalla formula che il diametro della via ha una piccola influenza sull'induttanza e la lunghezza della via ha la maggiore influenza sull'induttanza. Sempre usando l'esempio precedente, l'induttanza della via può essere calcolata come: L=5.08x0.050[ln(4x0.050/0.010)+1]=1.015nH. Se il tempo di salita del segnale è 1ns, allora la sua impedenza equivalente è: XL=ÏL/T10-90=3.19Ω. Tale impedenza non può più essere ignorata quando passano correnti ad alta frequenza. Particolare attenzione dovrebbe essere prestata al fatto che il condensatore bypass deve passare attraverso due vie quando si collega il piano di potenza e il piano di terra, in modo che l'induttanza parassitaria dei vie aumenterà esponenzialmente.

Quarto, tramite progettazione in PCB ad alta velocità

Attraverso l'analisi di cui sopra delle caratteristiche parassitarie dei vias, possiamo vedere che nella progettazione di PCB ad alta velocità, il processo apparentemente semplice èHoles spesso portano anche grandi effetti negativi alla progettazione di circuiti. Al fine di ridurre gli effetti avversi causati dagli effetti parassitari dei vias, nel disegno si possono fare quanto segue:

1. considerando il costo e la qualità del segnale, scegliere una dimensione ragionevole tramite dimensione. Ad esempio, per il design PCB del modulo di memoria a 6-10 strati, è meglio utilizzare 10/20Mil (forato / pad). Per alcune schede ad alta densità di piccole dimensioni, puoi anche provare a utilizzare 8/18Mil. buco. Nelle attuali condizioni tecniche, è difficile utilizzare vias più piccoli. Per via di alimentazione o messa a terra, è possibile prendere in considerazione l'utilizzo di una dimensione più grande per ridurre l'impedenza.

2. Le due formule sopra descritte possono essere disegnate. L'uso di un PCB più sottile è utile per ridurre i due tipi di vias. Parametri sanitari.

3. Cercate di non cambiare gli strati delle tracce del segnale sulla scheda PCB, vale a dire, cercate di non utilizzare vias inutili.

4. il potere e i perni di terra dovrebbero essere forati nelle vicinanze e il cavo tra la via e il perno dovrebbe essere il più breve possibile, perché aumenteranno l'induttanza. Allo stesso tempo, i cavi di potenza e terra dovrebbero essere il più spessi possibile per ridurre l'impedenza.

5. Posizionare alcuni vias a terra vicino ai vias dello strato di segnale per fornire il loop più vicino per il segnale. È anche possibile posizionare un gran numero di vias di terra ridondanti sulla scheda PCB. Naturalmente, il design deve essere flessibile. Il modello via discusso in precedenza è il caso in cui ci sono pad su ogni strato. A volte, possiamo ridurre o persino rimuovere i pad di alcuni strati. Soprattutto quando la densità dei vias è molto alta, può portare alla formazione di una scanalatura rotta che separa il loop nello strato di rame. Per risolvere questo problema, oltre a spostare la posizione della via, possiamo anche considerare di posizionare la via sullo strato di rame. La dimensione del tampone è ridotta.