Principios y aplicaciones de encapsulamiento de circuitos integrados tridimensionales

2.5d la capa intermedia es una configuración que utiliza un agujero de silicio (tsv) a través de la capa intermedia para instalar el núcleo lado a lado en la capa intermedia de silicio, vidrio o orgánico. (cuando se utilizan laminados de vidrio o orgánico como base de la capa intermedia, se llaman a través del agujero de vidrio penetrante (tgv) y a través del agujero de base (tsv), respectivamente.) La comunicación entre los núcleos se realiza a través de circuitos fabricados en la capa intermedia.

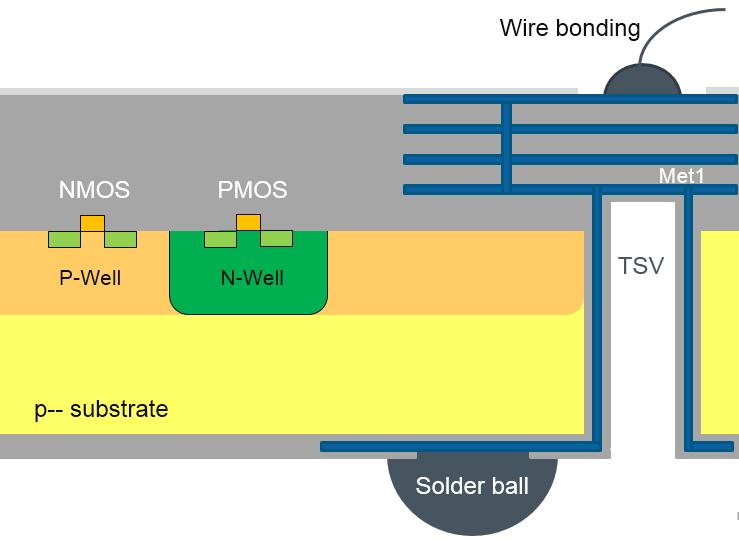

El sensor de imagen CMOS (cis) tiene TSV como agujero trasero para formar interconexiones, eliminando la fusión de teclas de plomo, reduciendo así el tamaño y aumentando la densidad. En todos los tipos de encapsulamiento 3d, los chips en el encapsulamiento se comunican utilizando señales fuera del chip, como si estuvieran instalados en un encapsulamiento separado en una placa de circuito normal.

Los IC 3D se pueden dividir en IC apilados 3D (3d - sic), lo que significa que los chips IC se apilan e interconectan con tsv; El verdadero IC 3D utiliza el proceso FAB para apilar varias capas de dispositivos en un solo chip, y se pueden usar o no tsvs con intervalos muy finos para formar interconexiones.

El agujero de silicio (tsv) es un agujero formado en una pastilla de silicio utilizando un proceso de grabado. La interconexión se forma llenando TSV con materiales conductores como cobre, tungsteno o polisilicio (figura 2). La principal ventaja de las interconexiones TSV es que acortan el camino de las señales que se transmiten de un chip al siguiente o de una capa de circuito a otra. Esto permite reducir la Potencia y aumentar la capacidad de densidad de interconexión, mejorando así la función y el rendimiento. El TSV en sí no es un IC 3D. En cambio, son la base para habilitar circuitos integrados tridimensionales. Los agujeros a través de la parte posterior también se utilizan en otros dispositivos, como sensores de imagen, Sistemas microelectromecánicos (microelectromecánicos) y semiconductores compuestos.

¿¿ qué significa un IC 3D único?

El IC 3D único no es apilar chips o módulos para crear el IC 3d, sino comenzar con el chip base, utilizando dispositivos FAB tradicionales en el chip base para agregar capas adicionales, como silicio cristalino, capas metálicas y circuitos activos y pasivos (figura 2). El uso de agujeros a través en el rango de nanómetros en lugar de micras para formar interconexiones verticales entre capas en lugar de entre chips; Lo mismo que el tsv. Actualmente se están desarrollando varios métodos diferentes, principalmente para aplicaciones de memoria. La dimensión tridimensional integral a veces se llama dimensión tridimensional continua.

¿¿ qué es la memoria 3d?

Se han desarrollado muchos métodos para apilar memorias perpendiculares a dos dispositivos no volátiles (memoria Flash nand) y memoria volátil (dram). Los métodos DRAM incluyen memorias de alto ancho de banda (hbm), cubos de memoria híbridos de micron y Ram integrada (diram) de tezzaron. Todo esto se basa en el IC 3D que utiliza TSV (figura 3). Samsung, Toshiba y muchas otras compañías están desarrollando memorias flash 3D Nand basadas en métodos 3D integrales.

¿¿ cuáles son las ventajas de la tecnología de inserción 2.5d?

La tecnología 2.5d fue desarrollada originalmente como tecnología de puente para circuitos integrados 3d, y ahora se ha convertido en una plataforma de encapsulamiento que se espera que coexista con circuitos integrados 3D. A diferencia del 3D - ic, solo la capa intermedia (y no el núcleo en sí) necesita TSV para conectar el núcleo activo al sustrato encapsulado. Esto permite el uso de diseños de moldes existentes.

¿¿ cuáles son los principales impulsores tecnológicos de la integración 3d?

En los nodos de la próxima generación de chips, este aumento general de los costos de los pasos fotolitográficos y el procesamiento de chips ha llevado a la industria a buscar alternativas para mejorar el rendimiento y el funcionamiento de nuestros dispositivos electrónicos y reducir los costos. Además, la demanda de pequeñas integraciones de diversas tecnologías (lógica, memoria, radiofrecuencia, sensores, etc.) está impulsando a la industria a considerar la integración 3D como una solución.

¿¿ cuáles son los impulsores del mercado de la integración 3d?

La fuerza impulsora del mercado de la integración 3D comienza con la computación de alta gama, servidores y centros de datos, militares y aeroespaciales, y equipos médicos, ya que son los que más demanda tienen y pueden soportar los costos de la tecnología actual de integración 3D. Las tabletas, los teléfonos inteligentes y los dispositivos de juego también están impulsando esta tecnología.

¿¿ cuáles son los desafíos que enfrentan los circuitos integrados 3d?

Aunque muchos afirman que no quedan desafíos técnicos y que los problemas restantes pueden resolverse fácilmente, algunos pasos del proceso todavía requieren mejores soluciones, como herramientas de diseño para la planificación, implementación y verificación de circuitos integrados 2.5d y 3d, procesamiento de chips, gestión térmica y pruebas. Los principales desafíos son los costos unitarios actuales, el bajo número y los riesgos de implementación debido a la madurez del ecosistema. Se están haciendo esfuerzos para reducir los costos de los procesos y simplificar la colaboración en toda la industria. Aumentar la producción ayudará a reducir costos. Sin embargo, muchos expertos en 3D creen que la implementación de circuitos integrados 3D reducirá significativamente los costos del sistema, y el desafío restante es educar a los ingenieros a nivel de sistema para diseñar circuitos integrados 3D en sus sistemas.

El sensor de imagen CMOS (cis) es uno de los primeros dispositivos en lograr un gran número de agujeros a través. El cis (bsi) con iluminación posterior está actualmente en producción y, dado que el CIS está apilado en la parte superior del ic, es un dispositivo IC 3D (figura 2). Xilinx lanzó en 2011 el diseño del plug - in 2.5d para todos los FPGAs programables de su serie virtex - 7. En los últimos años, tezzaron ha entregado pequeñas cantidades de diram.

A finales de 2014, micron y Samsung comenzarán a producir cubos de almacenamiento híbrido (hmcs), una pila de DRAM 3D ubicada sobre dispositivos lógicos. SK Hynix proporcionará tanto HMC como memoria de alto ancho de banda (hbm). Estos dispositivos de almacenamiento integrados en 3D se produjeron a gran escala en 2014 / 15 y continuaron utilizando pilas lógicas y dispositivos heterogéneos en los años siguientes.

¡¡ el IPCB compartirá toda la información con usted!