Además de la tecnología avanzada, el embalaje avanzado se ha convertido en una tecnología clave para continuar la Ley de moore. En los últimos años, tecnologías como 2.5d, 3D y chips se han convertido en temas candentes en la industria de semiconductores. ¿¿ cómo juegan los envases avanzados un papel clave en la continuación de la Ley de moore? ¿¿ cuáles son las características de tecnologías de encapsulamiento como 2.5d, 3D y chiplets?

Han surgido aplicaciones como la inteligencia artificial, la red de vehículos y el 5g, que requieren el uso de chips funcionales avanzados de computación de alta velocidad, transmisión de alta velocidad, baja latencia y bajo consumo de energía. Sin embargo, a medida que la demanda de computación se multiplica, cómo continuar la Ley de Moore es un desafío para la industria de semiconductores.

A medida que la miniaturización de los chips es cada vez más difícil, surgió la integración heterogénea.

En otras palabras, los procesos avanzados de semiconductores se están desarrollando hacia 7 nm, 5 nm, y luego 3 nm y 2 nm. Por lo tanto, el tamaño del Transistor se acerca al límite de volumen físico del átomo. Las restricciones electrónicas y físicas también dificultan cada vez más que los procesos avanzados sigan reduciéndose y actualizándose.

Por lo tanto, además de seguir desarrollando procesos avanzados, la industria de semiconductores también está buscando otras formas de mantener los chips miniaturizados y eficientes. El diseño del chip se ha convertido en una nueva solución para continuar la Ley de moore, y el concepto de sistema de arquitectura de diseño integrado heterogéneo (hidas) ha surgido y se ha convertido en la fuerza motriz de la innovación de los chips de circuitos integrados.

La llamada integración heterogénea, en sentido amplio, es la integración de dos chips diferentes, como memoria + chip lógico, fotoelectricidad + componente electrónico, a través de encapsulamiento, apilamiento 3D y otras tecnologías. En otras palabras, la integración de dos chips con diferentes procesos y diferentes rendimientos puede llamarse integración heterogénea.

Debido a que el mercado de aplicaciones es más diversificado, el costo, el rendimiento y la población objetivo de cada producto son diferentes, por lo que las tecnologías de integración heterogénea necesarias también son diferentes, y la tendencia de enfoque del mercado está emergiendo gradualmente. Por lo tanto, las industrias de oem, fabricación y equipos semiconductores de IC han invertido en el desarrollo de integración heterogénea, 2.5d, encapsulamiento 3d, chiplets y otras tecnologías de encapsulamiento populares se basan en el concepto de integración heterogénea, como los brotes de primavera.

2.5d encapsulamiento reduce efectivamente los costos de producción de chips

En el pasado, para integrar los chips, la mayoría de ellos utilizaban tecnologías de sistemas en encapsulamiento (sip), como encapsulamiento PIP (encapsulamiento en encapsulamiento) y encapsulamiento pop (encapsulamiento en encapsulamiento). Sin embargo, como teléfonos inteligentes, aiot y otras aplicaciones, no solo se necesita un mayor rendimiento, sino también mantener un tamaño pequeño y un bajo consumo de energía, en este caso, debemos encontrar una manera de apilar más chips para reducir el volumen, por lo que la tecnología de encapsulamiento actual, además del SIP original, también se está desarrollando hacia la tecnología de encapsulamiento tridimensional.

En resumen, el encapsulamiento tridimensional implica el uso de capas intermedias de silicio (capas intermedias de silicio) hechas directamente de pastillas de silicio, en lugar de usar "portadores de alambre" plásticos anteriores, y encapsular directamente varios chips con diferentes funciones en un chip más eficiente. En otras palabras, la adición de pastillas de silicio al silicio aumenta las limitaciones físicas de costos y procesos, manteniendo así efectiva la Ley de moore.

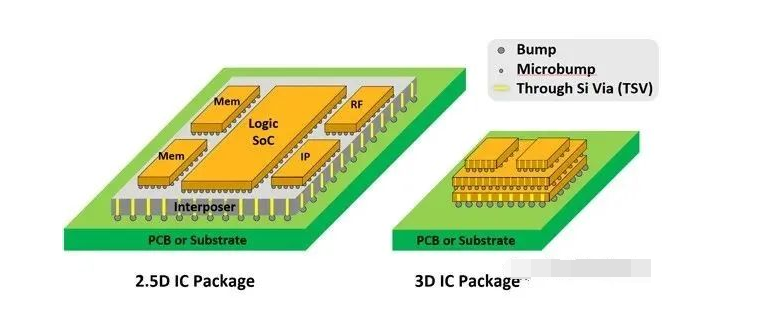

Los envases tridimensionales están más familiarizados con los envases 2.5d y 3d, donde comenzamos con los envases 2.5d. El concepto principal del llamado encapsulamiento 2.5d es organizar procesadores, memorias u otros chips en el Interpolador de silicio, que se conecta a través de micropacks para que los cables metálicos de la interpolación de silicio puedan conectarse a las señales electrónicas de diferentes chips. A continuación, el TSV se utiliza para conectar las protuberancias metálicas inferiores y la placa portadora del cable se utiliza para conectar bolas metálicas externas para lograr una interconexión más estrecha entre el chip, el chip y el sustrato de encapsulamiento.

2.5d y encapsulamiento 3D son las tecnologías de encapsulamiento tridimensional populares en la actualidad. (fuente: ansys)

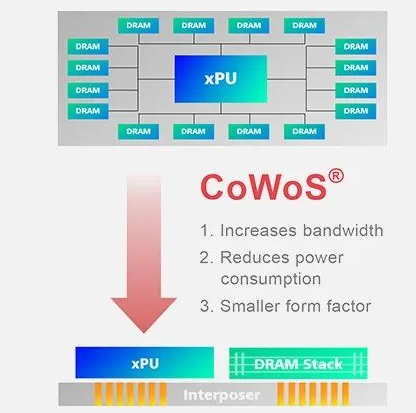

La conocida tecnología de encapsulamiento 2.5d no es más que el cowos de tsmc. El concepto de la tecnología cowos es colocar chips semiconductores (como procesadores, memorias, etc.) en una capa intermedia de silicio y luego conectarlos al sustrato inferior a través del proceso de encapsulamiento de los chips en el chip (cow). En otras palabras, el chip se conecta primero al chip de silicio a través del proceso de encapsulamiento del CHIP en el chip (cow), y luego el chip Cow se conecta al sustrato e integra en cowos. Con este modo de encapsulamiento, se pueden encapsular varios chips e interconectar a través de un Interpolador de silicio, logrando así el efecto de encapsulamiento pequeño, bajo consumo de energía y pocos pines.

El concepto de tecnología de encapsulamiento de tsmc. (fuente: tsmc)

Además de los cowos, los envases a nivel de obleas fanout también se pueden clasificar como un método de encapsulamiento 2.5d. El principio del paquete a nivel de obleas es sacar el circuito necesario del extremo del Semiconductor desnudo a la capa de redistribución para formar el paquete. Por lo tanto, no es necesario sellar las placas de carga, los cables, las protuberancias, lo que puede reducir los costos de producción en un 30% y también hacer que el chip sea más delgado. Al mismo tiempo, se puede reducir considerablemente el área del chip. También puede reemplazar las perforaciones de silicio de mayor costo, logrando la integración de diferentes componentes a través de la tecnología de encapsulamiento.

Por supuesto, la tecnología de encapsulamiento tridimensional no es solo 2.5d, sino también encapsulamiento 3D. ¿Entonces, ¿ cuál es la diferencia entre los dos y la industria de semiconductores está utilizando encapsulamiento 3d?

En comparación con el encapsulamiento 2.5d, el encapsulamiento 3D funciona creando una estructura de Transistor (cmos) en el chip y conectando señales electrónicas de diferentes chips arriba y abajo con agujeros de silicio para que la memoria u otros chips puedan apilarse directamente y verticalmente.

El encapsulamiento 3D es la pila directa de chips. (fuente: intel)

TSMC e Intel desarrollan activamente tecnología de encapsulamiento 3D

Intel (intc) y Taiwan Semiconductor (tsmc) tienen sus propias tecnologías de encapsulamiento 3D. Intel está utilizando la tecnología de encapsulamiento 3D "foceros", que utiliza lógica de pila heterogénea para procesar las operaciones y puede apilar cada chip lógico juntos. Esto significa que, por primera vez, la pila de chips se extiende desde los medios de silicio pasivo tradicionales y las memorias apiladas a productos lógicos eficientes como cpu, procesadores gráficos e ia. En el pasado, las apilamientos se utilizaban solo para memorias, pero ahora se utilizan apilamientos heterogéneos para lograr apilamientos de diferentes combinaciones de memorias y chips informáticos.

Además, Intel está desarrollando tres nuevas tecnologías, a saber, Co - emib, ODI y mdio. El Co - emib puede conectarse a un mayor rendimiento y capacidad computacional y permitir la interconexión de dos o más componentes de focos. Los diseñadores también pueden conectar simuladores, memoria y otros módulos con un ancho de banda muy alto y un consumo de energía muy bajo. La tecnología ODI proporciona una mayor flexibilidad para la comunicación de interconexión integral entre chips pequeños y medianos. El chip superior puede comunicarse con otros chips pequeños, como la tecnología emib, que puede comunicarse verticalmente con el chip desnudo inferior inferior a través de un agujero de silicio (tsv), como la tecnología foveros.

Concepto tecnológico Intel foveros. (fuente: intel)

La tecnología también utiliza grandes agujeros verticales para suministrar energía directamente desde el sustrato de encapsulamiento a la placa desnuda superior. Estos grandes agujeros son mucho más grandes que los agujeros de silicio tradicionales y proporcionan una transmisión de potencia más estable con una resistencia más baja. Y lograr un mayor ancho de banda y menor latencia a través de la pila. Este método reduce el número de agujeros de silicio necesarios en el chip base, libera más área para los componentes activos y optimiza el tamaño de las hojas desnudas.

Por otro lado, TSMC está proponiendo una solución integrada de "chip múltiple 3D y chip integrado de sistemas" (soic). La solución en chip integrada por el sistema superpone directamente los buenos cristales desnudos conocidos de diferentes tamaños, técnicas de proceso y materiales.

TSMC señaló que los chips integrados de este sistema tienen varias veces una alta densidad y velocidad de protuberancias en comparación con las soluciones tradicionales de circuitos integrados 3D que utilizan microcuencas, al tiempo que reducen significativamente el consumo de energía. Además, el chip integrado del sistema es una solución integrada de preprocesamiento que conecta dos o más cristales desnudos antes del encapsulamiento; Por lo tanto, el chipset de integración de sistemas puede utilizar la tecnología avanzada de encapsulamiento de back - end Ifo o cowos de la compañía para integrar aún más otros chips, creando así una potente solución a nivel de sistema "3d * 3d".

Además, TSMC ha lanzado 3dfabric, que combina soluciones de integración de sistemas 3tic de rápido crecimiento para ofrecer una mayor flexibilidad y crear sistemas potentes con potentes interconexiones de chips. 3dfabric tiene diferentes opciones de apilamiento de chips delanteros y encapsulamiento de chips traseros para ayudar a los clientes a conectar múltiples chips lógicos juntos, incluso pequeños chips heterogéneos como memorias anchas de alta frecuencia en serie (hbm) o analogías, entradas / salidas y módulos de radiofrecuencia. 3dfabric combina soluciones 3D traseras y frontales y complementa el modelo de miniaturas de Transistor para mejorar continuamente el rendimiento y la función del sistema, reducir el tamaño y la apariencia y acelerar el tiempo de comercialización del producto.

Después del lanzamiento de 2.5d y 3d, chiplets es una de las últimas tecnologías de encapsulamiento avanzadas que impactan en la industria de semiconductores. Por último, se presentan brevemente las características y ventajas de chiplets.

El uso de chiplets tiene tres beneficios. Debido a que el costo de los procesos avanzados es muy alto, especialmente los circuitos analógicos y el I / o son cada vez más difíciles de contraer con el desarrollo de la tecnología de proceso. Los chips dividen los circuitos en pequeños chips independientes, mejoran sus funciones, tecnología de proceso y tamaño, y finalmente los integran para superar el desafío de la miniaturización de los procesos. Además, chiplets también puede utilizar chips maduros existentes para reducir los costos de desarrollo y verificación.

En la actualidad, muchos fabricantes de semiconductores han lanzado productos de alto rendimiento en forma de chips. Por ejemplo, la FPGA de 10 metros Intel stratix 10 GX de Intel está diseñada con chips para lograr una mayor densidad y capacidad de componentes. El producto se basa en la arquitectura existente de Intel stratix 10 FPGAs y la avanzada tecnología de puente de interconexión multichip integrado (emib) de intel, utilizando la tecnología emib para integrar dos chips lógicos centrales de Intel stratix 10 GX FPGAs de alta densidad y las unidades de E / s correspondientes. Lo mismo ocurre con los procesadores de la serie epyc de segunda generación de amd. A diferencia de la primera generación de métodos de chip que combinan memoria e I / o para formar una CPU de 14 nm, la segunda generación es separar I / o y memoria en un chip y cortar la CPU de 7 nm en ocho chips para combinar.

En resumen, en el pasado, la eficiencia de los chips se mejoraba mediante mejoras en los procesos de semiconductores, pero a medida que el tamaño de los componentes se acercaba a los límites físicos, la miniaturización de los chips se hacía cada vez más difícil. Para mantener el diseño de chips de pequeño tamaño y alta eficiencia, la industria de semiconductores no solo continúa desarrollando procesos avanzados, sino que también mejora la arquitectura de chips para que los chips pasen de la monocapa original a la pila de varias capas. Por lo tanto, el embalaje avanzado también se ha convertido en uno de los factores impulsores clave para mejorar la Ley de moore, liderando la tendencia de la industria de semiconductores.

Las principales tareas del futuro laboratorio inteligente incluyen: establecer un sistema de evaluación del coeficiente intelectual del sistema de inteligencia artificial y llevar a cabo la evaluación del coeficiente intelectual de la inteligencia artificial mundial; Llevar a cabo el programa de investigación del cerebro en la nube de Internet (ciudad), construir la tecnología del cerebro en la nube de Internet (ciudad) y el mapa empresarial, y servir para mejorar el nivel de inteligencia de las empresas, industrias y ciudades.