[Produttore di substrati IC] l'intero processo dalla progettazione di chip IC, produzione all'imballaggio

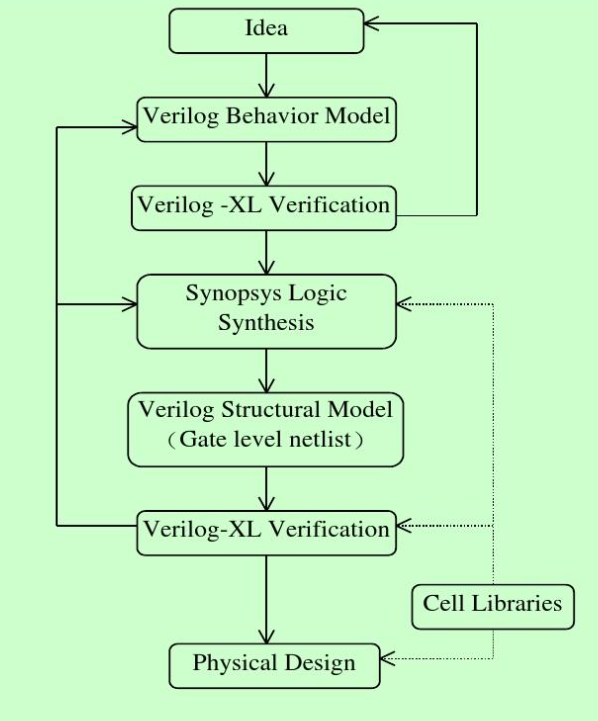

1, processo complicato di progettazione del chip IC

Il processo di fabbricazione dei chip è come costruire una casa con LEGO. Dopo che il wafer è utilizzato come fondamento e quindi il processo di fabbricazione del chip è impilato strato dopo strato, i chip IC necessari possono essere prodotti (questi saranno introdotti in seguito). Tuttavia, senza disegni di progettazione, è inutile avere una forte capacità produttiva. Pertanto, il ruolo degli architetti è molto importante. Ma chi è l'architetto nel design IC? Successivamente, questo documento introdurrà il design IC.

Nel processo di produzione IC, la maggior parte dei IC sono progettati e progettati da società professionali di progettazione IC, come MediaTek, Qualcomm, Intel e altri produttori ben noti, tutti progettano i propri chip IC e forniscono chip con specifiche ed efficienza diverse per i produttori a valle da scegliere. Poiché IC è progettato da ogni fabbrica, la progettazione IC dipende dalla tecnologia degli ingegneri e la qualità degli ingegneri influisce sul valore di un'impresa. Tuttavia, quando gli ingegneri progettano un chip IC, quali sono i passaggi? Il processo di progettazione può essere semplicemente suddiviso in quanto segue.

Processo di fabbricazione IC

Progettare il primo passo e impostare gli obiettivi

Nella progettazione IC, il passo più importante è la specificazione. Questo passaggio è come decidere quante stanze e bagni sono necessari prima di progettare l'edificio, quali norme edilizie devono essere rispettate, e progettare dopo aver determinato tutte le funzioni, in modo da non dedicare ulteriore tempo alle successive modifiche. La progettazione IC deve anche passare attraverso passaggi simili per garantire che il chip progettato non abbia errori.

Il primo passo nella formulazione delle specifiche è determinare lo scopo e l'efficienza del IC e impostare la direzione generale. Il passo successivo è vedere quali protocolli rispettare. Ad esempio, il chip della scheda di rete wireless deve essere conforme a IEEE 802.11 e ad altre specifiche. In caso contrario, il chip non sarà compatibile con i prodotti presenti sul mercato, quindi non sarà in grado di connettersi con altri dispositivi. L'ultimo è quello di stabilire il metodo di implementazione del IC, assegnare diverse funzioni in diverse unità e stabilire il metodo di connessione tra le diverse unità, in modo da completare la formulazione delle specifiche.

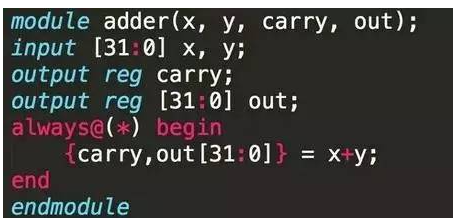

Dopo aver progettato le specifiche, i dettagli della progettazione del chip sono seguiti. Questo passaggio è come scrivere il piano architettonico inizialmente e disegnare il contorno generale per la comodità del disegno successivo. Nel chip IC, il linguaggio di descrizione hardware (HDL) è usato per descrivere il circuito. L'HDL comunemente usato include Verilog, VHDL, ecc. La funzione di un IC può essere facilmente espressa tramite codice. Quindi controllare la correttezza della funzione del programma e continuare a modificarla fino a quando non soddisfa la funzione desiderata.

Esempio Verilog di adder a 32 bit

Con i computer, tutto diventa facile

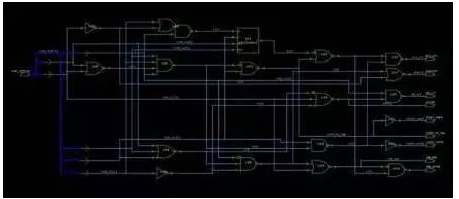

Con un piano completo, il passo successivo è quello di disegnare un progetto di progettazione della scheda. Nella progettazione IC, il passo della sintesi logica è quello di mettere il codice HDL determinato nello strumento di automazione elettronica della progettazione (strumento EDA), e lasciare che il computer converta il codice HDL in circuito logico per produrre il seguente diagramma del circuito. Quindi, determinare ripetutamente se il disegno di progettazione del cancello logico soddisfa le specifiche e modificarlo fino a quando la funzione non è corretta.

Risultati della sintesi delle unità di controllo

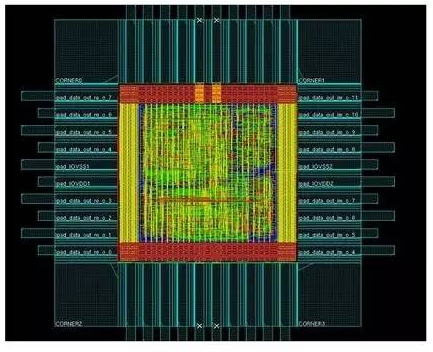

Infine, inserire il codice sintetizzato in un altro set di strumenti EDA per la disposizione del circuito e il luogo e il percorso. Dopo il rilevamento continuo, verrà formato il seguente diagramma del circuito. Nella foto, puoi vedere diversi colori come blu, rosso, verde e giallo. Ogni colore diverso rappresenta una maschera di luce. Come usare la maschera?

layout e avvolgimento

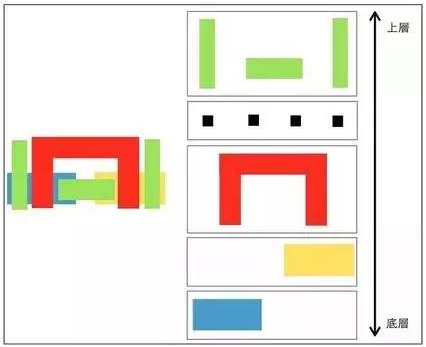

Strati di maschere, impilati un chip

Prima di tutto, è noto che un IC produrrà più maschere. Queste maschere hanno livelli superiori e inferiori, e ogni livello ha il suo compito. La figura seguente è un semplice esempio di maschera. Prendendo CMOS, l'elemento più basilare dei circuiti integrati, ad esempio, il nome completo di CMOS è semiconduttore complementare di ossido di metallo, cioè combinando NMOS e PMOS per formare CMOS. Per quanto riguarda che cosa è semiconduttore di ossido di metallo (MOS)? Questo tipo di componente ampiamente utilizzato nel chip è difficile da spiegare ed è difficile per i lettori ordinari capire. Non lo studierò più qui.

Nella figura sottostante, il lato sinistro è il diagramma del circuito formato dopo la disposizione del circuito e l'avvolgimento. È noto che ogni colore rappresenta una maschera. A destra è la diffusione di ogni cappuccio. La produzione deve partire dal basso, seguire il metodo proposto nel precedente articolo sulla produzione di chip IC, farli strato per strato, e infine produrre il chip desiderato.

Finora, dovremmo avere una comprensione preliminare della progettazione IC. Nel complesso, è chiaro che la progettazione IC è una specialità molto complessa. Grazie alla maturità del software assistito da computer, la progettazione IC può essere accelerata. La fabbrica di progettazione IC si basa fortemente sulla saggezza degli ingegneri. Ogni passo descritto qui ha la propria esperienza e può essere diviso in più corsi professionali. Ad esempio, scrivere un linguaggio di descrizione hardware non è semplice. Ha solo bisogno di avere familiarità con il linguaggio di programmazione, ma ha anche bisogno di capire come funziona il circuito logico e come convertire gli algoritmi richiesti in programmi Come il software sintetico converte i programmi in porte logiche.

2, Che cosa è un wafer?

Nella notizia dei semiconduttori, citiamo sempre le fabbriche di wafer segnate da dimensioni, come le fabbriche di wafer da 8 pollici o 12 pollici. Tuttavia, qual è il cosiddetto wafer? Quale parte è di 8 pollici? Quanto è difficile produrre wafer di grandi dimensioni? Di seguito è un'introduzione passo-passo alla base più importante dei semiconduttori - che cosa è "wafer".

I wafer sono la base per la produzione di tutti i tipi di chip per computer. Possiamo confrontare la produzione di chip alla costruzione di una casa con blocchi Lego e completare la nostra forma desiderata (cioè tutti i tipi di chip) impilando strato dopo strato. Tuttavia, se non c'è una buona base, la casa costruita sarà storta, che non è quello che vuoi. Per rendere una casa perfetta, hai bisogno di una piastra di base stabile. Per la produzione di chip, questo substrato è il wafer da descrivere successivamente.

Prima di tutto, ricordiamo che quando giocavamo con i grattacieli da bambini, ci sarebbe stata una piccola proiezione circolare sulla superficie dei blocchi. Con questa struttura, possiamo impilare stabilmente i due blocchi insieme senza usare colla. La produzione di chip fissa anche gli atomi aggiunti successivamente e il substrato insieme in modo simile. Pertanto, abbiamo bisogno di trovare un substrato con superficie pulita per soddisfare le condizioni richieste per la produzione successiva.

Nei materiali solidi, c'è una speciale struttura di cristallo - cristallo singolo. Ha la caratteristica che gli atomi sono disposti strettamente uno ad uno e possono formare una superficie atomica piana. Pertanto, i requisiti di cui sopra possono essere soddisfatti utilizzando il singolo cristallo per fare wafer. Tuttavia, come produrre un tale materiale? Ci sono due passaggi principali: purificazione e disegno di cristallo, e quindi un tale materiale può essere completato.

Come fare un singolo wafer di cristallo

La purificazione è divisa in due fasi. Il primo passo è la depurazione metallurgica. Questo processo consiste principalmente nell'aggiungere carbonio e convertire l'ossido di silicio in silicio con purezza superiore al 98% mediante ossidazione-riduzione. La maggior parte della raffinazione dei metalli, come ferro o rame, utilizza questo metodo per ottenere metallo di sufficiente purezza. Tuttavia, il 98% non è ancora sufficiente per la produzione di trucioli e deve essere ulteriormente migliorato. Pertanto, il processo Siemens sarà ulteriormente utilizzato per la purificazione. In questo modo, si otterrà polisilico ad alta purezza richiesto dal processo a semiconduttore.

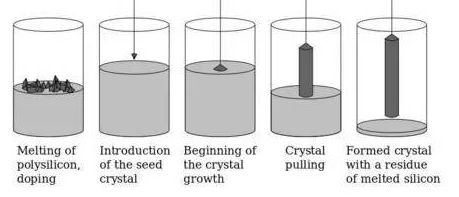

Processo di fabbricazione della colonna di silicio

Il prossimo passo è il disegno di cristallo. In primo luogo, il polisilico ad alta purezza ottenuto sopra viene fuso per formare silicio liquido. Quindi, contatta la superficie liquida con un singolo seme di cristallo e tiralo lentamente su mentre ruota. Per quanto riguarda il motivo per cui il silicio monocristallo è necessario, è perché la disposizione degli atomi di silicio è la stessa di quella delle persone in linea. Avrà bisogno di un leader per far sapere alle persone successive come organizzare correttamente. I semi di silicio sono un leader importante per far sì che gli atomi successivi sappiano fare la coda. Infine, dopo che gli atomi di silicio lasciano la superficie liquida si solidificano, le colonne di silicio monocristallino ordinatamente disposte sono completate

Colonna di silicio monocristallino

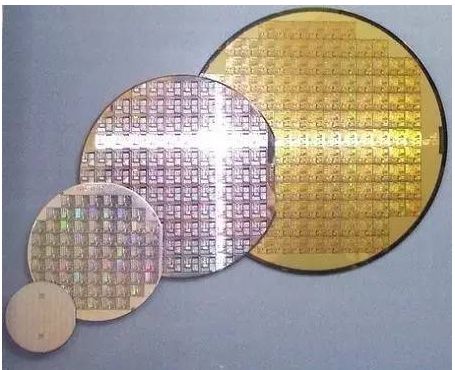

Tuttavia, cosa rappresentano 8 pollici e 12 pollici? Si riferisce al diametro della colonna di cristallo prodotta da noi, che assomiglia alla parte del portapenne. La superficie viene trattata e tagliata in sottili pezzi rotondi. Qual è la difficoltà di realizzare wafer di grandi dimensioni?

Come accennato in precedenza, il processo di fabbricazione della colonna di cristallo è come fare zucchero filato, ruotando e formando allo stesso tempo. Se hai mai fatto marshmallow, dovresti sapere che è molto difficile fare marshmallow grandi e solidi, e il processo di disegno a cristalli è lo stesso. La velocità di rotazione e controllo della temperatura influenzeranno la qualità della colonna di cristallo. Pertanto, più grande è la dimensione, maggiori sono i requisiti di velocità e temperatura. Pertanto, è più difficile realizzare wafer da 12 pollici di alta qualità rispetto a wafer da 8 pollici.

Tuttavia, un'intera colonna di silicio non può essere trasformata in un substrato per la produzione di chip. Per produrre wafer di silicio uno per uno, è necessario tagliare la colonna di silicio orizzontalmente in wafer con un coltello diamantato, e quindi i wafer possono essere lucidati per formare i wafer di silicio necessari per la fabbricazione di chip. Dopo così tanti passaggi, la produzione del substrato del chip è completata. Il passo successivo è impilare le case, cioè la produzione di chip. E come fare le patatine?

Strati di chip impilati

Dopo aver introdotto cosa sono i wafer di silicio, so anche che produrre chip IC è come costruire una casa con blocchi Lego, creando la forma desiderata impilando strato dopo strato. Tuttavia, ci sono alcuni passaggi per costruire una casa, e così sono la produzione di IC. Quali sono i passaggi per fabbricare IC? Questo documento introdurrà il processo di fabbricazione del chip IC.

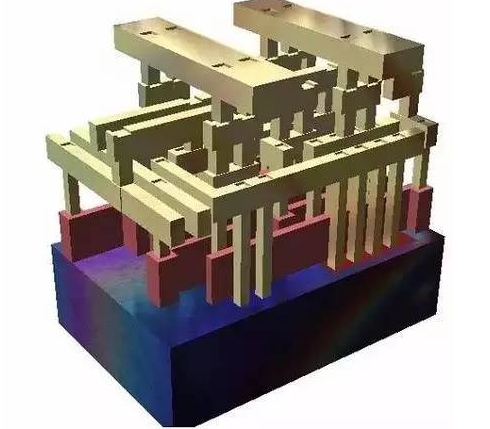

Prima di iniziare, dovremmo prima capire che cosa è il chip IC. IC, il nome completo del circuito integrato, può essere visto dal suo nome che combina i circuiti progettati in modo impilato. Con questo metodo, possiamo ridurre l'area richiesta per collegare il circuito. La figura seguente è un diagramma 3D del circuito IC. Si può vedere che la sua struttura è come travi e colonne di una casa, impilate strato dopo strato, motivo per cui la produzione di IC è paragonata alla costruzione di una casa.

Profilo 3D del chip IC

Dal profilo 3D del chip IC nella figura sopra, la parte blu scuro in basso è il wafer introdotto nell'articolo precedente. Da questa figura, possiamo sapere più chiaramente quanto importante il substrato del wafer gioca nel chip. Per quanto riguarda le parti rosse e kaki, devono essere completate durante la produzione di IC.

Prima di tutto, la parte rossa può essere paragonata alla sala al primo piano di un grattacielo. La sala al primo piano è la porta di una casa. E' dove la gente entra e esce. Di solito ha più funzionalità sotto il controllo del traffico. Pertanto, rispetto ad altri piani, la costruzione sarà più complessa e richiederà più passaggi. Nel circuito IC, questa sala è lo strato del cancello logico, che è la parte più importante dell'intero IC. Una varietà di porte logiche sono combinate per completare il chip IC con funzioni complete.

La parte gialla è come un piano generale. Rispetto al primo piano, non avrà una struttura troppo complessa e ogni piano non cambierà molto durante la costruzione. Lo scopo di questo livello è quello di collegare le porte logiche nella parte rossa insieme. Il motivo per cui sono necessari così tanti strati è che ci sono troppe linee per essere collegate insieme. Quando un singolo livello non può ospitare tutte le linee, è necessario impilare più livelli per raggiungere questo obiettivo. In questo processo, le linee di diversi strati saranno collegate su e giù per soddisfare i requisiti di cablaggio.

Costruzione a strati e struttura strato per strato

Dopo aver conosciuto la struttura di IC, introdurremo come farlo. Immaginate che se vogliamo fare un disegno fine con una bomboletta spray di vernice, dobbiamo tagliare la piastra di copertura della figura e coprirla sulla carta. Poi spruzzare la vernice uniformemente sulla carta. Dopo che la vernice è asciutta, rimuovere l'otturatore. Dopo aver ripetuto questo passaggio, una grafica ordinata e complessa può essere completata. IC di fabbricazione è impilare strato per strato coprendo in modo simile.

Quando si fa IC, può essere semplicemente diviso nei quattro passaggi di cui sopra. Sebbene le fasi di produzione e i materiali utilizzati siano diversi nella produzione effettiva, principi simili sono generalmente adottati. Questo processo è un po 'diverso dalla pittura di vernice. La produzione di IC viene prima rivestita e poi coperta, mentre la pittura viene prima coperta e poi dipinta. Ogni processo è descritto di seguito.

-Spruzzare metallo: cospargere uniformemente il materiale metallico da utilizzare sul wafer per formare una pellicola sottile.

-Rivestimento photoresist: in primo luogo posizionare il materiale photoresist sul wafer, passare attraverso la maschera (il principio della maschera sarà spiegato la prossima volta), colpire il fascio sulla parte indesiderata e distruggere la struttura del materiale photoresist. Quindi, i materiali danneggiati vengono lavati via con prodotti chimici.

Tecnologia di incisione: il wafer di silicio senza protezione fotoresist è inciso dal fascio ionico.

-Rimozione Photoresist: sciogliere il fotoresist rimanente utilizzando la soluzione di rimozione photoresist, in modo da completare un processo.

Infine, molti chip IC saranno completati su un wafer intero. Successivamente, finché i chip IC quadrati completati sono tagliati, possono essere inviati alla fabbrica di imballaggio per l'imballaggio. Che cosa è la fabbrica di imballaggio? Te lo spiego dopo.

Confronto di wafer di varie dimensioni

3, che cosa è il processo di nanofabbricazione?

Samsung e TSMC sono molto caldi nel processo avanzato di produzione di semiconduttori. Entrambi vogliono prendere il comando nella fonderia di wafer per vincere gli ordini. È quasi diventato una disputa tra 14nm e 16nm. Tuttavia, qual è il significato dei due numeri di 14nm e 16nm e a quale parte si riferisce? Quali vantaggi e problemi porterà in futuro dopo aver ridotto il processo? Spiegheremo brevemente il processo nano qui sotto.

Quanto è sottile Nano?

Prima di iniziare, dovremmo prima capire cosa significa nano. Matematicamente, il nanometro è 0,000000001 metri, ma questo è un esempio molto povero. Dopo tutto, possiamo vedere molti zeri solo dopo la virgola decimale, ma non abbiamo una sensazione pratica. Se lo spessore dell'unghia viene confrontato, può essere più evidente.

Se si misura effettivamente con un righello e un misuratore, si può sapere che lo spessore dell'unghia è di circa 0,0001 metri (0,1 mm), cioè, provare a tagliare il lato di un chiodo in 100000 linee, e ogni linea è circa equivalente a 1 nm. Pertanto, potete immaginare quanto sia piccolo 1 nm.

Dopo aver saputo quanto è piccolo nano, dovremmo anche capire l'intenzione di ridurre il processo. Lo scopo principale di ridurre i transistor è quello di inserire più transistor in chip più piccoli, in modo che i chip non diventino più grandi a causa del miglioramento tecnologico; In secondo luogo, può aumentare l'efficienza operativa del processore; Inoltre, riducendo il volume può anche ridurre il consumo energetico; Infine, dopo la riduzione delle dimensioni del chip, è più facile collegarlo al dispositivo mobile per soddisfare le esigenze di leggerezza in futuro.

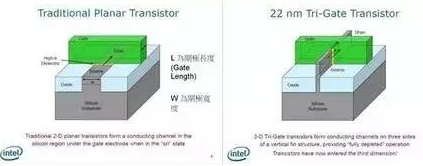

Poi tornate ad esplorare qual è il processo nano. Prendete 14 nm come esempio. Il processo si riferisce al fatto che il cavo più piccolo nel chip può essere di 14 nm. La figura seguente mostra come esempio l'aspetto dei transistor tradizionali. Lo scopo principale di ridurre il transistor è quello di ridurre il consumo energetico, ma quale parte dovrebbe essere ridotta per raggiungere questo scopo?

La L nella figura in basso a sinistra è la parte che ci aspettiamo di ridursi. Riducendo la lunghezza del cancello, la corrente può utilizzare un percorso più breve dall'estremità dello scarico all'estremità della sorgente (se siete interessati, potete usare Google per cercare MOSFET, che vi verrà spiegato in modo più dettagliato).

Inoltre, i computer funzionano su 0 e 1. Come possono i transistor soddisfare questo scopo? Il metodo è quello di giudicare se il transistor ha flusso di corrente. Quando la tensione viene fornita al terminale gate (Green Square), la corrente fluirà dal terminale di scarico al terminale sorgente. Se non viene fornita alcuna tensione, la corrente non fluirà, quindi può rappresentare 1 e 0 (Per quanto riguarda il motivo per cui usiamo 0 e 1 per giudizio, se siete interessati, è possibile controllare l'algebra brin. Usiamo questo metodo per fare computer.)

La riduzione delle dimensioni ha i suoi limiti fisici

Tuttavia, il processo di produzione non può essere ridotto indefinitamente. Quando riduciamo il transistor a circa 20 nm, incontreremo problemi nella fisica quantistica, in modo che il transistor abbia perdite, compensando i benefici ottenuti quando l è ridotto. Come metodo di miglioramento, viene introdotto il concetto di FinFET (tri gate), come mostrato nella figura in alto a destra. Nella precedente spiegazione fatta da Intel, si può sapere che l'introduzione di questa tecnologia può ridurre le perdite causate dai fenomeni fisici.

Ancora più importante, questo metodo può aumentare l'area di contatto tra l'estremità del cancello e lo strato inferiore. Nella pratica tradizionale (sopra a sinistra), la superficie di contatto ha un solo piano, ma dopo aver utilizzato la tecnologia FinFET (tri gate), la superficie di contatto diventerà tridimensionale, che può facilmente aumentare l'area di contatto. In questo modo, l'estremità di scarico della sorgente può essere ridotta mantenendo la stessa area di contatto, che è molto utile per ridurre le dimensioni.

Infine, è il motivo per cui alcune persone dicono che le principali fabbriche dovranno affrontare sfide piuttosto gravi quando entrano nel processo di 10 nm. La ragione principale è che la dimensione di un atomo è di circa 0,1 nm. Nel caso di 10 nm, ci sono solo meno di 100 atomi in una linea, che è abbastanza difficile da fabbricare, e finché c'è un difetto di un atomo, come gli atomi che cadono o impurità nel processo di fabbricazione, ci sarà un fenomeno sconosciuto, che influenzerà la resa del prodotto.

Se non riesci a immaginare la difficoltà, puoi fare un piccolo esperimento. Allineare un 10 con 100 perline sul tavolo * 10 quadrato, e tagliare un pezzo di carta per coprire le perline, poi spennellare le perline successive con un piccolo pennello, e infine fargli formare un 10 * Un rettangolo di 5. In questo modo possiamo conoscere le difficoltà incontrate dalle grandi fabbriche e quanto sia difficile raggiungere questo obiettivo.

Poiché Samsung e TSMC completeranno la produzione di massa di 14 nm e 16 nm FinFET nel prossimo futuro, entrambi vogliono competere per l'OEM del chip iPhone di prossima generazione di Apple. Vedremo una concorrenza commerciale abbastanza meravigliosa e otterremo più telefoni cellulari leggeri e a risparmio energetico. Grazie ai benefici apportati dalla legge di Moore.

4, dirvi che cosa è l'incapsulamento

Imballaggio, protezione finale e integrazione del chip IC

Dopo un lungo processo, dalla progettazione alla produzione, abbiamo finalmente ottenuto un chip IC. Tuttavia, un chip è abbastanza piccolo e sottile. Se non è protetto all'esterno, sarà facilmente graffiato e danneggiato. Inoltre, poiché le dimensioni del chip sono piccole, non sarà facile posizionarlo manualmente sul circuito stampato senza un guscio più grande. Pertanto, questa carta descriverà e introdurrà l'imballaggio successivo.

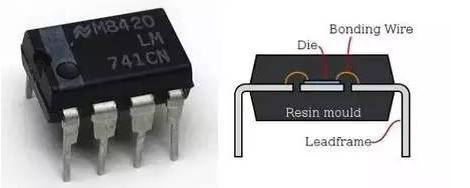

Attualmente, ci sono due pacchetti comuni, uno è il pacchetto dip comune nei giocattoli elettrici, che sembra un centopiede in nero, e l'altro è il pacchetto BGA comune quando si acquista CPU in scatola. Come per altri metodi di imballaggio, PGA (pin grid array) utilizzato dalle prime CPU; Pin grid array) o migliorato QFP (plastica quadrato flatpack) di dip. Poiché ci sono così tanti metodi di imballaggio, gli imballaggi dip e BGA saranno introdotti di seguito.

Imballaggio tradizionale, durevole

La prima cosa da introdurre è il doppio pacchetto inline; Dip), come si può vedere dalla figura sottostante, il chip IC con questo pacchetto sembrerà un centopiede nero ai piedi della connessione a doppia fila, il che è impressionante. Questo metodo di imballaggio è la prima tecnologia di imballaggio IC, che ha il vantaggio di basso costo ed è adatto per piccoli chip senza troppi fili. Tuttavia, poiché la maggior parte di loro sono di plastica, l'effetto di dissipazione del calore è povero, che non può soddisfare i requisiti dei chip ad alta velocità attuali. Pertanto, la maggior parte dei chip che utilizzano questo pacchetto sono chip durevoli, come op741 nella figura sottostante, o chip IC con meno requisiti per la velocità di funzionamento, chip più piccoli e meno fori di connessione.

Vista della sezione trasversale dell'amplificatore

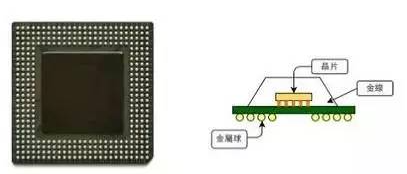

Per quanto riguarda gli imballaggi a griglia sferica (BGA), rispetto al dip, il volume di imballaggio è più piccolo e può essere facilmente inserito in dispositivi più piccoli. Inoltre, poiché il perno si trova sotto il chip, può ospitare più perni metallici che immersione, che è abbastanza adatto per chip che richiedono più contatti. Tuttavia, questo metodo di imballaggio ha costi elevati e metodo di connessione complesso, quindi è utilizzato principalmente in prodotti con prezzo unitario elevato.

Il diagramma schematico di BGA utilizzando l'imballaggio flip chip

Con l'ascesa dei dispositivi mobili, le nuove tecnologie sono balzate sul palco

Tuttavia, l'utilizzo di questi metodi di imballaggio consumerà un volume considerevole. Ad esempio, i dispositivi mobili e i dispositivi indossabili ora richiedono una varietà di componenti. Se ogni componente è incapsulato in modo indipendente, consumerà molto spazio da combinare. Pertanto, ci sono due metodi per soddisfare i requisiti di riduzione del volume, vale a dire SOC (sistema su chip) e SIP (sistema in pacchetto).

All'inizio dell'ascesa degli smartphone, il termine SOC può essere trovato nelle principali riviste finanziarie. Tuttavia, cos'è SOC? In breve, è quello di integrare l'IC con diverse funzioni in un chip. Questo metodo non solo può ridurre il volume, ma anche ridurre la distanza tra i diversi IC e migliorare la velocità di calcolo del chip. Per quanto riguarda il metodo di fabbricazione, è quello di mettere insieme diversi IC nella fase di progettazione IC e quindi fare una maschera attraverso il processo di progettazione descritto in precedenza.

Tuttavia, SOC non presenta solo vantaggi. La progettazione di un SOC richiede una notevole cooperazione tecnica. Quando i chip IC sono imballati, sono protetti da imballaggi esterni e la distanza tra IC e IC è lontana, quindi non c'è interferenza reciproca. Tuttavia, quando tutti i IC sono confezionati insieme, è l'inizio dell'incubo. La fabbrica di progettazione IC dovrebbe passare dall'IC di progettazione semplice originale a un IC che comprende e integra varie funzioni, aumentando il carico di lavoro degli ingegneri. Inoltre, ci saranno molte situazioni, come il segnale ad alta frequenza del chip di comunicazione può influenzare l'IC di altre funzioni.

Inoltre, SOC ha anche bisogno di ottenere l'autorizzazione IP (proprietà intellettuale) da altri produttori per mettere componenti progettati da altri in SOC. Poiché la fabbricazione di SOC richiede i dettagli di progettazione dell'intero IC per fare una maschera completa, che aumenta anche il costo di progettazione di SOC. Alcune persone possono chiedere perché non progettare uno da soli? Poiché progettare vari IC richiede un sacco di conoscenze relative al IC, solo le aziende con un sacco di soldi come Apple possono avere un budget per reclutare ingegneri di alto livello da aziende ben note per progettare un IC nuovo di zecca. È più conveniente cooperare e autorizzare che sviluppare un proprio IC.

Compromesso, SIP appare

In alternativa, SIP è salito sul palco dell'integrazione dei chip. Diverso dal SOC, acquista vari IC e li incapsula per l'ultima volta, eliminando così la fase di autorizzazione IP e riducendo notevolmente i costi di progettazione. Inoltre, poiché sono IC indipendenti, il grado di interferenza tra loro è notevolmente ridotto.

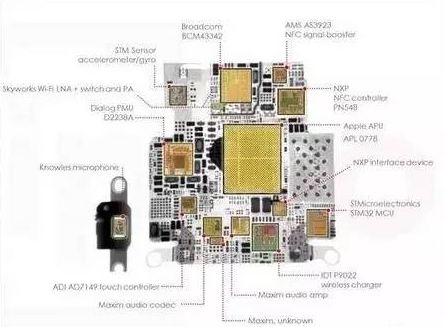

Apple Watch utilizza la tecnologia SIP per confezionare

I prodotti più famosi che utilizzano la tecnologia SIP sono Apple Watch. Poiché lo spazio interno dell'orologio è troppo piccolo, non può adottare la tecnologia tradizionale e il costo di progettazione di SOC è troppo alto, SIP è diventato la prima scelta. Con la tecnologia SIP, non solo può ridurre il volume, ma anche ridurre la distanza tra ogni IC, che è diventato un compromesso fattibile. La figura seguente è il diagramma della struttura del chip Apple watch. Si può vedere che un numero considerevole di IC sono inclusi in esso.

Schema di configurazione interna del chip S1

Dopo che l'imballaggio è completato, è necessario entrare nella fase di prova. In questa fase è necessario verificare se il IC confezionato funziona normalmente. Dopo che è corretto, può essere spedito all'impianto di assemblaggio per fare i prodotti elettronici che vediamo. Finora, l'industria dei semiconduttori ha completato l'intero compito di produzione.