La progettazione del segnale LVDS sulla scheda PCB non è solo un segnale differenziale, ma anche un segnale digitale ad alta velocità. Pertanto, indipendentemente dal fatto che il mezzo di trasmissione LVDS utilizzi cavi o cavi per schede PCB, occorre adottare misure per evitare che il segnale si rifletta sul terminale multimediale e ridurre le interferenze elettromagnetiche per garantire l'integrità del segnale. Finché consideriamo questi elementi durante il cablaggio, progettare circuiti differenziali ad alta velocità non è molto difficile. Quanto segue introduce brevemente i punti di progettazione del segnale LVDS sulla scheda PCB: 2.1 Layout in una scheda multistrato I circuiti stampati con segnali LVDS sono generalmente disposti come una scheda multistrato. Poiché il segnale LVDS è un segnale ad alta velocità, lo strato adiacente dovrebbe essere uno strato di terra per proteggere il segnale LVDS per evitare interferenze. Per schede a bassa densità, se le condizioni fisiche lo consentono, posizionare segnali LVDS e altri segnali su strati diversi. Ad esempio, in una scheda a quattro strati, gli strati di solito possono essere disposti come segue: strato di segnale LVDS, strato di terra, strato di potenza e altri livelli di segnale. 2.2 Calcolo e controllo dell'impedenza del segnale LVDS. L'oscillazione di tensione del segnale LVDS è solo 350mV, che è adatto per il funzionamento del segnale differenziale guidato dalla corrente. Per garantire che il segnale non sia influenzato dal segnale riflesso quando si propaga nella linea di trasmissione, il segnale LVDS richiede che l'impedenza della linea di trasmissione sia controllata e l'impedenza differenziale è solitamente di 100 +/- 10Ω. La qualità del controllo dell'impedenza influisce direttamente sull'integrità e sul ritardo del segnale.

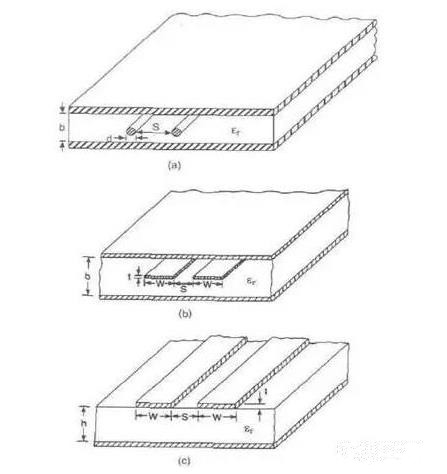

1. Come controllare la sua impedenza della scheda PCB? 1.1 Determinare la modalità di cablaggio, i parametri e il calcolo dell'impedenza. LVDS è diviso in modo differenziale della linea microstrip dello strato esterno e modo differenziale della linea della striscia dello strato interno. L'impedenza può essere calcolata impostando i parametri ragionevolmente e utilizzando software correlati. Attraverso il calcolo, il valore di impedenza è direttamente proporzionale allo spessore dello strato isolante e inversamente proporzionale alla costante dielettrica, allo spessore e alla larghezza del filo.1.2 Seguire il principio delle linee parallele equidistanti e dell'accoppiamento stretto. Dopo aver determinato la larghezza e la spaziatura della linea, seguire rigorosamente la larghezza e la spaziatura della linea calcolata durante il routing, e la spaziatura tra le due linee deve essere sempre costante, cioè devono essere parallele (è possibile posizionare l'immagine). Allo stesso tempo, il principio di accoppiamento stretto viene osservato quando si calcola la larghezza e la spaziatura della linea, cioè la spaziatura della coppia differenziale è inferiore o uguale alla larghezza della linea. Quando le due linee differenziali del segnale sono molto vicine, la direzione di trasmissione corrente è opposta, i campi magnetici si annullano a vicenda, i campi elettrici sono accoppiati tra loro e la radiazione elettromagnetica è molto più piccola. Inoltre, i due fili devono essere sullo stesso strato per evitare il cablaggio stratificato.Perché nell'elaborazione effettiva della scheda PCB, il grado di laminazione tra le pile è molto inferiore alla precisione di incisione dello stesso strato e la perdita dielettrica durante il processo di laminazione non può garantire che la distanza tra le linee differenziali è uguale allo spessore del dielettrico intercalare, che causerà il cambiamento di impedenza differenziale della coppia differenziale tra gli strati.

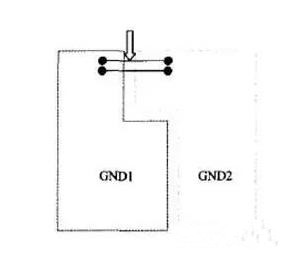

1.3 Andare corto e dritto. Al fine di garantire la qualità del segnale, la traccia differenziale della coppia LVDS dovrebbe essere il più breve e diritta possibile, ridurre il numero di vias nel cablaggio ed evitare cavi differenziali troppo lunghi e troppi giri. Prova a usare 45° o archi agli angoli. Evitare giri di 90°. Non vi sono restrizioni alla selezione dei metodi di routing delle coppie LVDS tra diverse coppie di linee differenziali. La linea di microstrip e la linea di striscia possono essere utilizzate, ma va notato che c'è un buon piano di riferimento. La distanza tra le diverse linee differenziali non dovrebbe essere troppo piccola e dovrebbe essere almeno 3-5 volte la distanza tra le linee differenziali. Se necessario, aggiungere l'isolamento del foro di terra tra le diverse coppie di linee differenziali per evitare il cross talk reciproco. Tenere i segnali LVDS lontani da altri segnali il più possibile. I segnali differenziali LVDS non possono essere suddivisi tra piani. Sebbene i due segnali differenziali siano percorsi di ritorno l'uno per l'altro, la segmentazione trasversale non interromperà il ritorno del segnale, ma la linea di trasmissione attraverso la segmentazione causerà discontinuità in impedenza a causa della mancanza di un piano di riferimento (come mostrato in figura, dove GND1 e GND2 sono adiacenti al piano di terra LVDS). La distanza tra la resistenza corrispondente dell'estremità ricevente e il perno ricevente deve essere il più vicino possibile. Allo stesso tempo, la precisione della resistenza di corrispondenza deve essere controllata. Per la topologia punto-punto, l'impedenza della traccia è solitamente controllata a 100Ω, ma la resistenza corrispondente può essere regolata in base alla situazione reale. Il grado di resistenza è 1%-2%. Perché secondo l'esperienza, il disallineamento dell'impedenza del 10% produrrà una riflessione del 5%.

2. Analisi di simulazione del segnale LVDS serialeQuanto sopra analizza le questioni che devono essere prestate attenzione quando si progettano segnali LVDS. Sebbene le regole di cui sopra siano generalmente seguite durante la progettazione del PCB, al fine di migliorare la correttezza e l'accuratezza della progettazione, la simulazione completa del segnale del PCB deve essere effettuata attraverso la simulazione. Ottenere le forme d'onda del segnale crosstalk, delay, riflessione e pattern degli occhi, in modo da raggiungere l'obiettivo di progettazione corretta. Il processo di simulazione del problema di integrità del segnale è prima di stabilire il modello di simulazione dei componenti e quindi eseguire la pre-simulazione per determinare i parametri e i vincoli del processo di cablaggio. La fase di realizzazione fisica è progettata secondo i vincoli e la post-simulazione viene eseguita per verificare se il progetto soddisfa i requisiti di progettazione. La natura del modello nell'intero processo influisce direttamente sui risultati della simulazione e i metodi di analisi della simulazione utilizzati nelle fasi di pre-simulazione e post-simulazione sono anch'essi critici per i risultati della simulazione, e in questo progetto viene utilizzato un più alto grado di modello speziato. Quanto segue è una combinazione di progetti reali per illustrare il processo di implementazione della simulazione in questo progetto.2.1 Impostazione dello stack di schede PCB Dall'analisi di cui sopra, è noto che l'impostazione di impilamento della scheda PCB è strettamente correlata all'accoppiamento del segnale e al calcolo dell'impedenza. Pertanto, la progettazione di impilamento deve essere eseguita prima della progettazione della scheda PCB e quindi il calcolo dell'impedenza del segnale.2.2 Impostare il valore di tensione DC Questo passo consiste principalmente nel specificare il valore di tensione DC per determinate reti specifiche (di solito alimentazione a terra, ecc.), determinare la tensione DC da applicare alla rete ed eseguire la simulazione EMI richiede la determinazione di uno o più pin sorgente di tensione. Questi valori di tensione includono Le informazioni sulla tensione di riferimento utilizzate dal modello nel processo di simulazione sono descritte.2.3 Impostazioni del dispositivoDurante la simulazione allegro, allegro divide i dispositivi in tre categorie: IC, connettori e dispositivi discreti (condensatori di resistenza, ecc.), allegro assegnerà attributi di simulazione ai pin del dispositivo in base al tipo di dispositivo, dispositivi discreti e pin del connettore L'attributo è UPSPEC, e l'attributo pin di IC può essere IN, OUT, BI, ecc.2.4 Assegnazione modelloI principali modelli utilizzati nel processo di simulazione della scheda PCB ad alta velocità a livello di scheda sono modelli di dispositivo e modelli di linea di trasmissione. Il modello del dispositivo è generalmente fornito dal produttore del dispositivo. Nel segnale seriale ad alta velocità, quello che adottiamo è il modello SPICE con maggiore precisione per portare avanti l'analisi di simulazione. Il modello della linea di trasmissione è formato attraverso la modellazione software di simulazione. Quando il segnale viene trasmesso, la linea di trasmissione renderà evidente il problema di integrità del segnale, quindi la capacità del software di simulazione di modellare la linea di trasmissione influisce direttamente sul risultato della simulazione.2.5 Ispezione SI La funzione SI Audit viene utilizzata per verificare se una particolare rete o un gruppo di reti può essere estratta per l'analisi. Generalmente, è per impostare la rete ad alta velocità a cui dobbiamo prestare attenzione.Questo design si concentra principalmente sui segnali seriali LVDS.2.6 Estrarre la topologia della rete Estrarre la struttura topologica del segnale di interesse dalla scheda PCB, generalmente compreso l'estremità motrice e l'estremità ricevente, così come la linea di trasmissione e i relativi resistori e condensatori corrispondenti. Si può vedere dalla topologia che la rete passa attraverso quei percorsi, che causeranno l'influenza della trasmissione del segnale. Questo articolo prende solo il diagramma topologico di rete di uno dei segnali come esempio: come mostrato in Figura 4:2.7 Visualizza forma d'onda Dopo aver impostato i passaggi correlati sopra, la simulazione può essere eseguita. Allegro può eseguire la simulazione di riflessione del segnale e la simulazione di crosstalk, e la linea differenziale deve anche eseguire l'analisi del diagramma oculare. Naturalmente, la simulazione è anche divisa in pre-simulazione e post-simulazione. Quando si utilizza allegro per progettare la scheda PCB, è necessario modificare la progettazione in tempo reale con i risultati della simulazione per soddisfare i requisiti. Poiché il processo di simulazione è complicato e i passaggi sono ingombranti, non li descriverò uno per uno. Ci sono due punti a cui prestare attenzione nel cablaggio della coppia differenziale. Uno è che la lunghezza delle due linee dovrebbe essere il più lunga possibile, e la lunghezza uguale è quella di garantire che i due segnali differenziali siano mantenuti opposti in ogni momento. Polarità per ridurre i componenti in modalità comune. L'altro è che la distanza tra le due linee (questa distanza è determinata dall'impedenza differenziale) deve essere sempre mantenuta costante, cioè deve essere mantenuta parallela. Ci sono due modi paralleli, uno è che i due fili corrono sullo stesso lato-by-side, e l'altro è che i due fili corrono su due strati adiacenti sopra e sotto (sopra-sotto). Generalmente, il primo ha più implementazioni affiancate. L'equidistanza è principalmente per garantire la stessa impedenza differenziale tra i due e ridurre la riflessione. Il metodo di cablaggio della coppia differenziale dovrebbe essere vicino e parallelo in modo appropriato. La cosiddetta prossimità appropriata è perché questa distanza influenzerà il valore dell'impedenza differenziale, che è un parametro importante per la progettazione di coppie differenziali. La necessità di parallelismo è anche di mantenere la coerenza dell'impedenza differenziale. Se le due linee sono improvvisamente lontane e vicine, l'impedenza differenziale sarà incoerente, che influenzerà l'integrità del segnale e il ritardo di temporizzazione. Dal grafico simulato del parametro S, l'impedenza differenziale della coppia differenziale e l'integrità del segnale possono essere analizzate. Le forme d'onda chiave di simulazione del segnale in questo disegno sono fornite di seguito per spiegazione. Si può vedere dalla leggenda della simulazione Figura 5 che l'indice di degradazione di S11 nel dominio di frequenza di 0-3.0GHz è: