Mentre l'industria informatica si sposta verso convertitori DC-DC in grado di erogare fino a 200A a 1V, Scheda PCB Le tecniche di layout devono soddisfare i requisiti di questo stimolante convertitore emergente. Per confrontare gli effetti di vari difetti di cablaggio, Ci concentriamo sugli effetti delle induttanze parassitarie nel circuito, in particolare quelli associati alla fonte, scarico, e gate of switching MOSFET. Abbiamo costruito un Scheda PCB per testare un convertitore DC-DC che prende in 12V DC e lo converte in 1.3V e uscite fino a 20A. Usiamo una scheda plug-in per il montaggio e possiamo cambiare l'induttanza ad ogni elettrodo MOSFET singolarmente o contemporaneamente in qualsiasi momento. Abbiamo scelto di utilizzare il valore di induttanza come percentuale dell'induttanza complessiva di una scheda da 2 pollici appositamente progettata, piuttosto che un valore reale perché il conduttore conosce solo la lunghezza di una particolare traccia e non necessariamente il valore della sua induttanza.

Progettazione della prova

Usiamo l'efficienza del convertitore per misurare l'efficacia di queste induttanze parassitarie. Questo perché l'efficienza è una misura standard delle prestazioni del convertitore DC-DC. La prova è divisa nelle seguenti parti: regolare il coefficiente proporzionale di ogni valore di induttanza dello scarico, della sorgente e del cancello MOSFET e osservare l'effetto sul raddrizzatore sincrono misurando l'efficienza di conversione. Attraverso la combinazione di due di quanto sopra, per capire la relazione tra di loro. Il bordo della prova di induttanza ha un'induttanza di 43nH ed è tipicamente impostato a 0%, 25%, 50% e 100%. Nei nostri esperimenti, la resistenza parassitaria sul bordo di prova dell'induttanza ha poco effetto e può essere ignorata. Poiché gli effetti deleteri delle induttanze parassitarie dipendono dalla frequenza, abbiamo sperimentato a tre frequenze di commutazione preimpostate: 300kHz, 600kHz e 1MHz. Questo ci permette di vedere quanto sarà importante per il progetto passare dalle normali frequenze di commutazione a frequenze più alte in futuro. Sappiamo tutti che nei circuiti di alimentazione, la lunghezza di tutte le tracce deve essere mantenuta breve per evitare tensione e squillo di corrente, ridurre l'EMI complessivo della scheda ed evitare di influenzare negativamente i componenti "più stabili" del circuito (soprattutto per i circuiti di controllo analogici e relativi componenti). Inoltre, il materiale di riferimento mostra che l'induttanza sorgente del MOSFET di controllo ha un effetto non lineare sull'aumento del tempo di caduta della corrente sorgente, con conseguente maggiore dissipazione di potenza e minore efficienza di conversione. Oltre ai fenomeni di cui sopra, l'induttanza della sorgente può anche causare squillo al nodo di commutazione.

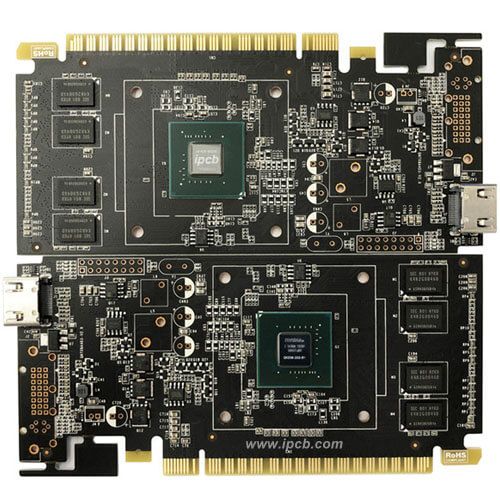

Circuiti di prova e circuiti stampati

Il circuito utilizzato è una topologia di rettifica sincrona che opera in un circuito aperto. Questo per escludere qualsiasi impatto che il loop di controllo potrebbe avere sulle prestazioni del circuito e permetterci di concentrarci sull'efficienza di conversione di potenza, in particolare sulle prestazioni MOSFET. Sappiamo che le condizioni di elevata induttanza possono causare un forte squillo, specialmente al nodo di commutazione. Selezionare IC driver gate che possono tollerare questo squillo senza effetti negativi. Questo circuito stampato a quattro strati utilizza due once di materiale di rame e i due strati interni sono piani di terra e potenza. Tutte le regole di buon cablaggio dovrebbero essere rispettate durante il cablaggio.

Effetto dell'induttanza del cancello

L'induttanza del cancello ha poco effetto sull'efficienza ad una frequenza di commutazione di 300kHz. A una frequenza di commutazione di 600kHz, l'effetto dell'induttanza del cancello è molto più pronunciato, con una variazione dell'1,2% nell'efficienza a 20A. A 1MHz, la degradazione in efficienza scompare quasi completamente. Non abbiamo indagato questo motivo e possiamo indovinare che c'è una probabilità del 50% che il fattore di risonanza compenserà la sua perdita. Il fenomeno di risonanza dell'azionamento del cancello MOSFET dovrebbe essere ulteriormente indagato. Osserviamo che l'induttanza del cancello ha poco effetto sull'efficienza del controllo e dei MOSFET sincroni.

Effetto dell'induttanza della sorgente

L'induttanza della sorgente ha un effetto più pronunciato sull'efficienza. In alcuni casi, abbiamo dovuto interrompere il test prima di raggiungere la corrente perché la temperatura del MOSFET era superiore a 130°C. La Figura 5 mostra i risultati dello studio MOSFET di controllo. Un esame più attento di questi risultati mostra che ad una frequenza di 300kHz e un'induttanza del 100%, il convertitore DC-DC non può funzionare a 20A perché la temperatura del MOSFET supera 130°C. Lo stesso può essere trovato al 50% di induttanza, 600kHz e 1MHz. Si osserva che la degradazione dell'efficienza dovuta all'induttanza della sorgente è più grave che senza induttanza della sorgente. Quando l'induttanza è 50% e la corrente è 15A, l'efficienza è ridotta del 7% anche alla frequenza di commutazione di 300 kHz. Quando l'induttanza è 100%, l'efficienza si deteriora all'11%. Alle frequenze di commutazione di 600kHz e 1MHz, l'effetto è più pronunciato e la degradazione dell'efficienza è più grave che senza l'induttanza della sorgente. Chiaramente, anche un'induttanza a bassa sorgente riduce l'efficienza, specialmente per le frequenze di commutazione � 600kHz.

Effetto dell'induzione del drenaggio

L'induttanza di drenaggio può causare un forte squillo che può essere sufficiente a causare il crollo del MOSFET in condizioni estreme (Figura 3). Essa incide anche negativamente sull'efficienza. L'efficienza è una funzione della corrente di carico e drena l'induttanza a frequenze diverse. Inoltre, si possono osservare i seguenti risultati: quando la corrente è 15A, a 300kHz e 50% induttanza, dobbiamo interrompere il test perché la temperatura del MOSFET supera 130â. Alla stessa frequenza, 100% induttanza, non abbiamo potuto ottenere alcuna lettura perché il suono era troppo grave. A 300kHz, 12A, 50% dell'induttanza di scarico è 7% meno efficiente dello 0%. A causa dell'alta temperatura del MOSFET, il test non può essere eseguito sopra 15A. A 600kHz, 12.5A, 50% dell'induttanza di scarico è 8.5% meno efficiente dello 0%. Poiché la temperatura del MOSFET è troppo alta, il test non può essere eseguito sopra 12.5A. A 1MHz, il test non può essere eseguito sopra 5A a causa dell'alta temperatura del MOSFET.

Effetto dell'induttanza gate-source

Una maggiore induttanza della sorgente ridurrà significativamente l'efficienza. È stata dimostrata una dipendenza fondamentale dell'efficienza dall'induttanza del cancello. Quando combinato con una piccola induttanza di sorgente, il quadro generale diventa abbastanza chiaro - un'induttanza di gate più grande comporta necessariamente una maggiore perdita di potenza. L'interpretazione di questo risultato richiede ulteriori studi. Ora possiamo affermare che, entro valori ragionevoli di induttanza per la scheda, le induttanze di scarico e sorgente devono essere ridotte per garantire un'elevata efficienza del convertitore. La simulazione dà i seguenti risultati: Le induttanze gate e source risuonano con la capacità gate-source del MOSFET. Quando l'HS-FET spegne la sorgente del gate, il condensatore scarica attraverso questi percorsi induttivi. Dopo che il MOSFET è spento, l'induttanza costringerà la corrente del gate a continuare a fluire e invertire la capacità della sorgente del gate. Questa carica scaricherà nuovamente nello stesso modo e invertirà la tensione gate-source del HS-FET. A seconda del dip, l'HS-FET può riaccendersi con un enorme cortocircuito. L'effetto diventa grave a tali induttanze elevate del cancello. In alcuni casi, anche un secondo effetto di cortocircuito può essere visto. Come parte di questo circuito risonante, l'induttanza della sorgente può anche agire in un secondo modo. Quando si verifica una corrente di cortocircuito, l'induttanza della sorgente limita il di/dt (tasso di cambiamento della corrente nel tempo) della corrente di cortocircuito, limitando così le perdite. L'induttanza della sorgente provoca anche un feedback negativo alla tensione gate-source e limita i cortocircuiti. Questi effetti si verificano soprattutto quando le induttanze parassitarie sono elevate. Per l'alta efficienza, questo effetto dovrebbe essere evitato dalla progettazione, cioè l'induttanza del cancello deve essere attentamente progettata per minimizzarla.

Effetto della sorgente HS - sorgente LS induttanza

Abbiamo studiato l'effetto della posizione dell'induttanza della fonte parassitaria sull'efficienza. Di conseguenza, il FET di controllo avrà un effetto maggiore sulla sua efficienza rispetto al FET sincrono nella stessa quantità di ciclo di induttanza della sorgente parassitaria. La ragione di questo fenomeno è che il FET di controllo a commutazione lenta provoca ulteriori perdite di commutazione perché il VDS del FET di controllo è superiore a quello del FET sincrono (la caduta di tensione in avanti del FET sincrono è piccola) durante il processo di conversione. Inoltre, il feedback dell'induttanza parassitaria alla tensione FET gate-drain ha un impatto significativo sulla corrente di perdita generale HS-FET. A confronto, l'effetto dell'induttanza parassitaria sulla corrente di perdita LS-FET è solo parziale, poiché può essere bypassato dal diodo del corpo del FET sincrono.

Effetti dei MOSFET paralleli

Quando i MOSFET sono collegati in parallelo, è improbabile che ogni singolo loop MOSFET abbia gli stessi parassiti in molti casi. Abbiamo studiato l'effetto dell'induttanza aggiuntiva nel ciclo di scarico MOSFET sull'efficienza. Mostriamo sperimentalmente l'effetto dannoso dell'induttanza parassitaria sull'efficienza di commutazione dei MOSFET nei convertitori DC-DC. Le conclusioni sono le seguenti: l'effetto dell'induttanza nel circuito sorgente è grave, seguita da un'induttanza simile nel circuito di scarico. Nel nostro paniere, Non abbiamo trovato effetti gravi relativi all'induttanza del circuito gate. La riduzione dell'efficienza è strettamente correlata alla frequenza di commutazione del convertitore. La riduzione dell'efficienza ha molto a che fare con la corrente di carico. In presenza di induttanze parassitarie nei circuiti sorgente e scarico, maggiore è la corrente di carico, maggiore è il calo dell'efficienza. Nelle attuali applicazioni dei convertitori DC-DC, particolare attenzione deve essere prestata durante l'instradamento del PCB del sistema di alimentazione, soprattutto intorno ai MOSFET di commutazione. Uno dei vantaggi dell'utilizzo di una scheda multistrato è quello di ridurre la resistenza parassitaria e l'induttanza affondando più corrente possibile negli strati. Ciò riduce le perdite resistive e le perdite dovute all'induttanza parassitaria. Nella progettazione di convertitori DC-DC ad alta frequenza, ci sono molti problemi di induttanza parassitaria associati ai circuiti di sorgente e scarico. Il primo è l'induttanza del pacchetto, ed è possibile utilizzare i pacchetti a bassa induttanza recentemente introdotti per la commutazione dei MOSFET. Il secondo elemento è l'induttanza parassitaria del Scheda PCB, che devono essere controllati utilizzando un multistrato Scheda PCB e riducendo l'induttanza della traccia. Ciò consente ai progettisti di utilizzare meno condensatori per una risposta dinamica più rapida e progetti ad alta frequenza di successo. Induttanze parassite che non possono essere evitate per progettazione devono essere spostate nel ciclo sincrono FET perché l'induttanza nel FET sincrono ha un effetto minore sull'efficienza complessiva rispetto all'induttanza nel ciclo di controllo FET. Nota: A cicli di lavoro ridotti, La resistenza parassitaria nel ciclo sincrono FET può ridurre significativamente l'efficienza. Complex trade-offs need to be made in the design (trace width, spessore del rame, intervallo effettivo del ciclo, pregiudizio, ecc.). Evitare MOSFET paralleli. Il modo per sostituire MOSFET in parallelo è quello di aggiungere fasi aggiuntive o utilizzare MOSFET migliori. Se il parallelismo è inevitabile, per MOSFET paralleli, la simmetria elettrica deve essere garantita nella progettazione per ottenere la stessa distribuzione della corrente e lo stesso tempo di commutazione sul Scheda PCB.