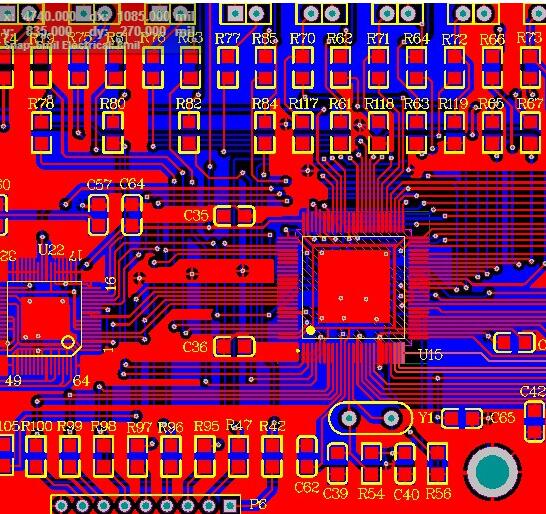

Come ridurre i vuoti di saldatura e i difetti di vari chip IC sui circuiti stampati PCBA Dopo che la saldatura dei prodotti elettronici hardware PCBA è introdotta nel processo senza piombo, a causa delle caratteristiche della saldatura senza piombo, come alto punto di fusione, scarsa bagnabilità, finestra di processo stretta, ecc., il processo di saldatura ha difetti e difetti unici di saldatura senza piombo, come perle di stagno e giunti di saldatura. Durezza, saldatura mancante, piccola latta e vuoti. È noto che si formano vuoti quando si saldano componenti di grandi dimensioni piatte e basse altezze, come componenti QFN. L'uso di questi tipi di componenti è in aumento. Per soddisfare gli standard IPC, la formazione di vuoti fa sentire un mal di testa molti progettisti di circuiti stampati PCB, fonderie EMS di saldatura PCBA e personale di controllo qualità. I parametri per ottimizzare le prestazioni di vuoto sono solitamente la composizione chimica della pasta di saldatura, il profilo della temperatura di riflusso, il rivestimento del substrato e dei componenti e il design ottimale del pad e del modello di stencil SMT. Tuttavia, in pratica, modificare questi parametri ha evidenti limiti. Nonostante molti sforzi per ottimizzare, ma spesso vedono ancora livelli di vuoto troppo alti. La causa principale dei vuoti di saldatura è che l'aria o il gas volatile avvolto nella pasta di saldatura non viene completamente scaricato dopo la fusione della pasta di saldatura. I fattori che influenzano includono materiale della pasta di saldatura, forma di stampa della pasta di saldatura, volume di stampa della pasta di saldatura, temperatura di riflusso, tempo di riflusso, dimensione della saldatura, struttura Attendere. Tipi di tecnologia di imballaggio del chip IC: LGA, PGA, BGA

Come ingegnere SMT nel settore della produzione elettronica, se non padroneggiate il processo di assemblaggio superficiale SMT, è difficile analizzare e migliorare il processo. Prima di comprendere il processo di assemblaggio, è necessario padroneggiare la struttura di imballaggio dei componenti di montaggio superficiale. La struttura del pacchetto e il processo di assemblaggio sono analizzati in dettaglio. Il pacchetto del componente del montaggio superficiale (SMD) è l'oggetto del montaggio superficiale. Comprendere la struttura dei pacchetti di SMD è di grande importanza per l'ottimizzazione del processo SMT. La struttura del pacchetto di SMD è la base della progettazione del processo. Pertanto, qui non siamo classificati dal nome della confezione ma dalla struttura del perno o dall'estremità della saldatura. Secondo questa divisione, i pacchetti SMD includono principalmente componenti del chip (Chip), pin a forma di J, pin a forma di L, BGA, BTC e castello. Introduzione del pacchetto BGA:1. Il pacchetto BGA (Ball Grid Array), secondo la sua struttura, comprende principalmente il pacchetto di plastica BGA (P-BGA), flip-chip BGA (F-BGA), nastro trasportatore BGA (T-BGA) e ceramica BGA (C-BGA) ) Quattro categorie. Il dispositivo terminale di saldatura inferiore BTC sul bordo stradale è ampiamente usato, come dispositivi speciali come dispositivi a sfera (BGA/CSP/WLP/POP) e QFN/LLP. Il pacchetto BTC è elencato nel pacchetto BTC elencato in IPC-7093 Ci sono QFN (pacchetto Quad Flat No-Lead), SON (SmallOutline No-Lead), DFN (Dual Flat No-Lead), LGA (land Grid Array), MLFP (Micro Leadframe Package). Tra questi, QFN è un pacchetto senza piombo, che è quadrato o rettangolare. C'è un grande pad esposto al centro del fondo del pacchetto per la conduzione del calore e il collegamento elettrico viene raggiunto attraverso i grandi pad alla periferia del pacchetto. Poiché non c'è piombo, l'area di montaggio è più piccola di QFP e l'altezza è inferiore a QFP. Insieme alle eccezionali prestazioni elettriche e termiche, questo tipo di pacchetto è sempre più utilizzato nell'industria elettronica. Il controllo del vuoto del pad del dissipatore di calore QFN è uno dei problemi del processo di saldatura QFN ed è anche uno dei problemi nel settore. Poiché i pacchetti di piccole dimensioni sono più capaci di trasportare chip ad alta potenza, i pacchetti di componenti terminali inferiori come QFN stanno diventando sempre più importanti. Poiché i requisiti per le prestazioni di affidabilità continuano ad aumentare, è essenziale ottimizzare le prestazioni termiche ed elettriche per i componenti di gestione dell'energia in pacchetti come QFN. Inoltre, per massimizzare la velocità e le prestazioni RF, ridurre i vuoti è molto importante per ridurre il percorso corrente del circuito. Poiché le dimensioni del pacchetto si restringono e il fabbisogno energetico aumenta, il mercato richiede la riduzione dei vuoti sotto le pastiglie termiche dei componenti QFN. Pertanto, è necessario valutare i fattori chiave di processo che generano vuoti e progettare la soluzione migliore. Il pacchetto QFN ha eccellenti prestazioni termiche, principalmente a causa del pad di dissipazione del calore di grande area nella parte inferiore del pacchetto. Al fine di condurre efficacemente il calore dal chip al PCB, il fondo del PCB deve essere progettato con i corrispondenti pad di dissipazione del calore e via di dissipazione del calore. Il pad dissipatore del calore fornisce un'area di saldatura affidabile e i vias forniscono un modo per dissipare il calore. Pertanto, quando i pad esposti sul fondo del chip vengono saldati ai pad termici sul PCB, il gas nella pasta di saldatura sui vias termici e i pad di grandi dimensioni traboccano, con conseguente alcuni fori di gas. Per il processo smt In termini di grandi cavità, è quasi impossibile eliminare questi pori. L'unico modo per ridurre i pori è minimizzarli. Il nome completo di LGA è "land grid array", o "planar grid array package", cioè un pacchetto con contatti elettrodi a stato array realizzati sulla superficie inferiore. La sua forma è molto simile a quella dei componenti BGA, perché la sua dimensione del terreno è più grande di quella delle palline BGA. Il diametro è di circa 2 a 3 volte più grande ed è anche difficile controllare i vuoti. Ed è lo stesso dei componenti QFN, l'industria non ha formulato standard di processo pertinenti, che hanno causato problemi all'industria di elaborazione elettronica in una certa misura. Il nome completo di BGA è chiamato "ball grid array", o "ball grid array package". Attualmente, la stragrande maggioranza delle CPU mobili Intel utilizza questo metodo di imballaggio, ad esempio, tutti i processori Intel che finiscono in H, HQ, U, Y, ecc. (incluso ma non limitato a bassa tensione). BGA può essere il prodotto estremo di LGA e PGA, che è diverso dalla caratteristica che possono essere sostituiti a piacimento. Una volta che il BGA è confezionato, è impossibile per i giocatori ordinari smontarlo e sostituirlo in modo normale, ma perché viene fatto in una volta., Quindi il BGA può essere reso sempre più breve. I principali difetti dei giunti di saldatura a chip BGA sono: vuoti, dissaldatura (circuito aperto), ponte (corto circuito), crepe interne nella sfera di saldatura, disturbo del giunto di saldatura, saldatura a freddo, fusione incompleta della sfera di saldatura e spostamento (la sfera di saldatura non è allineata con il pad PCB), perle di saldatura, ecc.