A, simulazione PCB e progettazione di memoria DDR3

La tecnologia di memoria DDR3 del sistema informatico di oggi è stata ampiamente utilizzata e la velocità di trasmissione dei dati è stata ripetutamente promossa e ora è alta fino a 1866 Mbps.

Nella condizione di questo tipo di bus ad alta velocità, al fine di garantire l'affidabilità della qualità della trasmissione dei dati e soddisfare i requisiti di temporizzazione del bus parallelo, pone una grande sfida per la progettazione e l'implementazione.

Questo articolo utilizza principalmente lo strumento di analisi del dominio temporale di Cadence per analizzare quantitativamente il design DDR3, introduce i principali fattori che influenzano l'integrità del segnale dell'analisi di temporizzazione DDR3 e migliora e ottimizza il design attraverso l'analisi dei risultati per migliorare la qualità del segnale. La sua affidabilità e sicurezza sono notevolmente migliorate.

2 Introduzione alla memoria DDR3 DDR3 è simile alla memoria DDR2, inclusi 2 controller e parti di memoria, che utilizzano tutti la sincronizzazione della sorgente, cioè, il segnale selezionato (orologio) non viene inviato da una sorgente di clock separata, ma dal chip driver.

Ha una velocità di trasferimento dati superiore a DR2, fino a 1866MBPS; DDR3 utilizza anche la tecnologia prefetch a 8 bit, che aumenta significativamente la larghezza di banda di archiviazione e la sua tensione operativa è di 1,5V, garantendo un consumo energetico ridotto alla stessa frequenza. La progettazione dell'interfaccia DDR3 è difficile da raggiungere. Utilizza una topologia Fly-by unica e utilizza la tecnologia "write equalization" per controllare il tempo di offset interno del dispositivo e altre misure efficaci.

Anche se svolge un ruolo nel garantire l'implementazione del progetto e l'integrità del segnale, il sistema di archiviazione che raggiunge alta frequenza e larghezza di banda non è completo. Pertanto, l'analisi della simulazione è necessaria per garantire l'integrità dell'implementazione del progetto e la qualità del segnale.

Analisi di simulazione DDR3 combinata con il progetto per spiegare: scegli il modulo CPU dual-core PowerPC 64 bit, questo modulo utilizza MT41J256M16HA-125IT di Micron per la memoria.

Analizzando il processore del P5020, il modulo è configurato con una velocità di trasmissione dati del bus di memoria di 1333MT/s e una frequenza analogica di 666MHz.

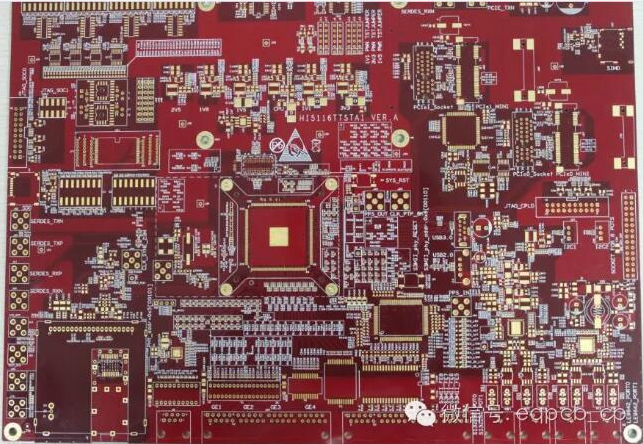

Prima dell'analisi, è necessario comunicare con il produttore di PCB in base all'impedenza di DDR3 per confermare la sua struttura laminata. La chiave per garantire le prestazioni della linea di trasmissione nella trasmissione ad alta velocità è l'impedenza caratteristica continua. Determinare il controllo dell'impedenza della linea di segnale PCB ad alta velocità entro un certo intervallo, in modo che il circuito stampato diventi una "scheda di impedenza controllabile", che è la base dell'analisi analogica.

L'impedenza singola del bus DDR3 è 50Ω, e l'impedenza lineare differenziale è 100Ω. Impostare il valore di tensione del terminale di rete di analisi, compreso il modello di allocazione passiva del dispositivo analizzato, determinare gli attributi del tipo di dispositivo e garantire gli attributi del pin del dispositivo (ingresso e uscita, messa a terra di potenza, ecc.)......

In secondo luogo, risolvere rapidamente l'integrità del segnale nel sistema ad alta velocità PCB

Risolvi rapidamente i problemi di integrità del segnale nei sistemi ad alta velocità PCB. Con l'aumento della velocità dei dati, i problemi di integrità del segnale sono diventati il fattore più critico considerato dai progettisti. Questo aumento esponenziale della velocità dei dati può essere osservato in applicazioni come router/switch ad alta larghezza di banda come dispositivi mobili portatili e prodotti display di consumo. Jitter (rumore) è il motivo principale per ridurre il livello di integrità del segnale nella progettazione. Oltre a utilizzare layout, corrispondenza dell'impedenza e materiali più costosi per ottenere la tecnologia di miglioramento dell'integrità del segnale, i progettisti possono anche semplicemente aggiungere ricevitori jitter come equalizzatori al design per risolvere il problema del jitter.

In questo modo, i progettisti non devono concentrarsi sui problemi di integrità del segnale, ma sul design centrale del sistema. Il cablaggio del segnale era spesso considerato un concetto semplice in passato, e non vi è distinzione tra segnali video, segnali vocali o segnali dati dal punto di vista del cablaggio. Pertanto, poche persone si preoccupavano del cablaggio del segnale in passato. Tuttavia, ora la situazione è completamente cambiata. La velocità di trasmissione del segnale video ha ora raggiunto i 3,3 Gbps per canale e il segnale dati supera di gran lunga i 5 Gbps per canale.

Gli standard seriali ad alta velocità come PCI Express, XAUI, SATA, TMDS e porta display richiedono ai team di progettazione e agli ingegneri non solo di considerare i problemi di integrità del segnale, ma anche di avere una comprensione approfondita di come influenzerà le prestazioni e l'affidabilità del sistema. Per padroneggiare questa conoscenza, gli ingegneri devono prima comprendere i fattori che influenzano l'integrità del segnale nel sistema. La perdita di integrità del segnale nel sistema può essere osservata aumentando il jitter del segnale. Il jitter totale del sistema è composto principalmente da due tipi di jitter, vale a dire jitter casuale e jitter deterministico. Il jitter casuale è infinito e fondamentalmente obbedisce alla distribuzione gaussiana, mentre il jitter deterministico è finito e prevedibile.

Nel 90% dei sistemi, il jitter deterministico è il principale problema di integrità del segnale che i progettisti devono risolvere. Il jitter deterministico include interferenza del codice (ISI), distorsione del ciclo di lavoro e jitter periodico, causati rispettivamente da problemi di limitazione della larghezza di banda, asimmetria del ciclo di clock e problemi di accoppiamento incrociato o EMI.

Componenti passivi come connettori, cablaggio PCB, cavi lunghi e altri componenti passivi posizionati lungo il cablaggio sono le fonti più importanti di jitter deterministico. Maggiore è la frequenza del segnale, maggiore è l'attenuazione, quindi il livello di potenza nel flusso di dati specificato non corrisponde e questo disallineamento del livello di potenza si tradurrà in ISI nel segnale.

ISI ridurrà l'integrità del segnale, il che è sufficiente per impedire al ricevitore di estrarre correttamente qualsiasi dato effettivo dal segnale all'estremità ricevente. La ragione della disallineazione del livello di potenza è che nessun ingegnere di progettazione può garantire la trasmissione dei dati nella progettazione. I dati possono essere in continuo cambiamento (0-1-0-1-0-1, ecc.) o costanti (1-1-1-1-1-1, ecc.). Ovviamente, il rapporto duty-free dei 6 bit di cui sopra è 6 volte il rapporto duty del flusso di dati costante 6"1". Poiché il rapporto duty-free è 6 volte più piccolo, la frequenza del segnale sarà 6 volte superiore.

Se il flusso di dati contiene questi due tipi, il segnale ricevitore avrà livelli di potenza molto diversi, perché maggiore è la frequenza, maggiore è l'attenuazione.

La maggior parte degli standard di segnale ad alta velocità stipulano che il numero di bit continui senza modifiche dovrebbe essere minimizzato, come la codifica 8B / 10B. Questo schema di codifica assicura che il flusso di dati non superi 4 bit consecutivi.

Tuttavia, è ancora possibile quadruplicare la porzione ad alta potenza del segnale ricevitore. Per compensare la disallineazione del livello di potenza per ridurre ISI, i progettisti di PCB possono utilizzare tecniche di equalizzazione o de-enfasi.

La tecnologia di equalizzazione PCB aumenterà la potenza di tutti i bit ad alta velocità, in modo che i segnali ricevuti nei bit ad alta velocità e bassa velocità abbiano lo stesso livello di potenza, riducendo così la disallineazione del livello di potenza. L'opposto di esacerbare l'equilibrio, ma l'obiettivo è lo stesso: ridurre al minimo il disallineamento del livello di potenza. Viene fatto riducendo la potenza del bit a bassa velocità, che aumenterà la potenza del bit ad alta velocità.