IPCBは PCB設計 電子商取引会社 製品設計 ((レイアウト配線設計)). 主に多層化する, 高密度 PCB設計 ドローイングボード 回路基板 設計証明事業. 次, でのスルーホールデザインの仕方を紹介します 高速PCB設計.

みんな知ってる, イン 高速PCB設計, 一見単純なビアはしばしば回路設計に大きな負の影響を及ぼす. したがって, イン 高速PCB design, we should try our best to do the following:

コストと信号品質の両方を考慮すると、合理的なスルーホールサイズを選択します。例えば、6〜10層のメモリモジュールの高速PCB設計のためには、スルーホールPCBを10 / 20 mil(ドリル/はんだ付けパッド)選択することが最適である。小型の高密度基板については、現在の技術条件で8 / 18 milスルーホールPCBsを使用しようとすることができ、より小さなスルーホールを使用することは困難である。電源または接地線用のスルーホールPCBsについては、より大きなサイズがインピーダンスを減少させると考えられる。

2. シンナーを使う PCBボード, これは、穴を通して2つの寄生パラメータを減らすのを助けます.

3 . PCBボード上の信号配線層を変更しないようにしてください。

(4)パワーピン及びグラウンドピンはホールに最も近いものであり、インダクタンスを大きくするので、ホール及びピンが短くなる。同時に、電源および接地リード線は、インピーダンスを減らすためにできるだけ厚くなければならない。

信号層のホールの近傍にグランドホールを設けて信号を最寄のループとする。さらに、プロセスが柔軟である必要があることを覚えておいてください。スルーホールPCBモデルは、各層上にパッドを有する。もちろん、いくつかの層パッドを減らすか、あるいは取り除くことさえできます。特に、スルーホールの密度が非常に高い場合には、銅層に溝分離回路が現れることがある。このとき、ビアの位置を移動させることに加えて、銅層のビアパッドを小さくすることも考えられる。

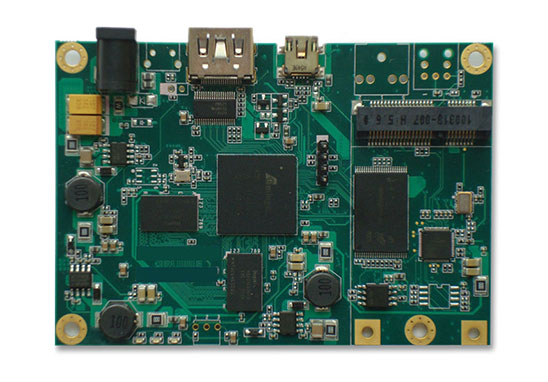

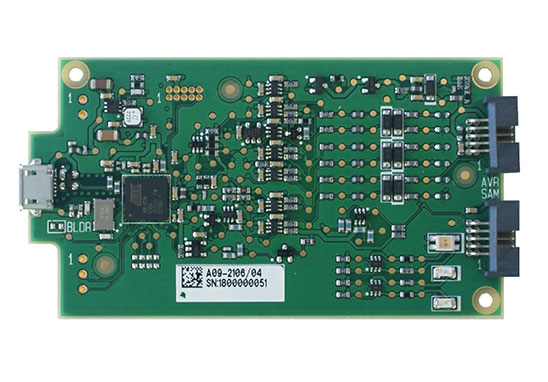

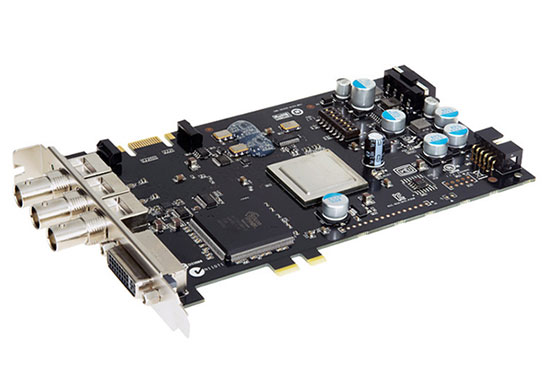

IPCB 回路基板 設計能力

最高信号設計率:10 GbpsのCML差動信号;

PCBデザイン層の最高数:40層;

最小線幅:2.4 mil;

最小線間隔

最小のBGAピン間隔:0.4 mm;

最小の機械的穴直径:6ミル;

最小レーザ穴あけ直径:4ミル;

最大ピン数:63000 +;

コンポーネントの最大数:3600 ;

BGAの最大数:48 +。

IPCB PCB設計サービスプロセス

顧客はPCB設計について概略図を提供する

(2)概略図と顧客の設計要件に従って引用を評価する

(三)顧客は、その申告を確認し、契約書に署名し、当該事業準備金を補充すること

4 .事前の支払いを受け、設計者の設計を行う

デザインが完了したら、確認のためにファイルのスクリーンショットを顧客に提供します

6. 顧客はOKを確認, バランスを決める, 提供 PCB設計 インフォメーション.