統合の機能の1つ 回路実装 チップの環境を保護し、チップと外気との接触を避けることである. したがって, 実装構造の気密性が特定の要件を満たすように、異なる種類の集積回路の特定の要件および使用場所に応じて異なる処理方法を採用し、異なる包装材料を選択する必要がある. 集積回路のための初期の包装材料は、有機樹脂およびワックスの混合物でできている, 包装は充填または注入により実現される. 明らかに, 信頼性は非常に貧しい. シールにはゴムを使用した, しかし、それはその不十分な熱のために除去されました, 油及び電気特性. 現在, 最も広く使用され、最も信頼性の高い密閉性材料は、ガラス金属封止である, セラミック金属封止と低融点ガラスセラミック封止. 大量生産とコスト削減の必要性, 多数のプラスチックモデルパッケージが出現した. 金型を通して熱硬化性樹脂を加熱・加圧して完成する. その信頼性は、有機樹脂及び添加剤の特性及び成形条件に依存する, しかし、その抵抗のために、それは熱特性と吸湿性が悪い, 他のシーリング材と比較できない. それはまだ半気密または非気密なシール材料です. チップ技術の成熟とチップ歩留まりの急速な改善, リアシーリングのコストは、集積回路全体のコストの増加する割合を占める. パッケージング技術の変化と発展は、それぞれの通過日で変化していて、それはめまいます.

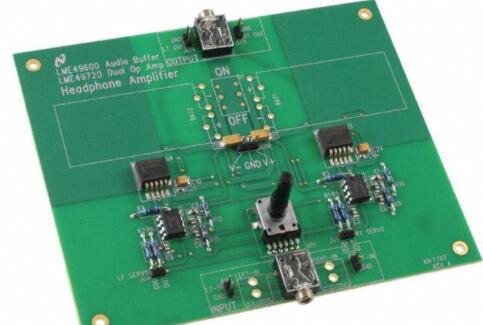

各チップにはデータシートがある, そして、アプリケーションの説明があります, 構造パッケージング, DataSheツールの材料番号およびその他の説明. デカールを力で作るとき PCB, データシートの構造パッケージ記述を参照する必要があります, には, 形状, 順序, etc. 各パッドの.

List of chip packaging methods:

1. BGA (ball grid array)

A display of spherical contacts, 表面実装パッケージの一つ. の後ろに printed circuit 板, ピンを交換するために、球状のバンプが表示モードで生成される, そして、LSIチップは、図1の前面に組み立てられる プリント回路基板, そして、成形樹脂またはポッティングで密封される. Also known as bump display carrier (PAC). ピンは200を超える, マルチピンLSI用パッケージ. The package body can also be made smaller than QFP (Quad Flat Package). 例えば, ピン中心距離1の360ピンBGA.5 mmは、わずか31 mmの正方形です;ピン中心距離0の304ピンQFP.5 mmは、40 mmの正方形です. そして、BGAはQFPのようなピン変形について心配する必要はありません. このパッケージは、米国モトローラ社によって開発されました. 最初に携帯電話や他の装置で採用された, そして、将来アメリカでパーソナルコンピュータで普及されるかもしれません. 当初, the BGA pin (bump) center distance was 1.5 mm, ピン数は225でした. 500ピンのBGAを開発しているいくつかのLSIメーカーもあります. BGAの問題はリフローはんだ付け後の目視検査である. 効果的な目視検査方法が利用可能かどうかはまだ明らかでない. いくつかは、溶接の大きな中心距離のため, 接続は安定していて、機能検査によってのみ処理できる. アメリカのモトローラ社は、成形された樹脂, and the package sealed by the pot錫g method is called GPAC (see OMPAC and GPAC).

2. BQFP (quad flat package with bumper)

Four-side pin flat package with cushion. QFPパッケージの一つ, the four corners of the package body are provided with protrusions (buffer pads) to prevent bending and deformation of the pins during transportation. アメリカン 半導体 メーカーは主にマイクロプロセッサやASIC. ピン中心距離は0です.635 mm, and the pin number is about 84 to 196 (see QFP).

3. Butt welding PGA (butt joint pin grid array)

Another name for surface mount PGA (see surface mount PGA).

4. C-(ceramic)

Indicates the mark of the ceramic package. 例えば, セラミックディップスタンド. それは実際にしばしば使用されるマークです.

5. Cerdip

Ceramic dual in-line package sealed with glass, ECL RAM用, DSP (digital signal processor) and other circuits. ガラス窓付きセルディップは、EPROM内部の紫外線消去可能EPROMとマイクロコンピュータ回路に使用される. ピン中心距離は2です.54 mm, そして、ピンの数は、8から42まであります. 日本にて, this package is expressed as DIP-G (G means glass seal).

6. Cerquad

One of the surface mount packages, ハーメチックシール下のセラミックQFP, は、DSPなどの論理LSI回路をパッケージ化するために使用される. WindowsとのCerquadはEPROM回路をカプセル化するのに用いられます. プラスチックQFPよりも放熱性が良い, そして、それは1を許容することができます.自然の空気冷却条件の下の5 ~ 2 Wの力. しかし、パッケージングコストはプラスチックQFP. ピンの中心距離は1のような種々の仕様を有する.27 mm, 0.8 mm, 0.65 mm, 0.5 mm, 0.4 mmなど. ピンの数は32から368の範囲です.

7. CLCC (ceramic leaded chip carrier)

A ceramic chip carrier with pins, 表面実装パッケージの一つ. ピンは、パッケージの4つの側面から引き出され、T字型である.

これは、紫外線消去可能なEPROMとEPROM. このパッケージはqfjとも呼ばれます, QFJ-G (see QFJ).

8. COB (chip on board)

Chip-on-board packaging is one of the bare chip mounting technologies. The 半導体 チップは手に取り付けられ、マウントされます プリント回路基板. チップと基板との間の電気的接続は、ワイヤステッチによって実現される, そして、チップと基板との間の電気的接続は、ワイヤステッチによって実現される. 樹脂の信頼性確保. COBは最も簡単なベアチップ実装技術であるが, 実装密度はTABとフリップチップボンディング技術にはるかに劣る.

9. DFP (dual flat package)

Double-sided lead flat package. それはsです... the rest of the full text>>

The package using vinyl refers to the COB (Chip On Board) package.

The COB packaging process is as follows:

The first step: crystal expansion. 膨張機は、製造者が提供するLEDチップフィルム全体を均一に拡大するために使用される, フィルムの表面に取り付けられた堅く配列されたLEDダイが引き裂かれて、とげの結晶を容易にするために.

ステップ2:接着剤. 銀ペースト層が削られたバッキングマシン面に広げられた結晶リングを置いてください, そして、銀のペーストを背中に置いてください. いくつかの銀ペースト. バルクLEDチップに適した. 適切な量の銀ペーストをスポットに置くために、調剤機を使ってください PCB プリント回路基板.

第三段階:銀ペーストで準備した結晶膨張リングをピアスクリスタルホルダーに入れる, そして、オペレータはLEDチップを PCB プリント回路基板 顕微鏡下でピアスペンで.

ステップ4:ピアスをかける プリント基板 熱サイクルオーブンで一定の温度で一定時間, and take it out after the silver paste has solidified (do not leave it for a long time, さもなければ、LEDチップコーティングは黄色を焼きます, それで, 酸化する, give the 接着 Cause difficulties). LEDチップボンディングがあれば, 上記のステップが必要ですICチップボンディングがあれば, 上記のステップはキャンセルされる.

番目のステップ:チップをスティック. Use a dispenser to put an appropriate amount of red glue (or black glue) on the IC position of the PCB プリント回路基板, and then use an anti-static device (vacuum suction pen or sub) to correctly place the IC die on the red glue or black glue.

第六段階乾燥. 接着されたダイを大きな平らな加熱プレートで熱サイクルオーブンに入れて、それを一定の温度でしばらく耐えるようにしてください, or it can be cured naturally (for a longer time).

The seventh step: Bonding (playing the line). The aluminum wire bonding machine is used to bridge the chip (LED die or IC chip) with the corresponding pad aluminum wire on the PCB board, それで, コブのインナーリードは溶接されている.

第8ステップ:プリテスト. Use special testing tools (different equipment for COB for different purposes, simply high-precision stabilized power supply) to test COB boards, と無修正のボードを再修復.

ステップ9:調剤. 接着剤ダイスペンサーは、接着されたLEDダイの上に準備されたAB接着剤の適量を置くために用いる, そして、ICは黒い接着剤で包まれます, そして、顧客の要件に応じて外観でパッケージ化.

第一歩:硬化. 密封する プリント基板 熱サイクルオーブンに、それを一定の温度に立つ. 異なる乾燥時間を要件に応じて設定することができます.

第11ステップ:ポストテスト. 包装された PCB プリント回路基板次に、Sは、良いものと悪いものを区別するために特別なテストツールで電気性能のためにテストされます.

第12ステップ:研磨. Grind according to the customer's requirements for product thickness (generally soft PCB).

第13ステップ洗浄. 製品をきれいにする.

第14ステップ:エアドライ. クリーニング製品を二度乾燥させる.

ステップ15:テスト. The success or failure is determined at this step (there is no better way to remedy the bad film).

第16ステップ:切断. カットする PCB into the size required by the customer

The seventeenth step: packaging and leaving the factory. 製品を梱包する.

ビニルの融点は比較的低い. 装着時, まずビニールでワイヤーをカプセル化する, そして、チップと他の簡単に損害を受けたオリジナルをインストールしてください. ビニール一度加える, 次の充填は少ないビニルですので, パッケージがオリジナルにダメージを与えないことが保証されます.

半導体集積回路チップを実装するために使用されるシェルは、配置、固定、封止、チップの保護、および電気熱性能の向上の役割を果たし、チップの内部世界と外部回路との間のブリッジであり、チップ上のコンタクトはピン上のワイヤでパッケージシェルに接続されている。これらのピンは、プリント基板上のワイヤを介して他のデバイスとの接続を確立する。このため,cpuや他のlsi集積回路において実装が重要な役割を果たしている。

最も重要なものはエポキシ樹脂とセラミックスである。

前者はデュアルインラインパッケージであり,後者はsmdパッケージの最も一般的なタイプである。下の図に示されているように、(nはディップで、Dで示されるのはSOPです)。

Introduction to Semiconductor Packaging:

The 半導体 ウエハ製造からの生産プロセス, ウエハ試験, チップ実装とポストパッケージ試験. 半導体パッケージは、独立したチップを得るために製品モデルおよび機能要件に従って試験されたウェーハを処理するプロセスを指す. The packaging process is: the wafer from the previous wafer process is cut into small chips (Die) after the dicing process, and then the cut chips are attached to the corresponding substrate (lead frame) frame with glue. 島で, use ultra-fine metal (gold, tin, 銅, aluminum) wire or conductive resin to connect the bond pad of the chip to the corresponding lead of the substrate to form the required circuit ; Then the independent chip is encapsulated and protected with a plastic shell. プラスチックカプセル化後, 一連の操作が必要です, such as post-curing (Post Mold Cure), trimming and forming (Trim&Form), plating (Plating), と印刷. 包装完了後, 完成品検査, 通常は、着信の手順を通過する, テスト, 梱包, そして最後に倉庫と出荷. 典型的なパッケージプロセスは, 読み込み, bonding, プラスチック包装, フラッシュ除去, 電気めっき, トリミング成形, 外観検査, 製品テスト終了, 包装及び出荷.

1概要 半導体 device packaging

Electronic products are composed of 半導体 devices (integrated circuits and discrete devices), プリント回路基板, ワイヤ, コンプリートマシン, ケーシング, とディスプレイ. 集積回路は、信号処理および制御に使用される. ディスクリートデバイスは、通常、信号増幅と印刷です. 回路基板 ワイヤは信号を接続するために使われる, マシン全体のフレームシェルはサポートと保護に使用されます, そして、表示部分は、人々とのコミュニケーションのためのインターフェースとして使われます. したがって, 半導体 デバイスは電子製品の主要かつ重要な部分である, エレクトロニクス産業における「稲作米」の評判.

私の国は1960年代に最初のコンピュータを開発し生産した. 約100 m 2以上の面積を占める. 今日の携帯用コンピュータは小袋の大きさにすぎない, 将来のコンピュータがペンのサイズであるかもしれないか、より小さいかもしれませんが. コンピュータの大きさの急速な縮小とそれらのますます強力な機能は 半導体 テクノロジー. The credit is mainly due to: (1) The substantial increase in 半導体 chip 積分 and wafer fabrication (Wafer fabrication) 改良 the lithography precision has made the function of the chip increasingly powerful and the size smaller; (2) The improvement of the 半導体 実装技術は、集積回路の集積度を大きく向上させた プリント回路基板, そして、電子製品のボリュームが大幅に増加している. 減らす.

The improvement of 半導体 assembly technology (Assembly technology) is mainly reflected in the continuous development of its package type (Package). Usually referred to as assembly (Assembly) can be defined as: the use of film technology and micro-connection technology to connect the 半導体 chip (Chip) and the frame (Leadframe) or substrate (Sulbstrate) or plastic sheet (Film) or the conductor part of the プリント回路基板 配線ピンを引き出すために, そして、プラスチック絶縁媒体でpottingして、封をすることによって、彼らを固定してください, 全体三次元構造のプロセス技術の形成. 回路接続機能, 身体の支えと保護, 外部磁界遮蔽, 応力緩衝, 放熱, 大型化と標準化. 三極時代のプラグインパッケージと1980年代の表面実装パッケージから現在のモジュールパッケージまで, システムパッケージ, etc., 前任者は多くのパッケージ形態を開発した, 新しいパッケージの形は新しい材料を必要とするかもしれません, 新しいプロセスや新しい装置が使用されます.

連続開発を推進する駆動力 半導体 包装はその価格と性能である. 電子市場の最終顧客は3つのカテゴリーに分けられる, 産業ユーザーとナショナルユーザー. ホームユーザーの最大の特徴は、価格が安いとパフォーマンス要件が高くないことですナショナルユーザーは高いパフォーマンスを必要とします、そして、価格は通常普通のユーザー, 主に軍事と航空宇宙で使用される, etc.; 産業ユーザーは、通常、上記の2つの間ですべての下落価格とパフォーマンスです. 低価格は原価でコスト削減を要する, 使用する材料が少なくなるように, より良い, そして、ワンタイム出力が大きいほど, より良い. 高性能は長い製品寿命を必要とします、そして、過酷な環境に耐えることができます. 半導体メーカは常にコスト削減と性能向上を求めている. もちろん, 環境保護要件や特許問題などの他の要因は、パッケージの種類を変更する.

2 The role of encapsulation

Package (Package) is necessary for the chip, でもとても重要. また、パッケージングは 半導体 integration...The rest of the full text>>

バウンドパッケージは、一般的に牛の糞として知られている、それは水分が原因で失敗する傾向があります。