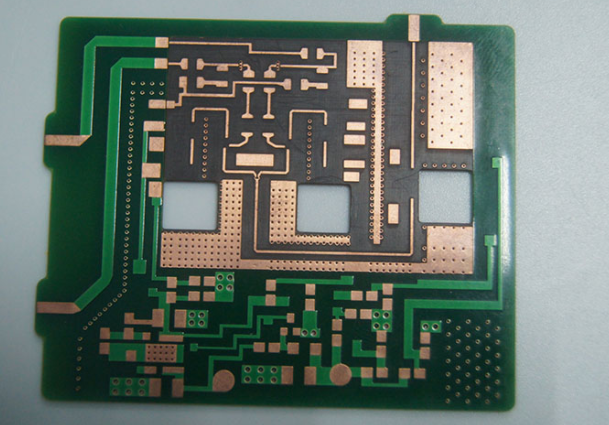

回路基板RF回路設計規則

Although there are still many uncertainties in the design of radio frequency (RF) 回路基板理論上, デザインにはまだ多くの規則があります RF回路基板.

しかし, 実際には PCB設計, 本当に実用的なスキルは、様々な制限のために実装することができないときにこれらの規則をトレードオフする方法です. 本稿は、RFの設計に関連する様々な問題に焦点を当てます 回路基板 パーティション.

1. 異なる特性をもつマイクロビア回路のタイプ 回路基板 分離しなければなりません, しかし、彼らは電磁妨害なしで最高の条件の下で接続されなければなりません. これはmicroviasの使用を必要とする.

通常、マイクロビアの直径は0.05 mm〜0.20 mmである。これらのビアは、一般的に3つのカテゴリー、すなわち盲目のビア、埋められたビアとビアを通して分けられる。

ブラインドビアは、プリント回路基板の上面および底面に位置し、ある深さを有する。これらは、表面線と下の内側の線を接続するために使用されます。穴の深さは、ある比率(開口)を超えない。

埋込みビアは、回路基板の表面に延在しないプリント回路基板の内側層に位置する接続孔を指す。

上記2種類のホールは、回路基板の内層に位置し、積層前のスルーホール形成工程によって完成し、ビア形成時にいくつかの内層を重ね合わせてもよい。

第3のタイプはスルーホールと呼ばれ、回路基板全体を貫通し、内部配線用または接着用の位置決め用孔として使用することができる。

(2)パーティション技術を用いてRF回路基板を設計する場合、高出力RFアンプ(HPA)と低雑音増幅器(LNA)をできるだけ離すべきである。簡単に言えば、高電力RF送信回路を低雑音受信回路から遠ざけることである。

PCB上に多くのスペースがあれば、これは簡単に行うことができます。

通常、多くのコンポーネントがあるとき, the PCB製造 空間はとても小さくなる, それで、これは達成するのが難しいです.

あなたはそれらをPCBの両側に置くことができます、あるいは、同時に働く代わりにそれらを交互に働かせてください。

高電力回路は、時々、RFバッファおよび電圧制御発振器(VCO)を含む。

設計分割は物理的分割と電気的分割に分けることができる。

物理的な分割は主にコンポーネントのレイアウト、向き、および遮蔽の問題を含んでいます電気的分配は、電力分配、RF配線、高感度回路及び信号、及び接地に分けられる。

物理的な分割。コンポーネントのレイアウトは、優れたRF設計を達成するための鍵です。最も効果的な方法は、RFパス上の構成部品を固定し、RFパスの長さを最小にする位置を調整することである。

そして、RF入力からRF入力を遠ざける、そして、高出力回路および低雑音回路からできるだけ遠く離れている。

最も効果的な回路基板スタッキング法は、表面下の第2層上に主グランドを配置し、RFラインをできるだけ表面に配線する方法である。

RF経路上のビアのサイズを最小化することは、経路インダクタンスを減少させるだけでなく、主グラウンド上の仮想はんだ接合を低減し、また、ラミネートの他の領域に漏洩するRFエネルギーの機会を低減する。

物理空間において、多段増幅器のような線形回路は、通常、複数のRFゾーンを互いに分離するのに十分であるが、デュプレクサ、ミキサ、および中間周波増幅器は、互いに干渉する複数のRF/IF信号を常に有している。したがって、この効果を最小限にするために注意を払わなければなりません。

RFとTRANは、可能な限り交差しなければならない。そして、接地面積はできるだけそれらの間に置かれるべきである。

正しいRFパスは、PCB基板全体の性能にとって非常に重要である。これは、通常、コンポーネントのレイアウトが、通常、携帯電話PCBボード設計においてほとんど取り上げられる理由である。

携帯電話で PCBボード, 通常、低雑音増幅回路は、PCB校正ボードの片側に配置することができる, そして、高出力増幅器は反対側に置かれる, そして、最後に、それらはデュプレクサによって、同じ側のRFアンテナに接続している. ベースバンドプロセッサの一端と他端.

これは、RFエネルギーがボードの一方から他方へのビアを通過しないことを確実にするための何らかの技術を必要とする。一般的なテクニックは両側にブラインドバイアを使用することです。PCBの両側にRF干渉を受けない領域にブラインドバイアを配置することによって、ビアの悪影響を最小化することが可能である。

金属シールドカバーは、時々、複数の回路ブロック間の十分な分離を保つことができない。この場合、RFエリア内の無線周波数エネルギーをシールドするために、金属シールドカバーを使用することを考慮する必要があるが、金属シールドカバーも副作用がある。

不規則な形状の金属シールドカバーを製造する場合には,高い精度を確保することは困難である。長方形または正方形の金属シールドカバーもコンポーネントのレイアウトを制限します

金属遮蔽カバーは、コンポーネント置換および故障変位に助力されない金属遮蔽カバーは接地面に溶接されなければならず、部品から適切な距離に保たれなければならないので、貴重なPCBボードスペースを取る。

金属シールドの完全性をできるだけ確保することは非常に重要である。したがって、金属シールドに入るデジタル信号線は、なるべく内側の層に行くべきであり、信号層の次の層を接地層として設定するのがベストである。

RF信号線は、金属シールドの底部とグランドギャップの配線層の小さなギャップから外部に取り出すことができるが、ギャップはできるだけ大きな接地面積で囲まれるべきである。異なる信号層上のグラウンドは、複数のビアを使用することができる。リンクアップ。

上記の欠点にもかかわらず、金属シールドは依然として非常に有効であり、しばしば臨界回路を分離する唯一の解決策である。

5 .電力デカップリング回路の適切かつ効果的なチップパワー分離回路もまた非常に重要である。

線形回路を集積する多くのRFチップは、パワーノイズに非常に敏感である。通常、各チップは、すべての電力ノイズをフィルタリングするために最大4個のコンデンサおよび絶縁インダクタを使用する必要がある。

最小のキャパシタンス値は、通常、コンデンサ自体の共振周波数およびピンインダクタンスに依存し、それに応じてC 4の値が選択される。

C 3及びC 2の値は、それら自身のpinインダクタンスにより比較的大きいので、RFデカップリング効果はより悪いが、より低い周波数ノイズ信号をフィルタリングするのにより適している。

RFデカップリングは、インダクタL 1によって行われ、RF信号が電力線からチップに結合するのを防止する。

すべてのトレースはRF信号を受信して送信することができる可能性のあるアンテナであるので、RF回路をキー回路およびコンポーネントから分離する必要がある。

これらのデカップリング構成要素の物理的位置は、通常も重要である。

これらの重要なコンポーネントのレイアウト原理は以下の通りです。

C 4はICピンに可能な限り近くなければならなくて、接地されなければなりません, C 3はC 4に最も近いに違いない, C 2はC 3に最も近いに違いない, そして、ICピンとC 4の間の配線は、できるだけ短くなければなりません, the grounding terminals of these components (especially C4) Usually should be connected to the ground pin of the chip through the first ground layer under the PCBボード.

コンポーネントをグランドプレーンに接続するビアは、PCB上の構成パッドに可能な限り近くなければならない。接続ワイヤのインダクタンスを最小にするために、パッドの上に打ち抜かれる盲目の穴を使うことは、最高です。インダクタンスL 1はC 1に近い。

集積回路または増幅器は、オープンコレクタ出力を有することが多いので、高インピーダンスRF負荷および低インピーダンスDC電源を提供するために、プルアップインダクタが必要である。このインダクタについても同様である。電源側のデカップリング。

いくつかのチップは、複数の電源を動作させる必要があるので、2つまたは3組のコンデンサおよびインダクタを別々に分離する必要がある。チップの周囲に十分なスペースがない場合、デカップリング効果は良好ではない。

特に、これは特別な注意を払う必要があります:これは、空気コア変圧器を形成し、干渉信号を相互に誘導するので、平行に一緒に近接していないので、それらの間の距離は少なくともそれらの1つの高さに等しくなければならないか、直角インダクタンスを最小にするように配置されなければならない。