最近に基づきます PCB設計 トレンド, 効率を改善することが重要な目標になった, そして、より良いEMIのために遅いスイッチング装置を使用するトレードオフは価値がありません. スーパー接合は、プレーナMOSFETが取り扱うのが困難な用途での効率を向上させることができる. 従来のプレーナMOSFET技術と比較して, スーパージャンクションMOSFETは、オン抵抗と寄生容量を著しく低減することができる. オン抵抗の減少と寄生容量の減少は効率を改善するのに役立つ, it also produces rapid switching of voltage (dv/dt) and current (di/dt), 高周波ノイズと放射EMI.

高速スイッチングスーパージャンクションMOSFETを駆動するためには,スーパージャンクションを使用するために作られたPCB設計レイアウト調整と同様に,スイッチング性能に対するパッケージとPCB設計レイアウト寄生の影響を理解する必要がある。耐圧500〜600 vのスーパージャンクションmosfetが主に用いられている。これらの電圧定格のうち、220〜247、to - 3 p、および263までの業界標準は、最も広く使用されているパッケージである。内部のゲートおよびソースボンディングワイヤ長が固定されるので、パフォーマンスにパッケージの影響は制限される。パッケージのソースインダクタンスを小さくするために、リード線の長さだけを変更することができる。

10 nhの典型的なリードインダクタンスは大きく見えないが、これらのMOSFETのdi/dtは容易に500 A/5/1/4 Sに達することができる。di/dtが500 a/5/1/sであると仮定すると、10 nhのリードインダクタンスの電圧はVIND=5 Vであるまた、10 nHのリードインダクタンスのdi/dtのターンオフは1000 A/15.1/Sであり、VIND=10 Vの電圧を発生する。ほとんどのアプリケーションおよび設計は、この追加インダクタンスも電圧を発生させるとは考えていないが、これは無視することはできない。上記の簡単な計算は、パッケージの合計ソースインダクタンス、すなわちボンドワイヤとピンインダクタンスを許容値にする必要があることを示している。ノイズの別のソースは、レイアウト寄生です。寄生インダクタンスと寄生容量という2つの目に見えるレイアウト寄生がある。1 cmのインダクタンスは6〜10 nHである。このインダクタンスは、PCBの上部に層を加え、PCBの底部にGND層を追加することによって低減することができる。他のタイプは寄生容量である。

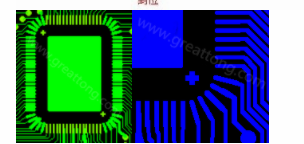

レイアウトにおける容量寄生の原理. 寄生キャパシタンスは、隣接する2つのトレースまたは他の側のトレースと接地平面との間に起因する. 別のタイプのキャパシタンスは、デバイスと接地面との間のキャパシタンスである. 両側に平行に走る2本の線 PCBボード キャパシタンスを増加し、ループインダクタンスを減少させることができる, これにより電磁ノイズ放射を低減する. あなたのデザインがスーパー接合MOSFETsを必要とする次のとき、これらのレイアウト・チップを考慮してください.

実装とレイアウトにおける寄生成分

MOSFETは単極性デバイスであるので、寄生容量はスイッチング過渡現象の唯一の制限要因である。電荷平衡の原理は、特定の領域のオン抵抗を減少させ、標準的なMOSFET技術と比較して、同じRDS(on)の下のチップサイズがより小さい。スーパージャンクションMOSFETと標準的な平面MOSFETのキャパシタンスを示す図である。標準MOSFETのcossは適度に線形関係を持ち,スーパー接合mosfetのcoss曲線は高い非線形関係を示した。セル密度が高いため、スーパージャンクションMOSFETのコースの初期値は高くなるが、スーパージャンクションMOSFETでは約50 Vのドレイン・ソース電圧付近で急速に低下する。超接合MOSFETが、PFCまたはDC/DCコンバータで使用される場合、これらの非線形効果は、電圧および電流振動を引き起こす可能性がある。図3は、パワーMOSFETおよび外部発振器回路の内部寄生素子を含む、PFC回路の簡略化された概略図を示す。外部発振回路は、レイアウトによってもたらされる外部結合コンデンサ(CGdNext−ext .)を含む。

平面MOSFETとスーパー接合MOSFET間の出力容量の比較

一般的に言えば, MOSFETのスイッチング特性に影響する複数の発振回路が存在する, 内部および外部発振回路を含む. に PFC回路, エル, COとDboostはインダクタである, 出力コンデンサおよびブーストダイオード. CGS, CGdRage intおよびCdSは、パワーMOSFET 100の寄生容量である. LD 1, LS 1, とLG 1はドレイン, ソース, パワーMOSFETのゲートボンディングワイヤとピンインダクタンス. RGRANint及びRGNEXTは、パワーMOSFETの内部ゲート抵抗及び回路の外部ゲート駆動抵抗である. CGdHelextは、回路の寄生ゲートドレインキャパシタンスである. LD, LS, そして、LGはドレインの浮遊インダクタンスである, ソース, and gate traces of the printed circuit board (PCB). MOSFETがオンまたはオフになると, ゲート寄生発振は、ゲート-ドレイン容量CgdおよびゲートリードインダクタンスLg 1を介して共振回路に生じる.

共振条件(λ=1/1)では、ゲート電圧およびソース電圧に発生する発振電圧は駆動電圧よりもはるかに大きい。この共振変化に起因する電圧振動は、Q値(Q=L/R=1/1)で比例する。MOSFETがオフすると、ドレイン寄生インダクタンス(LD+LD 1)、ゲート・ドレイン容量Cgd、ゲート・リードインダクタンスLg 1がゲート発振電圧を発生する。ゲート抵抗(RG−EXT .+RGSEX int)が非常に小さい場合、Qは大きくなる。加えて、LS 1の電圧降下およびLS 1のソース浮遊インダクタンスは、ゲート-ソース電圧において発振を発生する。寄生発振は、ゲート・ソース破壊、不十分なEMI、大きなスイッチング損失、ゲート制御不良を引き起こし、MOSFET故障を引き起こす可能性がある。

負の効果のないスーパージャンクションmosfetの性能を最大にするために回路設計を最適化することは非常に重要である。