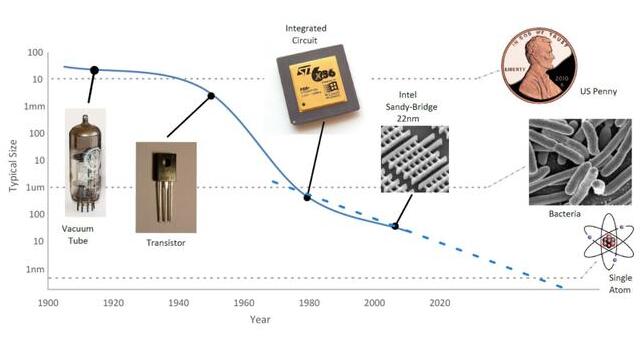

1950年代には、フェアチャイルド半導体とインテルの共同創設者であるゴードンムーアは、次の10年で、集積回路ごとの部品数が毎年2倍になると指摘した論文を発表した。1975年に、彼は彼の予想を概説して、構成要素の数が現在2年ごとに倍になると言いました。これは有名なムーアの法則です。

ムーアの法則は何十年も正しいことが証明されている。さらにムーアの法則はチップ製造とデザインを導いている。インテルとAMDの研究者は、ムーアの法則に従って常に目標と目標を設定しました。ムーアの法則がチップ設計の急速な発展を促して、コンピュータはより小さくてより小さくなります。ムーアの法則は単なる予測ではなく、メーカーが目指す目標と基準になっている。ムーアの法則の例を以下に示します。

1971年に、第1の半導体プロセスのうちの1つは、10ミクロン(メートルより10万倍小さい)であった。2001年までには,1971年に比べて130 nm,約80倍であった。

2017年現在, トランジスタプロセスは10 nm. 人間の髪に比べて, 直径は100ミクロンであった, 今日のトランジスタより10000倍大きい.

ムーアの法則

大規模回路の開発, トランジスタは小さくなっている, そして、集積回路の数は、幾何級数的に増加している, しかし、その製造工程はますます難しくなっている. これらの技術的、技術的障壁を克服するには多くの時間と研究が必要である, しかし、多くの資本と投資. したがって, ムーアの法則の時間も徐々に減速する, そして、それさえすぐに確立されないかもしれません, and the crisis of Moore's law breaks out (of course, it is inevitable if there is no great change).

インテルは2012年の22 nmプロセスから2014年の14 nmプロセスまで開発するには約2年半かかりました. その後, 10 nmの研究開発は、問題なく、何度も遅れました. 2019年まで利用できない場合があります. しかし, the good news is that AMD 7Nm graphics card and CPU will be available in 2019 (see the recent article "amd future product outlook...". ムーアの法則は本当の法ではないからです, しかし、予測または推測. チップメーカーは目標を達成し維持することを約束したが, ますます難しくなってきた.

ムーアは2015年に自分自身を引用している。

量子トンネリング

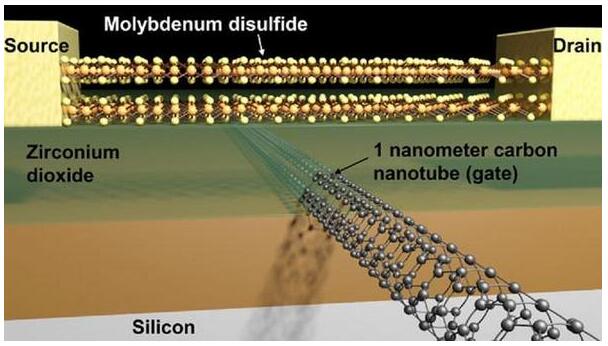

電子部品が小さくなり(ナノスケール)なると量子特性や効果が徐々に現れる。トランジスタのサイズを小さくし続けると、pn接合空乏層のサイズも減少する。空乏層は電子の流れを防ぐために非常に重要である。5 nm以下のトランジスタは,それらの空乏領域の電子のトンネリング効果による電子の流れを止めることができないと計算した。トンネリングのため、電子は空乏領域を知覚せず、直接「クロス」する。あなたが電子の流れを止めることができないならば、トランジスタは失敗します。

そのうえ、我々は現在原子自体のサイズにゆっくり近づいています。理論的には、原子より小さいトランジスタを作ることはできません。シリコン原子の直径は約1 nmであり、我々のトランジスタのゲートサイズはそのサイズの約10倍である。量子効果を考慮しなくても?また、トランジスタの物理的限界に到達し、より小さくすることはできない。

電流と加熱効果

量子トンネリング及び物理的限界に加えて、2つの非常に制限的なプロセス問題、すなわち、小型トランジスタの加熱効果がある。トランジスタが小さくなるにつれて、トランジスタはオフ状態においても、「リーク」する傾向がある。また、電流を通すことも避けられない。これをリーク電流と呼ぶ。100 nAにリーク電流を設定すると、CPUが100万個のトランジスタを有する場合、リーク電流は10 Aとなる。これは数分で携帯電話のバッテリーを消耗します。より高いゲート電圧は漏れ流れを減少させることができるが、これはより多くの加熱効果をもたらす。それを考慮せずに、各クロックの計算自体が多くの熱を消費します。メーカーはこれらの属性を使用し、これらの効果を防ぐためにそれらをちょうど右にする必要があります。プロセスが小さくなるほど小さくなり、プロセスがますます難しくなる。

また、高リーク電流は、暗シリコンおよび暗メモリの問題にもつながる。多くのトランジスタが我々のチップにあるかもしれないけれども、大部分のトランジスタはチップが過熱して、融解するのを防ぐために離れていなければなりません。すべてのこれらのオフ状態トランジスタは、他のコンポーネントを配置するために使用できる多くのスペースを取る。これは問題につながる:我々は本当に小さくする必要があるか、または既存のチップ設計を改善するか?

将来の展望

5 nmデザイン

これらのすべての要因を考慮して、インテルエグゼクティブと国際半導体技術ロードマップは、5 nmが到達できる限界サイズであることを示している。2021年には5 nmがデビューすると予想される。それでは、その後何を期待することができますか?

デナードのスケーリングデナードスケーリングはムーアの法則の姉妹法であると考えられる。それは1974年にロバート・デナードによって開発されて、トランジスタがより小さくなるので、彼らのパワー密度が減少すると指摘しました。これは、トランジスタが小さくなるにつれて、それらを動作させるのに必要な電圧および電流の量も減少することを意味する。この法則は、メーカーがトランジスタのサイズを減らして、反復につき大きなジャンプによって時計速度を上げるのを許します。しかし、2007年ごろ、デナードのスケーリングは崩壊しました。これは、より小さいサイズでは、リーク電流がトランジスタを加熱し、更なる損失を生じさせるからである。

私たちは、トランジスタがより小さくなったけれども、CPUコンピューティング・レートがDENNARSスケーリング・クラッシュのために過去10年で増加しなかったと気がつきました。高クロックレートでの高い損失はまた、スマートフォンチップが低いクロック速度(通常1.5 GHz)を使用する理由でもある。

久米の法則

現在のチップ実装とより良い命令パイプラインを改良することによって、我々はチップのパフォーマンスを改善することができます。スタンフォード大学教授ジョナサン・クメイはKoomeyの法則を提案しました。エネルギーのジュールごとの計算数は1.5年ごとに倍になります。この状況は2048年まで続き、Landauerの原理と熱力学の単純な法則がさらなる改善を妨げることになるだろう。現在,landauer限界の計算機効率は約0 . 00001 %である。

マルチコアアーキテクチャ

伝統的なプログラミング言語(Java、C ++とPythonなど)は、単一のデバイスでのみ実行できます。しかし、装置がより小さくてより安いように、我々はパフォーマンスをさらに向上させるために多くのチップの上で同時に、または、並行して同じプログラムを走らせることができます。この点で、golangとノードのような言語は、より重要な役割を演じます。

新素材研究

世界中の研究者は、より小さくてより速いトランジスタを作るより新しくてより革新的な方法を探しています。窒化ガリウムやグラフェンなどの材料はスイッチング周波数が速いほど損失が少ないことが証明されている。

量子コンピューティング

現在,可能な解決策は量子コンピュータを開発することである。d波とrigettiコンピューティングのような企業は、この分野で広範囲に働いています。さらに重要なことに、キュービットの法則の拡大はまだ始まっていない。DENNARDスケーリングを迂回する方法は、パフォーマンスを改善するために、より多くのコアを一つのチップに置くことです。現在,量子計算は大きな見通しを示した。その利点は複数の状態(他のコンピュータ0と1とは異なる)を持つことができることである。現在,量子計算による実乱数アルゴリズムの成功が期待されている。