PCBアナログ信号配線 要件

(1)干渉防止性能を向上させるためには、できるだけ短くする。

アナログ信号の一部はインピーダンス制御要求を放棄し、適切に配線を厚くすることができる。

3 .配線範囲を制限し、可能な限りアナログレンジ内の配線を完了し、デジタル信号から遠ざかる。

PCB高速信号配線要件

多層配線

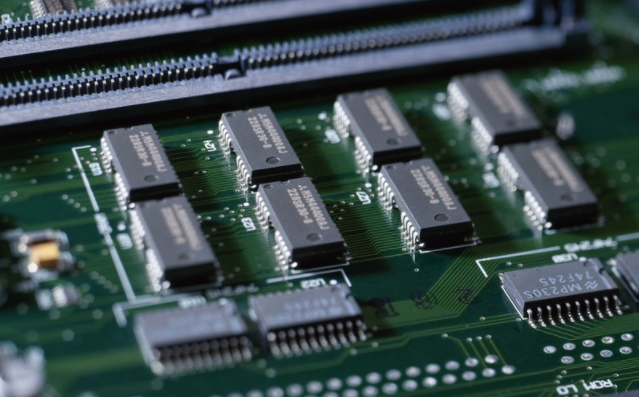

高速信号配線回路は、通常、高集積化と高い配線密度を有している。多層基板の選択は配線のためだけでなく,干渉を低減する合理的かつ効果的な方法である。重ね合わせ層の数を適切に選択することにより、プリント基板のサイズを大幅に小さくすることができ、中間層を完全に使用してシールドを設定することができ、最も近い接地を科学的かつ合理的に実現することができ、寄生インダクタンスを合理的かつ効果的に低減することができ、信号伝送長を合理的かつ効果的に短縮することができる。そして、信号間の交差干渉を減らすために大いに接地できる。

2 .鉛はできるだけ小さく曲げる

高速回路デバイスのピン間のリードのより少ない屈曲、より良い。高速信号配線回路配線のリード線は、できるだけ完全にまっすぐにして回す必要がある。45度程度の折線やアークターンを使用することができます。この要求は、低周波回路における鋼箔の固定強度の向上に使用され、高速回路ではこれが満たされる。しかし,高速信号の外部発光と相互結合を低減でき,信号の放射と反射を低減できる。

(3)鉛が短いほど、よりよい

高速信号配線回路のピン間のリード線は短くなる。リードが長いほど、分布インダクタンスおよび分布キャパシタンスが大きくなり、システムの高周波信号の通過に影響を与える。同時に、回路の特性インピーダンスも変化させ、システムを反射させて振動させる。

(4)鉛層間の交替

高速回路デバイスのピン間のリード層がより少なくなるほど、より良い。いわゆる「リード線の層間交替がより少なく、より良い」とは、部品接続プロセスで使用されるより少ないビアがよりよいことを意味する。一つのビアが約0.5 pFの分布キャパシタンスをもたらすことができ、回路の遅延が著しく増加し、ビアの数を減らすことによって、速度を著しく増加させることができる。

パラレルクロス干渉に注目

信号線の短距離並列配線で導入された「クロス干渉」には高速信号配線が注目される。並列分布を回避することができない場合は、並列信号線の反対側に「グランド」の大面積を配置して干渉を大幅に低減することができる。

枝や切り株を避ける

高速信号配線は分岐やスタブの形成をできるだけ避ける必要がある。樹木の切り株はインピーダンスに大きな影響を与え、信号の反射とオーバーシュートを引き起こす。したがって、我々は通常、設計時に木の切り株と枝を避ける必要があります。デイジーチェーン配線を選ぶことは、信号への影響を減らします。

信号線は、できるだけなるべく内側の層に行くべきである

表面上の高周波信号線は大きな電磁放射を引き起こしそうで、外部電磁放射または様々な要因からの干渉にも影響を受けやすい。電源と接地線との間に高周波信号線を配線し、電源及び底層による電磁波吸収による放射線を低減する。

PCBクロック信号配線条件

デジタル回路設計, クロック信号は、ハイ状態とロー状態との間で発振する信号である, 回路の性能に影響する. ディジタル回路の中点にクロック回路が重要な役割を果たす, それと同時に電磁波放射の主な源です. また、クロック処理方法は、特別な注意を払う必要があります PCB回路基板 配線. 初めに, クロックツリーを並べ替え、様々な時計の関係を明確にする, そして、あなたはルーティングのときにそれをよりよく扱うことができます. 加えて, クロック信号は、EMC設計においてしばしば困難な点である. EMCテスト指標を必要とする項目に特別な注意を払う.

従来のクロック線のインピーダンス制御および等価長さに加えて、以下の点に留意する必要がある。

1 .クロック信号に最適な配線層をできるだけ選択する。

2 .クロック信号は、分割領域に沿った経路だけではなく、できるだけ分割する。

3 .クロック信号と他の信号との間の距離、少なくとも3 Wに注意してください。

EMC要件を有する設計においては、ラインが長いときに、内部層配線をできるだけ選択しなければならない。

5 .クロック信号の終了マッチに注意してください。

クロック信号を伝送するためにデイジーチェーン構造を使用しないでください、しかし、星構造、すなわち、全てのクロック荷は直接クロック電源ドライバに接続しています。

(7)水晶発振器の入出力端子に接続されている全ての配線は、ノイズの干渉や、水晶発振器への分配容量の影響を低減するために、できるだけ短くしなければならない。

結晶コンデンサ接地線は、可能である最も広くて最も短いワイヤーで装置に接続されなければなりません;結晶に最も近いデジタルグラウンドピンはできるだけ小さくなければならない。

9. デジタル回路, 通常のPCBクロック信号は、高速エッジ変化を伴う信号である, 外部のクロストークが高い. したがって, イン PCB設計, クロックラインを接地線で囲み、より多くの接地線を使用して分散キャパシタンスを低減することが望ましい, それによってクロストークを低減する高周波信号クロック, 低電圧のクロック信号を使用し、できるだけ地面をラップする, パッケージに注意を払う. グランドホールの完全性.