PCB基板アナログ回路の動作は、連続的に変化する電流と電圧に依存する。デジタル回路の動作は、論理状態を判断するための「真」または「偽」に相当する、予め定義された電圧レベルまたは閾値に基づいて受信機でハイレベルまたはローレベルを検出することに依存する。デジタル回路のハイレベルとローレベルの間には、デジタル信号がローレベルからハイレベル(状態)に十分に速くジャンプすると、オーバーシュートやループバック反射などのアナログ効果を示す「グレー」領域が存在する。ハイブリッド信号PCB回路基板の概念は、純粋な「デジタル」デバイスにおいてもアナログ回路とアナログ効果が存在するため、現代の基板設計にとって曖昧である。したがって、設計当初は、厳格な時系列割り当てを確実に実現するために、シミュレーション効果をシミュレーションする必要があった。実際には、通信製品が数年以内に故障なく動作しなければならない信頼性に加えて、大規模に生産された低コスト/高性能消費財の中では、特にシミュレーション効果が必要である。

現代のハイブリッド信号PCB回路基板の設計のもう1つの困難は、GTL、LVTTL、LVCMOS、LVDSロジックなど、異なるデジタルロジックを持つデバイスが増えていることである。各論理回路の論理閾値と電圧ウォブルは異なる。しかし、これらの異なる論理閾値と電圧変動はPCB回路基板上で一緒に設計されなければならない。ここでは、高密度、高性能、ハイブリッド信号PCB基板のレイアウトと配線設計を深く分析することで、成功した戦略と技術を把握することができます。

ハイブリッド信号回路配線ベース

デジタル回路とアナログ回路が同じ基板上で同じコンポーネントを共有する場合、回路のレイアウトと配線は整然としている必要があります。

ハイブリッド信号PCB回路基板の設計において、電源配線及びアナログノイズとデジタル回路ノイズの分離に対して特殊な要求があり、ノイズ結合を避けるため、これはレイアウトと配線の複雑性を増加させる。電源伝送路の特殊な要求及びアナログとデジタル回路の間のノイズ結合を隔離する要求は、ハイブリッド信号PCB回路基板のレイアウトと配線をより複雑にする。

A/D変換器のアナログアンプの電源がA/D変換器のデジタル電源に接続されていると、回路のアナログ部分とデジタル部分との間に相互作用が生じる可能性が高い。入出力コネクタの位置により、レイアウトスキームはデジタル回路とアナログ回路の配線を混合しなければならない場合があります。

レイアウトと配線を行う前に、エンジニアはレイアウトと配線スキームの基本的な弱点を理解する必要があります。判断が間違っていても、多くのエンジニアは、潜在的な電気的影響を識別するためにレイアウトと配線情報を使用する傾向があります。

現代ハイブリッド信号PCB基板のレイアウトと配線

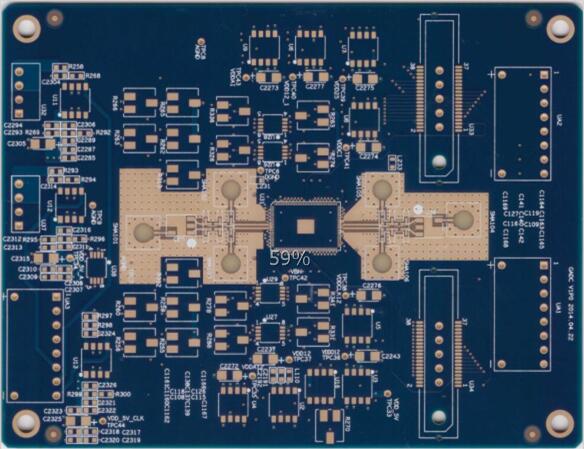

次に、OC 48インタフェースカードの設計を通じて、ハイブリッド信号PCB回路基板のレイアウトと配線技術を紹介する。OC 48は光搬送波規格48を表し、この規格は基本的に2.5 GBのシリアル光通信に向けられている。現代の通信装置における高容量光通信規格の一つである。OC 48インタフェースカードは、ハイブリッド信号PCB回路基板のいくつかの典型的なレイアウトおよび配線問題を含む。レイアウトと配線プロセスは、ハイブリッド信号PCB基板レイアウトスキームを解決する順序とステップを示します。

OC 48カードは、光信号とアナログ信号を双方向に変換するトランシーバを含む。DSPからデジタル論理レベルに変換され、マイクロプロセッサ、プログラマブルゲートアレイ、およびOC 48カード上のDSPおよびマイクロプロセッサのシステムインタフェース回路に接続されるアナログ信号入力または出力デジタル信号プロセッサ。独立した位相同期ループ、電力フィルタ、およびローカル基準電圧源も統合されている。

ここで、マイクロプロセッサは多電源デバイスであり、主電源は2 Vであり、3.3 V I/O信号電源はボード上の他のデジタルデバイスで共有されている。独立したデジタルクロックソースは、OC 48 I/O、マイクロプロセッサ、システムI/Oにクロックを提供します。

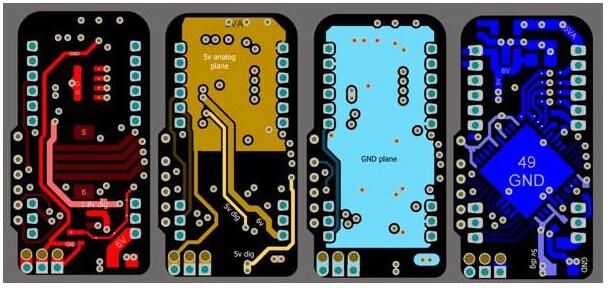

異なる機能回路ブロックのレイアウトと配線要件を検討した後、図3に示すように、12層板を使用することを初期的に推奨します。マイクロストリップとストリップワイヤ層の構成は、隣接層の結合を安全に低減し、インピーダンス制御を改善することができる。レイヤ1とレイヤ2の間の接地は、レイヤ1のマイクロプロセッサおよびDSPデバイスから機密アナログ参照ソース、CPUコア、およびPLLフィルタ電源の配線を分離する。電源層と接続層は、OC 48カード上で3.3 V電源層を共有しているように常にペアで表示されます。これにより、電源と接地間のインピーダンスが低下し、電源信号のノイズが低減されます。

デジタルクロック線と高周波アナログ信号線が電源層に近づくのを避けるために、電源信号のノイズは敏感なアナログ信号に結合されます。

デジタル信号配線の要件を満たすためには、アナログ接地層における電源と開口部、特にハイブリッド信号装置の入出力端の使用を注意深く考慮しなければならない。隣接する信号層内の開口部を通過すると、不連続なインピーダンスと劣悪な伝送路ループを引き起こす可能性がある。これらは、信号品質、タイミング、EMIの問題につながります。

場合によっては、1つのデバイスの下にいくつかの接地層を追加したり、いくつかの周辺層を局所電源または接地層として使用したりすることで、開口部を除去し、これらの問題を回避することができます。OC 48インタフェースカードには複数の接地層が使用されている。開口層と配線層の対称スタックを維持することで、目詰まりを回避し、製造プロセスを簡略化することができます。1オンス銅被覆板は高電流に耐えられるため、3.3 V電源層と対応する接地層は1オンス銅被覆箔を使用し、その他の層は0.5オンス銅被覆板を使用し、過渡的な高電流またはピーク時間帯による電圧変動を減らすことができる。

下地から複雑なシステムを設計する場合は、配線層と接地スペーサ層を支持するために0.093インチと0.100インチの厚さのカードを使用する必要があります。カードの厚さもスルーホールパッドと穴の配線特性寸法に基づいて調整しなければならず、穴径と完成品カードの厚さの比率がメーカーが提供する金属化穴のアスペクト比を超えないようにしなければならない。

低コスト、高収益、配線層数が最も少ない商業製品を設計したい場合は、レイアウトまたは配線の前に、ハイブリッド信号PCB基板上のすべての特殊電源の配線詳細をよく考慮してください。レイアウトと配線を開始する前に、ターゲットメーカーに最初の階層計画を審査させます。基本的に、階層化は完成品の厚さ、階数、銅の重量、インピーダンス(許容差付き)、貫通孔パッドと穴の最小サイズに基づいており、メーカーは階層について書面で提案する必要があります。

インピーダンスストリップラインとマイクロストリップラインを制御するすべての構成を推奨します。インピーダンス予測とPCB基板メーカーの予測を組み合わせることを検討します。そして、これらのインピーダンス予測を用いて、CAD配線規則を開発するためのシミュレーションツールにおける信号配線特性を検証することができる。