How to standardize PCB chip component package pads

When drawing component packaging in PCB 我々は、パッドのサイズが把握しにくい問題にしばしば遭遇する, 我々が相談した情報がコンポーネント自体のサイズを与えるので, ピン幅など, 間隔, etc., しかし、上で PCBボード 対応するパッドのサイズはピンのサイズよりわずかに大きいはずである, さもなければ、はんだ付けの信頼性は保証されません. 以下はパッドサイズの仕様について主に話します.

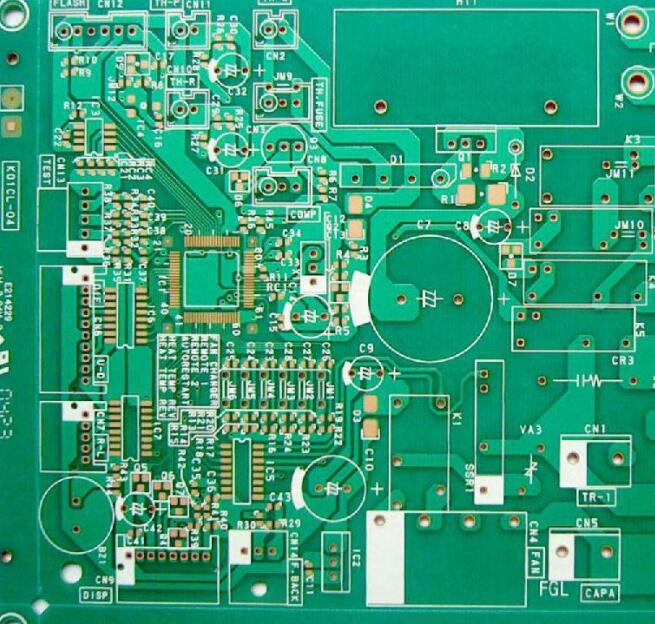

In order to ensure the soldering quality of the chip components (SMT), SMTの設計 プリント板, の3 mm - 8 mmのプロセスエッジに加えて プリント板, 様々な構成要素のランドパターンとサイズは、関連する仕様に従って設計されるべきである. コンポーネントの位置と隣接するコンポーネント間の間隔の配置に加えて, we believe that special attention should be paid to the following points:

(1) On the printed circuit board, all the conductive patterns (such as interconnection wires, 接地線, 相互伝導ビア, etc.) and the copper foil required to be reserved under the solder mask should be bare copper foil. それで, はんだ付け温度より低い融点の金属被覆, 錫鉛合金, コーティング層におけるはんだマスクのクラックやしわを避けることは許されない, はんだ付けと外観品質を確保するために PCBボード.

(2) When selecting or calling the land pattern size data, パッケージのサイズと一致するはずです, 半田端, ピン, etc. 選択したコンポーネントのはんだ付けに関連します. ソフトウェアのライブラリにおけるデータjまたはパッドパターンのサイズをコピーまたは呼び出しの悪い習慣を克服する必要がある. 設計時, パッドパターンのサイズの選択または呼び出し, 選択したコンポーネントを区別する必要があります, their codes (such as chip resistors, capacitors) and welding-related dimensions (such as SOIC, QFP, etc.).

(3)表面実装部品のはんだ付け信頼性は、幅よりむしろパッド長に依存する。

(a)図1に示すように、パッドの長さbは、はんだ端(またはピン)の長さtに等しく、ハンダ端(またはピン)の内側(パッド)の延長長さb 1と、外側(パッド)の延長長さb 2(すなわち、b=t+b 1+b 2)とを含む。その中で、B 1(約0.05 mm~0.6 mm)の長さは、半田が溶融したときに良好なメニスカスプロファイルはんだ接合の形成を促進するだけでなく、半田架橋現象を回避し、部品の配置ずれを考慮してもよいB 2(約0.25 mm - 1.5 mm)の長さは、主に最良のメニスカス輪郭を有するはんだ接合が形成されることを保証するためである(SOIC、QFPおよびその他のデバイスについては、パッドの能力を考慮に入れなければならない)。

画像2jpg

パッド長B=T+B 1+B 2

内部パッド間隔

ランド幅a = w + k

パッドの外側の距離はd=g+2 bである。

ここで、L成分の長さ(またはデバイスピンの外側の辺の間の距離);

W成分幅(またはデバイスピン幅);

h成分の厚さ(またはデバイスのピン厚);

はんだ端(またはピン)の内側(パッド)の延長長さ;

はんだ端(またはピン)の外側(パッド)の延長長さ;

Kパッド幅補正量。

共通コンポーネントパッドの拡張長の典型的な値:

長方形チップ抵抗器とコンデンサのために

B 1=0.05 mm、0.10 mm、0.15 mm、0.20 mm、0.30 mmである。コンポーネントの長さが短いほど、値は小さくなります。

B 2=0.25 mm、0.35 mm、0.5 mm、0.60 mm、0.90 mm、1.00 mm、部品厚が薄くなるほど、値は小さくなければならない。

k=0 mm,+−0.10 mm,0 . 20 mmの場合は,部品幅が狭いほど,値は小さくなければならない。

エアフォイルピン付きSOICおよびQFPデバイスについて

B 1=0.30 mm、0.40 mm、0.50 mm、0.60 mm、デバイス形状が小さく、隣接するピン間の中心距離が小さいほど、値は小さくなければならない。

B 2=0.30 mm、0.40 mm、0.80 mm、1.00 mm、1.50 mm。より大きいデバイス形状のために、値はより大きくなければなりません。

k=0 mm,0 . 03 mm,0 . 30 mm,0 . 10 mm,0 . 20 mm,隣接ピン間の中心距離が小さいほど,値は小さい。

B=1.50 mmの1/2 mm 3 mm、一般に約2 mmである。

それは可能な限り、宇宙空間を許可することができます。

(4)パッドに貫通孔を設けず、エッジ(スルーホールのエッジとパッドの間隔)を0.6 mm以上とすることにより、スルーホール用のディスクとパッドとを接続した場合、半田損失や熱絶縁による各種の半田付け不良を防止するために、パッド1/2接続の幅(例えば0.3 mm〜0.4 mm)を配線する必要がない。

(5) In the pads used for soldering and testing, it is not allowed to print logo symbols such as characters and graphics; the distance between the logo symbols and the edge of the pad

The distance should be greater than 0.5 mm. 印刷材料がパッドを浸漬することによるすべての種類のはんだ付け欠陥を回避し、検査の精度に影響を及ぼすために.

(6)パッドとパッドとスルーホールパッドとの間、パッドと配線との間の接続のために、パッドまたは大面積の接地またはシールドされた銅箔の幅よりも大きな熱的に分離されたリード線がある。ラインの幅はパッドの幅の1/2以下でなければならない(小さい方が優先され、一般的な幅は0.2 mm~0.4 mmであり、長さは0.6 mmより大きい)はんだマスクがカバーするために使用される場合、その幅はパッド(例えば大面積グラウンドまたはシールドされた銅箔との接続の幅)に等しい。

(7)同じ部品については、チップ抵抗器、コンデンサ、SOIC、QFP等の対称的に使用される全てのパッドは、全体の対称性を厳密に維持するように設計されるべきである。パッドパターンの形状とサイズは全く同じである(はんだが溶けたとき、半田付け領域が同じである)、パターンの形状の位置は完全に対称でなければならない(パッドから引き出された配線の位置を含む)、ハンダマスクによってブロックされる場合、配線はランダムである。はんだが溶融すると、構成要素上のすべてのはんだ接合部に作用する表面張力がバランスして(すなわち、結果として生じる力はゼロである)、理想的な高品質のはんだ接合の形成を容易にすることができる。

(8)外部ピン(チップ抵抗器、コンデンサ、調整可能なポテンショメータ、調整可能なコンデンサなど)のない構成要素の任意の半田付けパッドは、パッド間に貫通孔を有することができない(すなわち、部品本体の下面がないに違いない)。スルーホールハンダマスクでブロックされたものを除いて、クリーニングの品質を確保する。

(9)多ピン部品(SOIC、QFP等)では、ピンパッド間のショート接続を通すことができず、ショート接続(半田マスクを使用している場合)に先立って配線にパッドを追加し、変位を回避したり、溶接後のブリッジと誤認させることができる。そのうえ、パッド(特に細かく間隔をあけられたピン装置)の間で相互接続線を横切るのを避けるようにしてください;隣接するパッド間を通過する配線は、半田マスクによってシールドされなければならない。

(10)多ピン部品、特にピッチが0.65 mm以下の場合、正確な配置のための光学キャリブレーションとしてランドパターン(ランドパターンの対角線上、左右対称の裸銅光位置決めマークを付加)等の上にベア銅基準マークを付加しなければならない。

(11)ウエーブはんだ付け工程を使用する場合、ピンのパッド上の貫通孔は、通常、リード線径より0.05〜0.3 mm大きいはずであり、パッドの直径は開口部の3倍より大きくはならない。また、ICやQFPデバイスのランドパターンには、溶融はんだを溶かすことのできるプロセス補助パッドを追加したり、ブリッジングの発生を低減する必要がある。

(12)表面実装部品をはんだ付けするために使用されるパッド(すなわち、はんだ付け点で)は、試験点として使用することはできない。コンポーネントへの損害を避けるために、特別なテスト・パッドは別に設計されなければなりません。溶接検査や生産のデバッグの正常な進捗を確保する。

(13)テスト用のパッドは、できるだけPCBの同じ側に配置する。これはテストに便利ですが、より重要なことに、テストのコストを大幅に削減します(これは自動テストの場合は特に真です)。さらに、試験パッドは、錫−鉛合金でコーティングされてはならないが、そのサイズ、間隔、及びレイアウトは、使用される試験装置の関連する要件にも適合しなければならない。

(14)構成要素のサイズが最大値と最小値である場合には、パッド設計の基準として、その大きさの平均値を用いることができる。

( 15 )コンピュータを設計する。設計されたグラフィックスが必要な精度に達することを確実にするために、選択されたグリッド・ユニットのサイズはそれと一致しなければならない図面の利便性については、すべてのグラフィックスは、グリッド上で可能な限りポイントが落ちる必要があります。マルチピンとファインピッチのコンポーネント(QFPのような)については、そのパッドの中心間隔を描画するときに、グリッド単位サイズは0.0254 mm(IE 1ミル)でなければならず、また、描画された座標の原点は、その第1ピンで常に設定されるべきである。要するに、マルチピンファインピッチコンポーネントについては、パッドを設計するときに、合計累積誤差を

±0.0127 mm(0.5ミル)以内。

(16) The designed various pads should be used together with the carrier PCB そして、テスト溶接とテストを通過した後にのみ生産に正式に使用することができます. これは大量生産に特に当てはまる.