どちらの側面が 回路基板 デバッグ開始?

デジタル回路に関する限り, first determine three things in order

Confirm that all power supply values meet the design requirements. 複数の電源を有するいくつかのシステムは、電源の順序及び速度に対して特定の仕様を必要とする.

すべてのクロック信号周波数が適切に動作し、信号のエッジに非単調な問題がないことを確認する.

リセット信号が仕様要件を満たしているかどうかを確認する.

これらが正常ならば, チップは、サイクル信号を送出すべきである. 次, システムの動作原理とバスプロトコル.

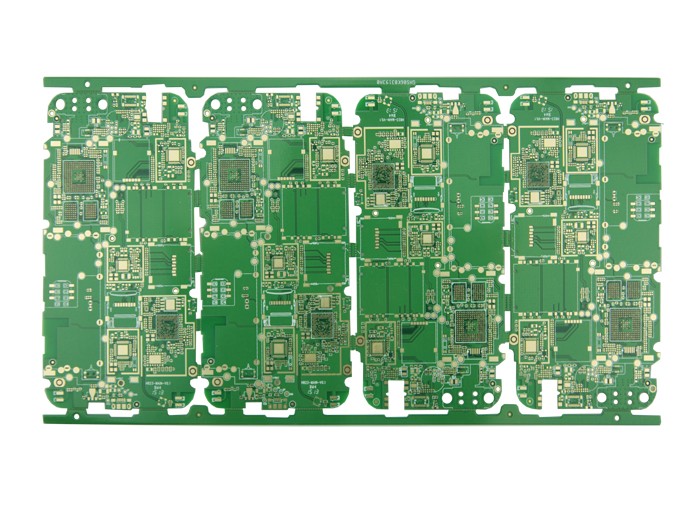

21. 固定の場合 回路基板 サイズ, if the PCB設計 より多くの機能を収容する必要性, PCBトレース密度を高めることがしばしば必要である, しかし、これは痕跡の相互干渉を増加させるかもしれません, それと同時に, トレースはあまりに薄く、インピーダンスを減らすことはできません, please introduce the skills in high-speed (>100MHz) high-density PCB設計?

設計時 高速PCB 高密度PCB, crosstalk interference (crosstalk interference) really needs special attention, それがタイミングと信号完全性に大きな影響を及ぼすので. Here are some points to note: 1). トレースの特性インピーダンスの連続性と整合性を制御する. 2). トレース間隔の大きさ. 共通の間隔は、線幅の2倍です. タイミングと信号完全性に対するトレース間隔の効果はシミュレーションによって既知である, と許容できる小さな間隔を見つけることができます. 異なるチップ信号の結果は異なることがある. 3). 適切な終了メソッドを選択. 4). 同じ配線方向に隣接する2つの層を避ける, 上下に重なる配線があっても, この種のクロストークが同じレイヤー上の隣接した配線のそれより大きいので. 5). 盲目を使う/痕跡面積を増やす埋込みビア. しかし, の製造コスト PCBボード 増加する.

実際の実装で完全な並列性と等しい長さを達成するのは、実際には難しい, しかし、できるだけそれをする必要があります. 加えて, 差動終端およびコモンモード終端は、タイミングおよび信号完全性に対する影響を軽減するために確保することができる.