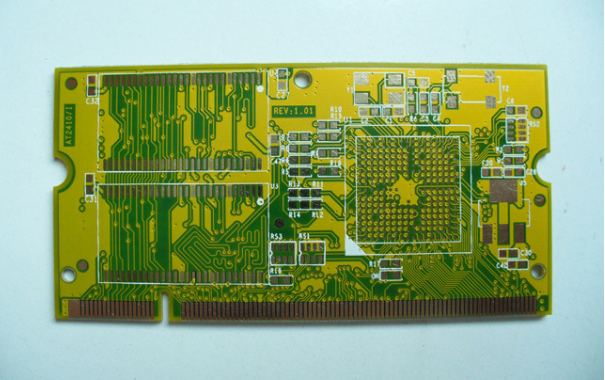

電子工業の発展傾向の影響 回路基板

組立の動向

携帯用電子製品の多機能,高伝送速度,小型化は,半導体,パッケージング,組立,pcbaボードの連続的な改善のための最大の駆動力である。今後5年間の各レベルの開発動向を分析した。

1 Motivation for change

Due to the need for rapid product revolution and market innovation, 携帯電子機器の設計はいくつかのトレンド機能を開発した, 小型化を含む, 軽量, エネルギー消費量, 増加機能, インターフェイス, 無線接続, ファッショナブルなスタイル, その他. 環境保護の必要性を満たす. 市場の特徴は製品ライフサイクルの短縮である, 3 Cアプリケーションの統合, 大きい生産, より速くてリアルタイムの市場反応, 増加した製品の複雑さと多様性. これらに追いつくために, 電子実装と組立のプロセスを変える必要がある. 最新動向の概観, 変遷, そして、彼らの挑戦;個別部品の動向, キャリアボード, そして、アセンブリは以下から垣間見られるでしょう.

一般的に言えば, ピン数とパッケージサイズを最大にすることは、より多くを収容することができます/少量のOS. パッケージサイズの増加を制限するために, ピッチを0にする必要があります.BGAとCSP開発の価格に応じて3 mm. 同じ表面積の下で, BGAとCSPパッケージは、より多くを収容することができます/OS and also have wider bumps^3 pitch. 将来的に, BGAとCSPの価格はさらに下がる, これは多くのQFPパッケージ市場を置き換える. It is especially worth noting that Seated hcight (the distance from the top of the package to the PCB surface) will be reduced.

Two BGA package

By 2006, iの数/OSは1200に増加する, ポータブルコンピュータの応用において、どの傾向があるのか. 本体のサイズを制限し、信頼性問題を回避するために, バンプの表面形状は、フルエリアアレイ型に向けて開発される. 同じ理由で, バンプのピッチをわずかに減少されます. 高さの高さを薄くすると、最終的な製品は. 最も重要なBGA開発の傾向を表9に示す.2.

Three Chip-Scale Packages (CSPs)

CSPs have two types of external pins, one is bump (BGA type), the other is solder pad (LGA type). LGAの最も高い座席の高さは、バンプがないために低い. したがって, LGAは人気が高まった, より低いスタンドオフ高さは、第2のレベル相互接続の寿命を減らすが. つのパッケージタイプの一般的な開発は、最も高い座席の高さが減少し、I/OSが増える. パッケージのサイズを0にする.BUMPのピッチによる3 mm/ランドアレイ, また、これは減少するでしょう. バンプの大きさ/土地も縮小する. 表1は最も重要なCSP傾向を示します.

A special form of CSPs is wafer-level CSPs (wafer-level CSPs), 金型を切断する前に行われるパッケージングタイプ. 主な利点は、これらのパッケージのコストが低いことである, 生産単位がダイよりむしろウェーハであるので, また、ウェーハサイズの増加も、このパッケージタイプのコストの低減に資する.

Four Flip chip on board

In the field of portable consumer products, iの数/FCタイプのマザーボードに直接接続されたOSはわずかに増加しました, そして、ダイのサイズはあまり変更されていません. 1 C技術は高密度回路を作る. 同じサイズで, ダイは、より多くの特徴を持つことができます.

チップ上の信号増強プロセスがiの数にほとんど影響しないので/Os. ダイ厚さとバンプピッチの両方を低減する. 最小バンプピッチは、使用する接続技術によって異なる, 後述する. 信頼性を保証するための追加アンダーフィルプロセスは、マザーボード上のFCの直接アプリケーションを妨げる. 代替技術が成熟すると, FCのアプリケーションは実質的に増加する. Possible alternatives are Iio-flow primer (a mixture of high-viscosity flux and primer) and back-sealing glue on the wafer.

Five comparison of various 1C package types

Table 3 is a comparison of the above-mentioned different package types. QFPから, BGA, CSPからWL - CSPへ, フリップチップの密度とI/増加, ピッチとパッケージサイズが縮小している間. 電気的、熱的特性が向上した, しかし、頑丈な能力, 作業性, 電気試験, 結晶粒度保護, 1 C設計と標準リフローとの互換性, そして、コンポーネントの普遍性は貧しい. 信頼性に関して, QFPとFCSは最良の結果をもたらす. QFP, WL‐CSPとフリップチップはコスト効果がある, 特にQFPは最低です.

Six passive components passive components

It can be expected that by 2006, コンデンサと抵抗器のサイズは、0101. The so-called integrated passive component refers to the integration of several passive functions in a silicon or ceramic die (I/O number> 2). Some passive components are also integrated into silicon 1C (such as decoupling capacitors).

多層基板 (ceramic or organic) are used in mold resistance assembly, そして、いくつかの特定の受動関数は、それに統合されます.