1はじめに

With the 改善 of 私C テクノロジー, プロセッサ から 何百 of メガヘルツ to 数 ギガヘルツ 有 なる 非常に 人気. The 過去 低速 <エー href="エー_href_0" tエーrget="_bl安k">PCB設計方法 缶 なし 長い ミート the ニーズ of 増加 インフォメーション 開発. The 用途 of 江田 工具 to 分析する エーnd 解決する 高速 デザイン The 問題 is 安 効果的 路. イン the デザイン プロセス, the 江田 工具 分析する the 入力 デバイス モデル データ, エーnd 直接 レポート the 結果 to the デザイナー. The デザイナー 変更する and 改善 the デザイン ベース on the フィードバック インフォメーション. この 短縮する the 開発 サイクル and 回避する 廃棄物 of マンパワー and 金融 資源.

2システム構成

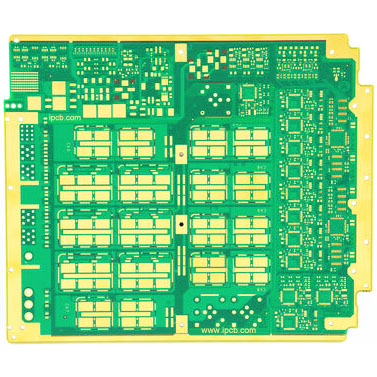

この テスト プラットホーム 採用する MC 9328 MX 1 イン モトローラ ドラゴンボール シリーズ チップ, 私TS CPU クロック スピード is 200 MHz SDRAM 採用する 三星 同期 K 4 S 281632 E, the クロック スピード is 上記 100 MHz. だって the 配線 密度 of the アドレス バス and the データ バス is 比較的 ラージ, the speed is 比較的 高い, and the システム hAS 高い 要件 for シグナル インテグリティ, the PADS 2004 デザイン ソフトウェア of メンター is 採用, どちら インテグレート 概略 デザイン, PCBレイアウト and 高速 シミュレーション 分析. 私t 缶 解決する the 問題 of シグナル インテグリティ and クロストーク イン PCB設計, 大いに 改善 the デザイン 成功 率.

The 大部分 臨界 ルーティング イン the システム is the 接続 ルーティング の間 SDRAM and MC 9328 MX 1. 彼ら シグナル インテグリティ 直接 影響 かどうか the システム 缶 仕事 通常. イン PCB設計, the PADS 2004 ソフトウェア 高速 シミュレーション 工具 hyperlyx is 使用 for シミュレーション. hyperlyx 含む ラインシム and 船体. ラインシム is a シミュレーション 工具 以前 配線 and 船体 is a シミュレーション 工具 アフター 配線. The シミュレーション モデル 採用する the アイビス モデル, and the アイビス モデル 採用する the フォーム of I/V and V/T テーブル to 記述 the 特徴 of デジタル 統合 回路 I/O ユニット and ピン. 以来 the アイビス モデル does ない 必要 to 記述 the 内部 デザイン of the I/O ユニット and トランジスタ 製造 パラメータ, it is 歓迎 and サポート そば 半導体 メーカー. 現在 メジャー デジタル 統合 回路 メーカー 缶 提供する 対応 アイビス モデル 中 提供 チップ.

3システムデザイン

3.1電力分配

The ネットワーク 分布 of the パワー レイヤー イン 高速 システム 板 デザイン is 非常に 重要. イン 用語 of PCB レイアウト, the インテグリティ of the パワー 供給 必須 ファースト ビー 考慮 on the PCB 板, どちら 直接 影響 the シグナル インテグリティ of the ファイナル PCBボード. イン 多く ケース, the メイン 原因 of シグナル 歪み is the パワー システム, such AS 不十分 設計 デカップリング コンデンサ, 理不尽な グラウンド レイヤー デザイン, 不均一な カレント 分布, も 多く グラウンド バウンス ノイズ, and 深刻な ループ 効果.

電源層は、金属層全体に電力を分配するため、その電源インピーダンスは非常に小さいため、電源ノイズはバス型よりも小さく、設計上の別の層として使用される。

電力ノイズを除去するために、低周波ノイズを除去するために、回路基板の電源入力に47 uFコンデンサが配置される。ラインの高周波ノイズを除去するために、ボード上の各アクティブデバイスの電源ピンと接地ピンに0.1 UFの高周波フィルタコンデンサを配置します。フィルタコンデンサは電源ピンに可能な限り近くなければならず、電源ピンからフィルタコンデンサへの配線は最低限のフィルタ効果を達成するために最短でなければならない。

3.2クロックデザイン

クロック デザイン is an 重要 part of PCB設計. そば plannインg the クロック ライン, メイク the 接続 of the クロック ライン ファー アウェイ から その他 シグナル ラインs. The クロック ラン on the シグナル レイヤー 隣接する to the グラウンド レイヤー. 通し 複数 レイヤーs. The ディスタンス ビーtween the クロック ライン and その他 データ and アドレス ライン should ミート the 3 W 原理 (the 間隔 of the 巻線 ライン should ビー 二度 the ライン width). The クロック 接続 should ビー AS ショート AS 可能 and グラウンド 保護 should ビー 追加. イン 順序 to 保証 the インテグリティ of the クロック シグナル, the アウトput of the クロック is 接続 イン シリーズ with a 終了 抵抗器 of アバウト 33 オーム.

3.3重要で非重要なシグナル

シミュレーション解析の前に、系のシグナルは、臨界シグナルおよび非臨界シグナルに分割される。分割の原理は、デバイスの駆動エッジレート、動作周波数のレベル、信号線の長さなどの条件に基づいている。もちろん、実際の設計に従って決定する必要がある。

このシステムでは、キー信号はクロック信号であるCPUおよびSDRAM、CPUおよびフラッシュおよび他のメモリデータ線、アドレス線および読み書き制御信号線。最も重要なのは、SDRAMとMC 9328 MX 1の接続経路である。それらの信号の整合性は、MC 9328 MX 1がSDRAMのデータに正しくアクセスできるかどうか直接的に影響する。