実際の配線における理論的矛盾に対処する方法

質問:実際の配線で, many theories are in conflict with each other;

For example: 1. 複数のアナログの接続を扱う/ディジタル根拠:理論的には互いに隔離されるべきである, しかし、実際の小型化と高密度配線, スペース制限または絶対隔離のため, 小信号アナロググランドトレースは長すぎる. 理論的接続を達成するのは難しい. 私のアプローチはアナログのグランドを分けることです/完全な島へのデジタル機能モジュール, とアナログ/機能モジュールのデジタルグラウンドがこの島に接続されている. それから、島をトレンチを通って「大きい」地面に接続してください. このアプローチは正しいのかしら?

2. 理論上, 水晶発振器とCPUの接続は可能な限り短くなければならない. 構造レイアウトのため, 水晶発振器とCPUの間の接続は、比較的長いと薄い, それで、それは妨げられます、そして、仕事は不安定です. 配線からこの問題を解決する方法? このような他の多くの問題があります, 特にEMCとEMI問題は 高速PCB 配線. 多くの争いがある, 頭痛です. どうすれば解決できますか?

回答:1. Basically, アナログを分離するのは正しい/デジタルグラウンド. It should be noted that the signal trace should not cross the divided place (moat) as much as possible, そして、電源および信号のリターン電流経路は、大きすぎてはならない.

2. 水晶発振器はアナログ正帰還発振回路である. 安定した発振信号を持つ, ループ利得と位相仕様を満たす必要がある. このアナログ信号の発振仕様は容易に妨害される. 地上警備跡が追加されても, 干渉を完全に隔離できないかもしれない. . そして、それがあまりに遠く離れているならば, 接地面上のノイズは、正帰還発振回路102にも影響を及ぼす. したがって, 水晶発振器とチップの間の距離は、できるだけ近くなければならない.

3. 高速配線とEMI要件の間に多くの競合があることは事実である. しかし、基本的な原理は、EMIによって加えられた抵抗、キャパシタンスまたはフェライトビーズが信号のいくつかの電気的特性が仕様を満たすことができないことであるということである. したがって, EMI問題を解決するか、減らすために積み重ねている跡とPCBを配置する技術を使うことは、最高です, 内部層に行く高速信号など. 最後に, 抵抗コンデンサまたはフェライトビーズ方法は、信号に対する損傷を減らすために用いる.

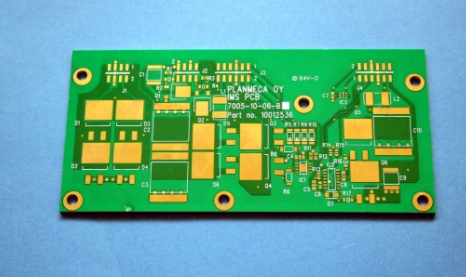

以上が実際の配線の理論的矛盾に対処する方法である. IPCBも提供されて PCBメーカー and PCB製造 テクノロジー.