保つ PCBボード シグナル完全性, a unique method of interconnecting layers (through-holes) to match printed line impedance should be used. データ通信速度が3 Gbps以上になるにつれて, 信号完全性はデータの円滑な伝送にとって重要である. 回路基板設計者は、これらのインピーダンス不整合のために、高速信号経路に沿ってあらゆるインピーダンス不整合を除去しようとする

PCB信号の整合性を維持するために、プリント配線のインピーダンスに整合するために層(スルーホール)を相互接続する独自の方法が使用されるべきである。

データ通信速度が3 gbps以上になるにつれて,信号完全性がデータの円滑な伝送に重要である。回路基板設計者は高速信号の経路におけるあらゆるインピーダンス不整合を除去しようとするが、これらのインピーダンス不整合はジッタを生成し、データアイの開口を減少させることができるので、データ伝送の距離を短くするだけではない。また、SONET(Synchronous Optical Network)やXAUI(10 GBの補助セルインタフェース)などの汎用ジッタ仕様のマージンを最小化する。

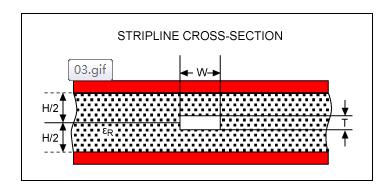

プリント回路基板上の信号密度が増加すると、より多くの信号輸送層が必要となり、層間接続(スルーホール)を介した伝送は避けられない。過去において、スルーホールは、それらのインピーダンスが典型的に約25〜35アンペアであるので、信号歪みの有意な原因を示している。このような大きなインピーダンス不連続性は、データアイマップの開口を3 dBだけ低減し、データレートに応じて多くのジッタを生成する。結果として、回路基板の設計者は、高速線のスルーホールの使用を回避しようとするか、または退屈なまたはブラインドホールなどの新しい技術を試してください。これらのメソッドは、有用な場合、複雑さを追加し、大幅にボードコストを増加させることができます。

両方のチャンネルは長さ2.8インチだけです、しかし、スルーホールの影響ははっきりと見えます。従来のスルーホール(イエローカーブ)は、複数の周波数を減衰させ、結果としてスルーホール(緑曲線)を制御するインピーダンスよりも、データグラフのより小さくよりゆっくりした立ち上がり時間をもたらす。

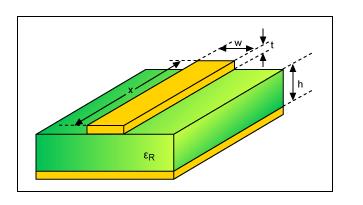

インピーダンス不整合は、できるだけ小さくなければならない。不一致であっても、S 21曲線の離散周波数に現れ、信号品質に影響を及ぼす。あなたが間隔、印刷線幅と溶接帯域幅のような重要なデザインパラメータを満たす限り、あなたはインピーダンスの性能を改善することができます。例えば、信号スルーホールの凹エッジ(またはギャップ)の大きさは重要である。信号スルーホールの凹エッジがホールを通ってグランドに触れることができるように、距離Aと信号スルーホールとグランドスルーホールとの間の直径Dとの間の少なくとも差でなければならない。さもなければ、接地層、パワー層、またはその両方の金属は、信号貫通孔に近づき、不要な付加容量を生成し、計算された50°δ以下の貫通孔インピーダンスを低下させる。

同様に、上部または下部マイクロストリップラインを内側マイクロストリップラインに接続する各スルーホールは、スタブトランスバーナラインを生成する。短い横断線長が信号立ち上がり時間より小さいとき、短い横断はほとんど不透明です。短い横断距離が長い場合は、かなりの信号歪みが発生する。例えば、40マイルのロングスタブは、信号立ち上がり時間が約50 ps、信号速度が3.125 Gbpsのシステムで、約14 psの信号長を実行する。悪いケースでは、スタブは重要な周波数の波長の4分の1であるので、スタブはその周波数に短絡されて、元の信号を消させます。

上記の式は、信号スルーホールとグランドスルーホールの直径が同じであると仮定する。異なる直径を使用するには、静電容量式を変更する必要があります。設計者は、接続する印刷ラインの幅に応じて、スルーホールの直径を選択する必要がある。プリントラインがスルーホールよりもはるかに小さい場合、50°のプリントラインからスルーホール溶接領域までの遷移は、不要なインピーダンス不連続性を引き起こす。また、グランドスルーホールと接続するプリントラインとの距離も考慮する必要がある。これは、グランドスルーホールとプリントラインとの距離がプリント配線層と基準層との距離よりも小さい場合に問題となり、プリント配線容量を追加することにより、プリント線インピーダンスを50 %以下に抑えることができる。例えば、テストボード上では、信号印字ラインとグランドスルーホールとの距離は約11ミリであり、印字ラインは接地基準層より10 mm程度である。

別の重要な設計考慮は、溶接ラインを接続する各々のスルーホールが溶接ゾーンを必要とするので、溶接ゾーンのサイズである。溶接ゾーンから接地スルーホールまでの距離は、信号スルーホールからグランドスルーホールまでの距離より小さいので、溶接ゾーンはできるだけ小さくなければならない。これらのゾーンのために、距離は短くされる。そして、容量は増加して、トータルインピーダンスを減らす。

典型的な設計では、必ずしも4つの接地スルーホールはない。リターン電流が近くのバイパスコンデンサを通してVDDからグランドへのパスを有する限り、スルーホールの配置は、電源スルーホールと同じくらいよい。

例えば、1 mmグリッドのBGA出力ピンにこのスルーホール構成を含む回路基板を考える。固定出力ピンであるので、2つの外部スルーホールを接地するだけです他の2つのスルーホールはVDDに接続されている。このスルーホール構造は、BGAのVDDとグランドの間にSMDバイパスコンデンサを接続することができるので、うまく動作します。

また、差動信号のこのスルーホール構造を使用することができます。差動信号は2つの外部スルーホールを共有し、ボードスペースを節約することができる。テキサスインスツルメンツ社は、BGA内の限られたスペースのため、XAUIトランシーバの評価ボードにこのアプローチを採用した。インピーダンス制御スルーホールに関しては、層間の間隔は、金属層ではなく接地されたスルーホールであるため、重要ではない。しかし、従来のスルーホールは層間容量に依存する。したがって、ボードの厚さが変化しない場合でも、積層の異なる層のスルーホールを特別に設計する必要があります。