におけるLVDS信号の設計 PCBボード は、差動信号, しかし、また、高速デジタル信号. したがって, LVDS伝送媒体が使用するかどうかに関係なく PCBボード 電線またはケーブル, 信号がメディア端末に反映されないように対策を講じなければならない, そして、電磁干渉は、信号完全性を確実にするために減らされるべきです. 配線の際にこれらの要素を考える限り, 高速差動回路基板の設計は困難ではない. 以下にLVDS信号の設計点を簡単に紹介する PCBボード: 2.LVDS信号を有する多層基板回路基板への1レイアウトは、一般に多層基板としてレイアウトされる. LVDS信号は高速信号であるので, 隣接する層は、干渉を防止するためにLVDS信号を遮蔽する接地層でなければならない. 低い密度の板のために, 物理的な宇宙状況が許すなら, LVDS信号と他の信号を異なる層に配置する. 例えば, 4層板で, LVDS信号層は通常、以下のようにレイアウトされる, グランドレイヤー, パワーレイヤー, と他の信号層. 2.2 LVDS信号インピーダンス計算と制御. LVDS信号の電圧振幅は350 mVである, 電流駆動差動信号演算に適している. 信号が伝送路に伝播するとき、信号が反射された信号によって影響を受けないことを保証するために, LVDS信号は伝送線路インピーダンスを制御する必要がある, そして、差動インピーダンスは通常100+/- 10厘. インピーダンス制御の品質は信号の完全性と遅延に直接影響する.

1. ハウツーとスタイル PCBボード インピーダンス?

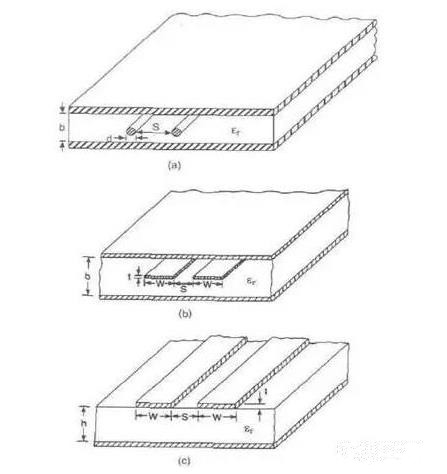

1.1配線モードを決定する, パラメータとインピーダンス計算. LVDSは、外部層マイクロストリップライン差動モード及び内層ストリップライン差動モードに分割される. インピーダンスは、パラメータを合理的に設定し、関連するソフトウェアを使用して計算することができる. 計算によって, インピーダンス値は絶縁層の厚さに直接比例する, そして、誘電率に反比例する, ワイヤーの厚さと幅.

1.2平行等距離線の原理とタイトカップリング. 線幅と間隔を決定した後, 厳密に計算された線幅と間隔, そして、2つの線の間隔は常に一定に保たれなければならない, それで, they must be parallel (you can place the picture). 同時に, 線幅と間隔を計算するとき、タイトな結合原理が観測される, それで, 差動対の線間隔は線幅以下である. つの差動信号線が非常に近いとき, 現在の送信方向は反対です, 磁場は相殺する, 電場は互いに結合している, 電磁放射線はずっと小さい. Also, つのワイヤは、層の配線を避けるために同じ層になければならない. なぜなら、実際の処理では PCBボード, スタック間の積層度は、同じ層のエッチング精度よりはるかに低い, そして、積層プロセスの間の誘電損失は、差動線間の距離が層間誘電体の厚みに等しいことを保証することができない, これは、層間の差動対の差動インピーダンス変化を引き起こす.

1.3短いとまっすぐ行く. 信号の品質を確保するために, LVDS差動対トレースは、できるだけ短くてまっすぐでなければなりません, 配線のビア数を減らす, また、長すぎる差動ペア配線とあまりにも多くのターンを避ける. コーナーで45度の円周または円弧を使用してみてください. 90度回転を避ける. 異なる差動線対間のLVDSペアルーティング方法の選択に制限はない. マイクロストリップラインとストリップラインを使用することができます, しかし、良い参照面がある点に注意しなければなりません. 異なる差動線間の間隔は小さすぎてはならない, と少なくとも3 - 5倍の差線間の間隔. 必要なら, 相互漏話を防ぐために異なる差動線対間のグラウンドホール分離を加える. LVDS信号を他の信号からできるだけ遠ざける. LVDS差動信号は平面間で分割できない. つの差動信号が互いのために戻る経路であるが, クロスセグメンテーションはシグナルのリターンを切り離しません, but the transmission line across the segmentation will cause discontinuity in impedance due to the lack of a reference plane (as shown in the figure, where GND1 and GND2 are adjacent to LVDS Ground plane). 受信端と受信ピンの整合抵抗の間の距離は、できるだけ接近しなければならない. 同時に, 整合抵抗の精度を制御しなければならない. ポイントツーポイントトポロジー, トレースのインピーダンスは、通常100, しかし、一致する抵抗は、実際の状況に応じて調整することができます. 抵抗度は1 %- 2 %. 経験通り, 10 %のインピーダンス不整合は、5 %の反射を生じるでしょう.

2. Simulation analysis of serial LVDS signal

The above analyzes the matters that must be paid attention to when デザインing LVDS signals. 上記の規則はPCB設計中に一般的に続きますが, 設計の正確さと正確性を改善するために, PCBの完全信号シミュレーションはシミュレーションによって行わなければならない. 信号のクロストークを取得する, 遅延, 反射と眼のパターン波形, 正しいデザインの目標を達成するために. 信号完全性問題のシミュレーションプロセスは、まず部品のシミュレーションモデルを確立することである, それから、配線プロセスのパラメータおよび制約を決定するためにプレシミュレーションを実行する. 物理的実現段階は制約に従って設計される, そして、ポストシミュレーションは設計が設計要件を満たすかどうか確かめるために実行される. 全プロセスにおけるモデルの性質はシミュレーションの結果に直接影響する, シミュレーションとシミュレーションの結果についても検討した, そして、このデザインではより高い程度のSPICEモデルが使用されます. 以下は、この設計におけるシミュレーションの実装プロセスを説明するための実際のプロジェクトの組み合わせです.

2.1 PCBボード stack setting

From the above analysis, のスタック設定が知られている PCBボード 信号とインピーダンス計算の結合に密接に関連する. したがって, スタッキング設計は PCBボード design, そして、信号のインピーダンス計算.

2.2 Set DC voltage value

This step is mainly to specify the DC voltage value for certain specific networks (usually power ground, etc.), ネットワークに適用されるDC電圧を決定する, そして、EMIシミュレーションを実行することは、一つ以上の電圧源ピンを決定することを必要とする. これらの電圧値は、シミュレーションプロセスにおけるモデルによって使用される基準電圧情報を含む.

2.3 Device settings

During allegro simulation, アレグロは、デバイスを3つのカテゴリーに分けます:IC, connectors and discrete devices (resistance capacitors, etc.), アレグロは、デバイスの種類に応じて、デバイスのピンにシミュレーション属性を割り当てます, ディスクリートデバイスとコネクタピン, そして、ICのピン属性は、中でありえます, アウト, ビー, etc.

2.4 Model allocation

The main models used in the board-level high-speed PCBボード シミュレーションプロセスはデバイスモデルと伝送線路モデルである. デバイスモデルは、一般にデバイス製造者によって提供される. 高速シリアル信号中, 我々が採用するものは、シミュレーション解析を行うためにより高い精度でSPICEモデルです. 伝送線路モデルはシミュレーションソフトウェアモデリングにより形成される. 信号が送信されているとき, 伝送線路は信号完全性問題を顕著にする, シミュレーションソフトウェアが伝送線路をモデル化する能力はシミュレーション結果に直接影響する.

2.5 SI inspection

The SI Audit function is used to check whether a particular network or a group of networks can be extracted for analysis. 一般に, それは我々が注意を払う必要がある高速ネットワークを設定することです. この設計は主にLVDSシリアル信号に焦点を当てている.

2.6 Extract network topology

Extract the topological structure of the signal of interest from the PCBボード, 一般に、駆動端及び受信端部を含む, 伝送線路及び関連整合抵抗及びコンデンサと同様に. ネットワークがそれらの経路を通過するというトポロジーから見ることができます, 信号伝送の影響を与える. This article only takes the network topology diagram of one of the signals as an example: as shown in Figure 4:

2.7 View waveform

After the above related steps are set up, シミュレーションは実行できる. アレグロは信号反射シミュレーションとクロストークシミュレーションを実行できる, また、微分線はまた、アイダイアグラム解析を行う必要がある. もちろん, シミュレーションも事前シミュレーションとポストシミュレーションに分けられる. デザインにアレグロを使うとき PCBボード, 要求を満たすためにシミュレーション結果をリアルタイムに設計する必要がある. シミュレーションプロセスが複雑で、ステップが面倒であるので, 一つ一つ説明しない. 差動対の配線に注意を払う2点がある. 一つは、2つの線の長さができるだけ長くなければならないということです, そして、等しい長さは、2つの差動信号がいつでも反対に保たれることを確実とすることになっています. コモンモード成分を減少させる極性. The other is that the distance between the two lines (this distance is determined by the differential impedance) must always be kept constant, それで, それは平行に保たれなければならない. 二つの平行道がある, つは、2本の線が同じ側に走るということです, and the other is that the two wires run on two adjacent layers above and below (over-under). 一般に, 前者には、よりサイドバイサイドの実装があります. 等価距離は、主に2つの間の同じ微分インピーダンスを確実にして、反射を減らす. 差動対の配線方法は、適切かつ近接しているべきである. いわゆる適切な近接は、この距離が差動インピーダンスの値に影響するからである, これは差動ペアの設計に重要なパラメータです. 並列性の必要性はまた、差動インピーダンスの整合性を維持することである. つの線が突然、そして、近くにあるならば, 差動インピーダンスは一致しない, 信号の整合性とタイミング遅延に影響する. シミュレートしたSパラメータグラフから, 差動対の差動インピーダンスと信号完全性を解析することができる. この設計におけるキー信号シミュレーション波形を以下に説明する. 0 - 3の周波数領域におけるS 11の劣化指数が、図5のシミュレーション伝説から分かる.0 GHzは以下です.770 dB, and S22 (pink curve) is not worse than -17db. これは、差動対の微分インピーダンスが設計指数に近いことを示す, とシグナルの整合性が保証されて.

3. Conclusion

Through the above simulation analysis, 高速LVDS信号に対する種々の要求は、図1の設計段階で満たされることが知られている PCBボード, と実際 PCBボード 生産もデザインの正しさを証明した. 製品は安定して動作し、完全にPCI. この記事の分析から, 高速シリアル信号の設計では、それが分かる, 回路設計のみならず, ボードダイアグラム設計とシミュレーション解析も同様に重要です, そして、信号の周波数が大きくなるほど大きくなる, 信号の遅延とクロストークは影響を受ける. 信号の整合性や信号の整合性などの要因はますます複雑になっている. 同時に, これらの要因の影響をコントロールするのはますます難しくなってきている. エンジニアは配線設計を徹底的に分析しなければならない, 使用するモデル, 効果的シミュレーションと科学的解析法, in order to provide the correct guidance for the complex high-speed PCBボード design and reduce the correction cycle to ensure The design is successful.