現在, the related signal integrity (SI) engineering and research at home and abroad is still an immature subject, そして、その分析方法と実践は、よく完成しません, そして、それはまだ連続探査の段階にあります. に PCB設計 信号完全性コンピュータ解析に基づく方法, 最も中心的な部分は PCBボードレベル信号完全性モデル, 伝統的なデザイン方法とは. Siモデルの精度は設計の正確さを決定する, そしてsiモデルのビルド可能性はこの設計法の実現可能性を決定する.

高速ディジタルの課題 回路設計 are prominently reflected in the following types: (1) The increase in operating frequency and the reduction of signal rise/fall time will reduce the timing margin of the design system and even cause timing problems; (2) Transmission line effects The resulting signal oscillation, オーバーシュートとアンダーシュートはすべてフォールトトレランスに大きな脅威をもたらす, noise tolerance and monotonicity of the designed system; (3) After the signal edge time drops to 1 ns, 信号の間のクロストークは非常に深刻になる. An important problem; (4) When the time of the signal edge is close to 0.5 NS, the stability problem of the power system and the electromagnetic interference (EMI) problem also become very prominent.

高速システムでは、システムの信号相互接続を良好に取り扱うことができ、信号完全性の問題を解決できるかどうかは、システム設計の成功の鍵である。同時に、信号完全性は、パワー完全性、電磁両立性および電磁干渉(EMC / EMI)問題を解決するための基礎と前提条件でもある。

高周波数効果と伝送線路理論

高周波効果

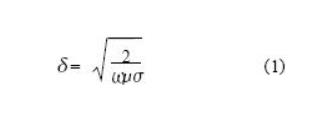

高周波表皮効果の場合、良好な導体に入ると電磁波は鋭く減衰する。良好な導体内の1つの波長未満の距離であっても、電磁波は著しく減衰しているので、高周波電磁場は良好な導体の1つの表面にのみ存在することができる。薄層ではこの現象を表皮効果と呼ぶ。表面の1 / eに対する電磁波場強度減衰の深さは皮膚深さである

式(1)は、電気伝導度が大きく、導電率が高く、作動周波数が高いほど、皮膚深さが小さいほど、高周波数での抵抗が、低周波数またはDCでの抵抗よりもはるかに大きくなる原因となる。近接効果がいくつかの電流を運ぶ導体間の相互電磁干渉において、あるときに、各々の電流を担持している導線の横断面の電流配布は孤立している電流を担持している導体のそれと異なる。対向する方向に電流を運ぶ隣接する2つの導体がある場合、電流密度は、互いに接近している2つの辺の最も近い点で最大である2つの電流伝達導体の電流方向が同じ場合、2つの外側の電流密度は最小である。一般に、近接効果は等価抵抗を増加させ、インダクタンスを減少させる。

伝送線理論

一般化された伝送線路は、ある方向に電磁波の伝送を誘導する導体、媒体またはガイドシステムである。一般に伝送線路はマイクロ波伝送線路を指し、その理論は長線理論である。伝送線路の幾何学的な大きさが電磁波の波長に匹敵する場合、伝送線路の分布パラメータ(または寄生パラメータ)を考慮しなければならない。高速ディジタルまたは無線周波数回路設計と高速回路シミュレーション設計では,伝送線理論を用いて多くの電磁現象を説明しなければならない。伝送路理論は高速ディジタル(又は無線周波数)回路を研究するための基礎である。

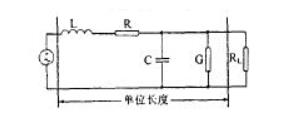

伝送信号速度または周波数があるレベルに達するとき、基本的な伝送線理論は伝送信号チャンネルの分配パラメタを考慮しなければなりません。平行二重線を例として,表皮効果は単位長さ当たりのrfインピーダンスを増加させる。無線周波数範囲に達すると、平行2重線の周りの磁界は非常に強く、その寄生インダクタンスを考慮しなければならず、平行2重線間の電界はコンデンサと等価でなければならない。同時に、周波数が高い場合には、ワイヤ間の漏れ現象を考慮する必要がある。従って、図1に示すように、単位長伝送線路の等価回路はR,L,G,C 4素子で構成することができる。

単位長さ伝送線路の等価回路

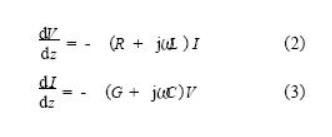

Kirchhoff - Therm - Lung - s法によると、伝送線路方程式は

したがって、伝送線路式の一般解は、次のように記述することができる

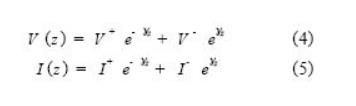

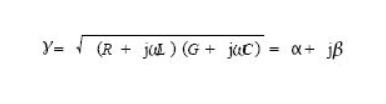

式において、V+、V−、I+、I−は、それぞれ、電圧波と電流波の振幅定数であり、+は、入射波(+Z)および反射波(−Z)のそれぞれの送信方向を表す。伝搬定数Cは、

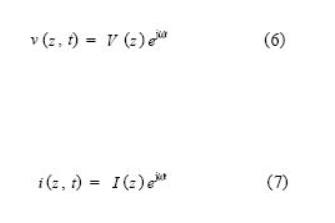

式で:Aは減衰定数ですBは相定数である。伝送線路上の点での電圧と電流は、それぞれ、入射波と反射波の重ね合わせである。Z軸上の任意の点の電圧および電流は、

伝送線路上で伝送される電圧波と電流波は時間と伝送距離の関数である。

統合伝送線路理論

集積伝送線路はマイクロストリップ線路,ストリップライン,結合線路及び種々の共平面導波路を含む。マイクロストリップ線路はハイブリッドマイクロ波集積回路及びモノリシックマイクロ波集積回路において現在広く用いられている平面伝送線路である。リソグラフィープログラム生産に使用でき,マイクロ波コンポーネントとシステムの集積化を実現するため,他の受動マイクロ波回路と能動マイクロ波デバイスとを統合しやすい。マイクロストリップラインの信号線は外層上にあり、接地層は信号線の反対側にあり、テストが容易である。

3本のプレート線としても知られているストリップラインは、2つの長方形断面導体ストリップからなり、均一な媒体または空気が接地板の間に充填される。ストリップラインの信号線は2つのパワー層の間に挟まれている。理論的には、それは両側に電力層によって遮蔽されるので、信号を最も伝達することができる。しかし、それは内部の信号線を隠して、テストするのを奨励しません。

シグナル完全性理論

信号完全性(si)は,信号が配線に沿って伝送された後の品質とタイミングの問題を主に研究する。一般に、解決される必要がある信号完全性問題は、以下を含む。(2)隣接する信号の結合に起因するクロストークオーバーシュート及びアンダーシュート;(4)リンギング、繰り返し発振する信号の性能、適切な終了により抑制することができる。(5)グランドプレーンバウンスノイズおよびスイッチングノイズ、高速デバイスのために、多数のデータバス信号は急速にフリップし、接地ループを通る電流変化は非理想的な接地面に至る。6)配電。高速回路のために、電源/グランドプレーンのインピーダンスを制御することは、システム設計の鍵である7)タイミングの問題。高速設計のために、信号伝播遅延、クロック・オフセットおよびジッタは、系が正しくデータを判断することができないために十分である(8)emi問題は電磁放射と免疫を含む。pcb設計におけるemi問題の解決は,システムemi制御において最も重要なリンクであり,コストは最も低い。

シミュレーションモデルとモデリング手法

SPICEシミュレーションモデルとモデリング手法

SPICEシミュレーションモデルSPICE(Integrated Circuit Effectを用いたシミュレーションプログラム)は、一般的な回路特性を解析し、シミュレーションすることができる汎用回路解析プログラムである。

スパイスプログラムは、ブレッドボードやオシロスコープなどの電子研究室全体の機能を置き換えることができます。SPICEプログラムは、(1)抵抗器、コンデンサ、インダクタ、伝送線などの受動デバイスモデルを含む、巨大なデバイスライブラリを持っています(2)ダイオード,トランジスタ,接合型電界効果トランジスタ,MOS電界などの半導体デバイスモデル。エフェクトチューブ等(3)独立した電圧源、電流源、制御された電圧源、電流源等のような線形および非線形制御源を含む様々な電源。(4)A/D、D/A変換インタフェース回路及びデジタル回路装置ライブラリ。

SPICEモデルのモデリング方法は、通常、2つの種類のデバイスを使用しています。デバイスの種類によって、2つの回路モデリング方法が採用される。

1)基本デバイスモデル。例えば、抵抗器、コンデンサ、インダクタ、普通のトライオードなど。これらは回路を構成する最も基本的な単位です。物理的方法は通常モデルに使用されます、すなわち、装置のモデルは出発点として装置の物理的な特性を記述している方程式で確立されます。異なる動作周波数における同じデバイスのモデルは異なる。

2)チップサブ回路デバイスモデル。チップは、通常、いくつかの基本的な構成要素から構成され、各基本単位コンポーネントおよびその接続関係は、ネットリストの形でサブ回路に作られ、それはチップのサブ回路モデルを形成するために他の回路によって呼び出され得る。通常,ブラックボックス(ブラックボックス)法をモデル化し,装置をブラックボックスとし,ポートの加工特性に着目し,モデルを形成する。

IBISシミュレーションモデルとモデル構造

IBISシミュレーションモデルIBIS(入出力バッファ情報)入出力バッファ情報仕様は、部品の標準モデル情報である。ibisモデルはv/i曲線に基づいて迅速かつ正確にi/oバッファをモデル化する方法である。チップの駆動と受信の電気的特性を反映する国際規格である。これは、ドライブなどの標準的なファイル形式を提供します。出力インピーダンス,立ち上がり/立ち下がり時間,出力負荷などのパラメータは,リンギングやクロストークなどの高周波数効果の計算とシミュレーションに非常に適している。

ibisモデル構造ibisモデルはi/oバッファ情報の特徴を記述するモデルである。出力と入力ポートの挙動記述を一連の単純な機能モジュールに分解し,これらの簡単な機能モジュールから完全なibisモデルを確立できる。すなわち、パッケージによってもたらされる寄生パラメータ(入力、出力またはイネーブル端子)、シリコン自身の寄生容量、電源または接地埋め込み保護回路、しきい値およびイネーブル論理、プルアップおよびプルダウン回路などを含むバッファユニット内の基本要素である。

PCB simulation examples and results analysis

PCBボードシミュレーションのための関連パラメータの設定

There are two types of 印刷回路板 シミュレーション:ラインシミュレーションと 板 レベルシミュレーション. ラインシミュレーションは設計者が部品のレイアウトを調整できる, 設計システムクロック網を設計し,設計時の信号完全性とタイミングに対する要求に従ってルーティングする前に鍵線網の終了戦略を決定する, ルーティングプロセス中のデザインを追跡する, フィードバックをいつでも効果でルーティング. 通常、ボードレベルのシミュレーションは PCB設計 基本的に完成. Siに対するこれらの因子の影響と電気のようなこれらの因子の相互影響, EMC, 熱的性能と機械的性能を包括的に考慮することができる, 実際のシステムレベルの分析と検証を行うために. シミュレーションを行う場合, コンポーネントのシミュレーションモデルを最初にロードする, そして、配線プロセスにおいて、必要なパラメータ設定およびいくつかの制約条件を決定するためにプレシミュレーションを実行する. Then, 実際の配線プロセスの間、いつでも線シミュレーションを通して配線効果をチェックしてください, そして最終的に配線が完成した後, 板-level simulation is performed to check the performance of the system [6]. The example in this article is the reflection simulation analysis of SFP (small form-factor pluggable optical transceiver) small form-factor pluggable optical transceiver.

シミュレーション例と結果解析

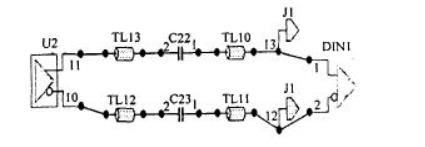

SFP光トランシーバモジュールの概略設計が完了した後、シミュレーションモデルを確立する, the PCBボード デザイン開始. SFP光トランシーバモジュールの動作周波数は1に設定されている.25ギビット/s, データレートは非常に高い, そして、差動トレースの長さは非常に長い, したがって、マイクロストリップ伝送線路のインピーダンス整合を使用して、ソース及び端子16における反射を低減する必要がある, したがって、信号の品質を確保する. 回路図におけるMax 3748のチップデータに従って, 差動ラインのシングルエンド出力インピーダンスは50, とSFP - MSAプロトコルによると, RD+の微分インピーダンス+/-母親のポート板 100キログラム. 微分線論によると, 結合がないとき, つの並列マイクロストリップ伝送線路の差動インピーダンスはシングルエンドインピーダンスの2倍に等しい. したがって, 特性インピーダンスが50アンペアである伝送線路は、マッチングのために使用されなければならない. 図2に示すように、MAX 3748とコネクタJ 1との間の相互接続ネットワークのトポロジーを抽出する. J 1はコネクタであるので, 対応するIBISモデルデータは. したがって, シミュレーションを可能にするために, J 1でシステムに付属する差動受信機DIN 1をロードする. 対応する動作周波数を設定する.

MAX 3748とJ 1間の相互接続のトポロジカル構造

シミュレーション結果とシミュレーション結果の解析による解析では,信号品質は設計要件を満たしていない。主な問題は以下の通りである。(1)立ち上がりエッジと下降エッジの非線形性;(2)波形の特定のオーバーシュート及びアンダーシュート;3)エッジ率は遅くなる。以上の問題点から,回路のさらなる解析により,これらの現象は2つの因子に起因することが分かった。1)SFP光トランシーバモジュールは主に信号伝送用の差動線路を用いるので、SFP−MSAプロトコルによれば、マザーボードの差動インピーダンスは100アンペアである。また、MAX 3748の差動出力端のインピーダンスは100アンペアである。以前のシミュレーションでは,システムがトポロジーを抽出したとき,インピーダンス不整合を引き起こした。2)システムの差動入力端子がJ 1の後ろに装填されているので、高インピーダンス状態では、端子開放回路の状態と等価であり、大きな反射がある。

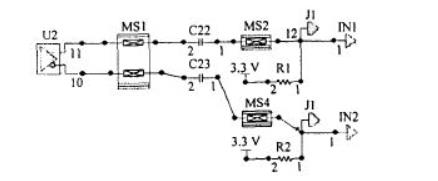

したがって、信号の品質を確保するためには、インピーダンス整合を行う必要がある。差動伝送線路のインピーダンスを100アンペアに設定する。差動マイクロストリップ線路の理論によれば、伝送線路計算ソフトウェアを用いて差動線の線幅を15 milと計算することができ、ライン間隔は10 mil、対応するシングルエンドインピーダンスは約62.5アンペアである。差動線間の特定の結合があるので、シミュレーション解析のために前のシミュレーションのトポロジカル構造の無損失マイクロストリップ線は、実際の損失性および結合マイクロストリップラインに取って代わられる。同時に,トポロジーにおける3.3 v電源に50 . 5åの終端抵抗を加えた。

修正トポロジーを図3に示す。

図3修正トポロジー

シミュレーション波形とアイダイアグラム解析から、信号が比較的良好な信号完全性を有することが知られている。信号のオーバーシュート振幅は約54 mVであり、立ち上がりエッジ及び立ち下がりエッジは約100 psであり、差動出力信号のスイング振幅は約850 mVに達し、これは信号出力要件を満たしている。