a. 以下のシステムは、反電磁気干渉に特別の注意を払うものとする

1 - 1 .マイクロコントローラクロック周波数は特に高く、バスサイクルは特に高速である。

1 - 2 .システムは、火花発生リレー、高電流スイッチなどのような高電力で高電流の駆動回路を含む。

1 - 3 .弱アナログ信号回路と高精度A/D変換回路を含むシステム

b .システムの反電磁干渉能力を高めるために、以下の措置を講じなければならない。

低周波数選択マイクロコントローラ

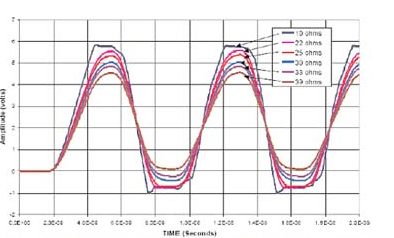

低い外部クロック周波数を有するマイクロコントローラを選択することにより、効果的にノイズを低減し、システムの干渉防止能力を向上させることができる。方形波と正弦波は同じ周波数で、方形波の高周波成分は正弦波よりも多い。方形波の高周波成分の振幅は基本波よりも小さいが、周波数が高いほどノイズ源として放散される。マイクロコントローラが発生する最も影響の大きい高周波ノイズは、クロック周波数の約3倍である。

2 .信号伝送における歪みの低減

マイクロコントローラは、主に高速CMOS技術によって製造される。信号入力端の静的入力電流は約1 mAであり、入力容量は約10 pFであり、入力インピーダンスはかなり高い。高速CMOS回路の出力端は、かなりの負荷容量、すなわちかなりの出力値を有する。ゲートの出力端が比較的高い入力インピーダンスで長い端を通して入力端に導かれるならば、反射問題は非常に重大です。tpd>trの場合,伝送路問題となる。信号反射やインピーダンス整合などの問題が考えられる。

プリント基板上の信号の遅延時間は、リード線の特性インピーダンス、すなわちプリント回路基板材料の誘電率に関係する。プリント基板のリード上の信号の伝送速度は、光の速度の1/3〜1/2であると大まかに考えられる。マイクロコントローラで構成されるシステムの共通の論理電話要素のtr(標準遅延時間)は3〜18 nsである。

プリント基板では、信号は7 Wの抵抗器と25 cmの長いリードを通過し、オンライン遅延時間は約4~20 nsである。言い換えれば、プリント回路の信号リードが短く、より良く、最長が25 cmを超えてはならない。さらに、バイアの数はなるべく少なく、好ましくは2以下であるべきである。[ URL ] href = www . 51 dz . com / d . asp . i = topmanazhi > >

信号の立ち上がり時間が信号遅延時間よりも速い場合、高速エレクトロニクスに従って処理する必要がある。このとき、伝送線路のインピーダンス整合を考慮する必要がある。プリント基板上の集積ブロック間の信号伝送にはtd>trdを避ける必要がある。プリント回路基板が大きくなればなるほど、システムが速すぎることはない。

プリント回路基板設計の規則を以下の結論で要約します。

信号がプリント基板上で送信されるとき、その遅延時間は使用されるデバイスの公称遅延時間より大きくない。

信号線間の交差干渉を低減する

A点の立ち上がり時間TRのステップ信号はリードABを介してB端に伝達される。D点では、点Aにおける信号の順方向送信、B点に到達した後の信号反射及びラインABの遅延により、Td時間後に幅Trのページパルス信号が誘起される。点Cにおいて、AB上の信号の送信及び反射により、AB線上の信号の遅延時間の2倍の幅を有する正のパルス信号が誘起される。これは信号間のクロス干渉です。干渉信号強度は,点c信号のdi/atと線間距離に関係する。つの信号線があまり長くないとき、あなたがABで見るものは実際に2つの脈の重ね合わせです。

cmosプロセスにより製造されたマイクロ制御は,高い入力インピーダンス,高い雑音及び高い雑音耐性を有する。ディジタル回路は100〜200 mvの雑音で重畳され,それはその仕事に影響しない。最初の模擬試験がAB信号なら、干渉は耐えられない。プリント配線板が4層板であり、一方がグランドの大面積、両面基板であり、信号線の裏面がグランドの大面積であると、信号間のクロス干渉が小さくなる。その理由は、信号線の特性インピーダンスが大きい領域で小さくなり、D端の信号の反射が大幅に減少するからである。特性インピーダンスは、信号線から接地への媒体の誘電率の二乗に反比例し、媒体厚さの自然対数に直接比例する。最初の模擬試験がABならば、ABへのCDの干渉は避けられるでしょう。AB線の下に広いエリアがあります。AB線からCDラインまでの距離は、AB線の接地よりも大きい。ローカルシールドグラウンドを使用することができ、リード線の側にリード線の左側と右側に接地線を配置することができます。

電源からのノイズの低減

電源がシステムにエネルギーを供給する間、それはまた、電源に電源を追加する。回路のマイクロコントローラのリセットライン、割り込みラインおよび他の制御線は、外部ノイズに最も弱い。電力網への強い干渉は、電源を介して回路に入る。電池式システムであっても、バッテリ自体は高周波ノイズを有する。アナログ回路のアナログ信号は、電源からの干渉に耐えられない。

5 .プリント配線板・高周波成分の高周波特性

高周波数では、リード、ビア、抵抗、キャパシタンス、コネクタの分布、インダクタンスおよびキャパシタンスは無視できる。キャパシタンスとインダクタンスの分布容量は無視できない。抵抗は高周波信号を反映し、リードの分布キャパシタンスは役割を果たす。長さがノイズ周波数の波長の1/20より大きい場合には、アンテナ効果が発生し、ノイズがリードを介して外部に送信される。

プリント回路基板のビアは、約0.6 pFの静電容量を発生する。

集積回路自体のパッケージング材料は、2〜6 pFのキャパシタンスを導入する。

回路基板上のコネクタは、520 nHの分散インダクタンスを有する。デュアルインライン24ピンICチップベースは、4〜18 nh分散インダクタンスを導入します。

これらの小さな分布パラメータは、低周波数のマイクロコントローラシステムには無視できる高速システムには特に注意が必要である。

6 .部品の配置は合理的に分割する

プリント基板上の構成部品の配置については、完全に電磁干渉を考慮しなければならない。原則の一つは、コンポーネント間のリードはできるだけ短くすることである。レイアウトでは、アナログ信号部分、高速デジタル回路部分、およびノイズ源部分(リレー、高電流スイッチなど)は、それらの間の信号結合を最小にするために合理的に分離されなければならない。

接地線の取扱い

プリント基板では電源コードと接地線が最も重要である。電磁妨害を克服する最も重要な手段は接地である。

両面基板に対しては特にグランド配線が特に好ましい。シングルポイント接地方式を採用することにより、電源とグランドとは、電源の両端と電源用の1接点とグランド用の1接点とからプリント配線板に接続される。プリント基板上には、リターン電源の接点に集まる複数のリターングランド線がある。いわゆるアナロググランド、デジタルグランド、ハイパワーデバイスのいわゆるオープニングは、配線が分離され、最終的にこの接地点に集められることを意味する。シールドケーブルは、通常、プリント回路基板の外側の信号に接続するときに使用される。高周波信号及びディジタル信号は、シールドケーブルの両端が接地されている。低周波アナログ信号用シールドケーブルの一端は接地されなければならない。

特に深刻な高周波ノイズを有するノイズや干渉や回路に非常に敏感な回路は、金属カバーで遮蔽する必要がある。

デカップリングコンデンサを使用します。

高周波数デカップリングコンデンサは、1 GHzの高周波成分を除去することができる。セラミックチップコンデンサや多層セラミックコンデンサは良好な高周波特性を有する。プリント回路基板を設計する際には、各集積回路の電源とグランドとの間にデカップリングコンデンサを追加しなければならない。デカップリングコンデンサは、2つの機能を有する。一方、集積回路のエネルギー蓄積コンデンサは、集積回路のドアを開閉する瞬間に、充電および放電エネルギーを供給し、吸収する一方、装置の高周波ノイズはバイパスされる。ディジタル回路における0 . 1 ufの代表的なデカップリングコンデンサは,5 nh分布のインダクタンスを持ち,その並列共振周波数は約7 mhzであり,10 mhz以下の雑音に対して良好なデカップリング効果を持ち,40 mhz以上の雑音にはほとんど効果がない。

1 uf,10 ufコンデンサ,20 mhz以上の並列共振周波数は,高周波雑音を除去する効果が良い。電源がプリント基板に入る場合には、1 UFまたは10 UFの高周波コンデンサを用いることが有利である。バッテリ駆動システムでさえ、このキャパシタが必要である。

つの充放電キャパシタまたは蓄積放電キャパシタは、10個またはそれ以上の集積回路ごとに追加される。容量は10 uFである。電解コンデンサを使わない方が良い。電解コンデンサは、2層のPU膜で巻かれている。この巻上げ構造を高周波インダクタンスとして示す。胆汁コンデンサまたはポリカーボネート醸造コンデンサを使うことは、最高です。

デカップリング容量値は厳密には選択されず、C=1/Fとして計算することができるすなわち、10 MHzを0.1μFとし、マイクロコントローラで構成されるシステムでは0.1〜0.01 UFとすることができる。

三番目, 雑音と電磁干渉の低減に関するいくつかの経験.

低速チップを使えば高速のものは必要ない。キーチップで高速チップを使用しています。

一連の抵抗器を使用して、制御回路の上下エッジのジャンプ速度を低減することができる。

リレーなどに何らかの減衰を与えるようにしてください。

システム要件を満たす最低周波数クロックを使用します。

クロックジェネレータは、クロックを使用してデバイスに可能な限り近いです。水晶振動子の殻は接地されなければならない。

接地線でのクロック領域とクロックラインは、できるだけ短くしなければならない。

I/O駆動回路は、できるだけ早くプリント基板を残すために可能な限りプリント板に近いものとする。プリント基板に入る信号をフィルタリングし、高ノイズ領域からの信号をフィルタリングする。同時に、文字列端子抵抗の方法を用いて信号反射を低減する。

MCDの無駄な端末は、ハイに接続されるか、または接地されるか、出力端子として定義される。集積回路上の電源接地に接続されているすべての端子は接続され、中断されない。

未使用のゲート回路の入力端は停止されず、未使用のオペアンプの正入力端は接地され、負の入力端は出力端に接続される。(10)プリント板は、高周波信号の外部伝送および結合を低減するために、できるだけ90本の破線の代わりに45本の破線を使用する。

プリント基板は、周波数および電流スイッチング特性に応じて分割され、ノイズ成分および非雑音成分は、より遠くになければならない。

単点接地電源及び単点接地は、単板及び両面板に使用する。電力線と接地線は、できるだけ厚くなければならない。手頃な価格であるならば、多層基板は、電源およびグラウンドの静電容量インダクタンスを減らすために用いる。

クロック、バスおよびチップ選択信号は、I/Oラインおよびコネクタから遠く離れていなければならない。

アナログ電圧入力ラインおよび基準電圧端子は、可能な限り、特にクロックまで、デジタル回路信号線から遠く離れていなければならない。

A / D装置の場合、デジタル部分とアナログ部分は交差するよりむしろ統一されるべきです。

I/O線に垂直なクロックラインは、平行I/Oラインより少ない干渉を有する。そして、クロック素子ピンはI/Oケーブルから遠く離れている。

素子ピンはできるだけ短くし、デカップリングコンデンサピンはできるだけ短くする。

鍵線はできるだけ厚くし、両側に保護区域を加えなければならない。高速線は短くてまっすぐでなければなりません。

ノイズに敏感な線は、大電流と高速スイッチング線と平行ではない。

水晶の結晶と雑音に敏感な装置の下で線を配線しないでください。

弱い信号回路と低周波回路の周りに電流ループを形成しない。

任意の信号のループを形成しないでください。必然的にループ面積をできるだけ小さくしておく。

ICあたり1個のデカップリングコンデンサ。各電解コンデンサには、小さな高周波バイパスコンデンサを追加しなければならない。

回路容量と放電エネルギー貯蔵コンデンサとして電解コンデンサの代わりに高容量タンタルコンデンサまたはポリクールコンデンサを使用してください。管状コンデンサを使用する場合、シェルは接地される。