低コストのPCB(プリント基板)を使用すると、ほとんどのCADソフトウェア(フリーソフトウェア)の基板を数時間で簡単に設計できます。2日でテーブルの上で原型板を完成させることができます。多くのパッケージには良い設計規則があります。ほとんどのPCBメーカーは、0.006インチ以下の線幅と線間隔を製造することができます。

この精度は低周波回路には問題ありませんが、無線周波回路は通常50個の島配線を必要とします。部品の体積はますます小さくなりますが、物理法則は変わりません。そのため、30年前の0.11インチに比べて、今日の0.062インチ厚の原型板上のマイクロストリップ線の幅は0.11インチである。しかし、多くのSMT(表面組立技術)コンポーネントは、前世代コンポーネントよりもはるかに小さい。したがって、無線周波数プロトタイプのための低コストのデュアルパネルは、今日の小型SMTコンポーネントには適していないようです。

cpwg(接地共面導波路)構造を用いて、PCB上に50個の無線周波数配線を製造することができる。Cpwg構造は所望の経路を生成することができ、その幅はマイクロストリップ構造の幅より小さい。

天板上の接地銅箔はマイクロストリップワイヤに近く、これによりマイクロストリップ構造の容量が増加する。構造全体を50°に補償して保持するためには、中心配線幅をある程度小さくして、より高いインダクタンスを持たせる必要があります。

低コスト、高速PCBプロセスのcpwg構造をどのように設計しますか。インターネット上には多くのcpwg計算機が見つかりますが、地層間隔がルーティング幅の30%未満の場合は?50%では、基板上の銅箔配線の高さが重要な要素になるため、これらの計算機は失敗します。計算機が想定しているよりも容量が増加しています。そのため、これらの計算機が設計したルーティングは高すぎる容量を持ち、そのインピーダンスを50島以下に低下させた。これらの公式は、数年前のIC設計にさかのぼることができる。

今日のPCBとICは本質的に異なるため、多くの計算機の数式は使用できません。狭いピッチ中心線比を有するcpwgをPCB上で正しく設計するための最良の方法は、全3次元電磁シミュレータを使用することである。この例では、一般的な構造の値をいくつか提供します。

最小配線間隔を6ミルに維持し、cpwg構造をシミュレーションし、製造し、テストしました。一般的な厚さ0.062インチのFR-4 PCB材料では、幅0.032インチ、間隔0.006インチの配線が50島に最も近い。6 GHzでは、ルーティングラインのエコー損失は40 dBより優れている。

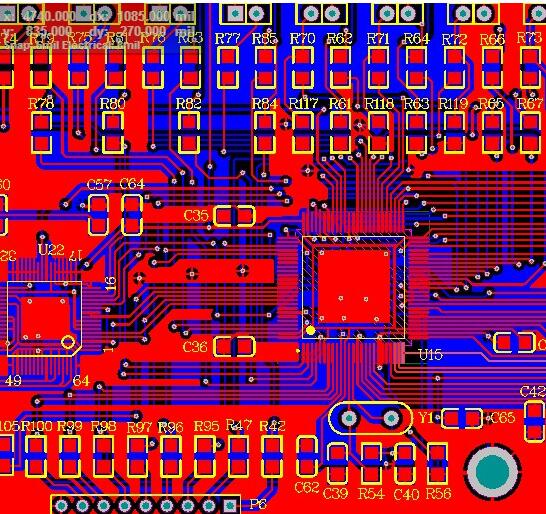

この方式は0.11インチ幅配線の方法より優れており、SMT素子と互換性がある。0603サイズのSMT素子と一般的なSMA(表面実装アセンブリ)プレートエッジコネクタは、このワイヤに完全に適合することができる。図1は、様々な一般的な無線周波数コンポーネントを準備されたPCBと比較したものである。パッドサイズが0.032インチの配線幅より大きい部品については、天板と接地する隙間を増やすことで補償することができます。例えば、トップクリアランスを0805 SMTパッドから約0.008インチに増加させ、1206 SMT素子パッドを0.012インチに増加させることで、パッド容量が大きすぎるのを防ぐことができる。

一般的な設計規則を守るために、銅箔をテストPCB上に敷設された回路基板の縁から0.01インチ後ろに引いた。しかし、このプルバック式とプレート側に取り付けられたコネクタは、変換に少量のインダクタンスを増加させた。線路端のプレート側コネクタの中間の太いピンは、内蔵容量補償を提供するために追加の容量を増加させる。ピンを元の長さの約半分に短縮することで、インダクタンスを平衡変換するための近似的に等価な容量を得ることができる。

Cpwg構造は配線の下に堅固な接地面を持つ必要がある、上部配線の下の底部に開口部を残すと、構造に大きなインダクタンスが加わり、高周波性能が低下します。さらに、上部地面と下部地面を「縫合」するためには、いくつかのオーバーホールを使用する必要があります。このような縫合孔の配置は、回路が使用する最高周波数波長の8分の1を超えてはならない。0.1インチの間隔は10 GHz以上の周波数でよく動作することに注意してください。

縫合穴から中心線までの間隔は同じ間隔規則に従う。正常な動作のために十分なビアを配線線に容易に配置することができる。

十分なビアがなければ、周波数に伴う線形損失勾配ではなく、S 21の輸送特性に0.5 dBから1 dBの小さいが急速な低下が見られる。VNA(ベクトルネットワークアナライザ)を使用すると、この効果をすぐに見ることができます。テストボードの測定により、2つのボードエッジコネクタを含めて、3 GHzと10 GHzでの損失はそれぞれ約0.25 dB/inと1 dB/inであることが明らかになった。

SMTデバイスまたはICを幅0.032インチ未満のパッドに接続する場合は、必要に応じて中心導体を縮小し、できるだけデバイスに近づけてください。実際の不連続性が小さい場合、周波数がそれほど高くない場合、その影響は無視できます。