なぜ良い PCBレイアウト 重要?

すべての2.5 cmのPCBトレースは、約20 nhのトレースインダクタンスを有する。正確なインダクタンス値は、トレースの厚さ、幅、および形状に依存するが、経験に基づいて、通常、20 nh/2.5 cmを取ることが可能である。バックレギュレータが5 Aの出力電流を提供すると仮定すると、電流スイッチは0 Aから5 Aになる。スイッチング電流が大きく、スイッチング遷移時間が短い場合、以下の式を使用して、小さなトレースインダクタンスを計算して、どれだけの電圧オフセットが発生されるかを計算することができる。

ワイヤ長が2.5 cm(20 nH)とすると、出力電流は5 A(バックレギュレータの5 Aスイッチング電流)であり、MOSFETパワースイッチのスイッチング時間は30 nsであり、電圧オフセットは3.33 Vとなる。

2.5 cmだけのトレースインダクタンスがかなりの電圧オフセットを生じることが分かる。このシフトは、しばしばスイッチモード電源の完全な故障につながる。スイッチングレギュレータの入力ピンから数cm離れたところに入力コンデンサを配置することは、通常、スイッチング電源が動作しないようにする。不適切なレイアウトを有する回路基板では、スイッチング電源がまだ動作することができれば、それは非常に大きな電磁干渉(EMI)を生じる。

上記式において、変更可能な唯一のパラメータはトレースインダクタンスである。トレースインダクタンスを低減するためにトレースをできるだけ短くすることができる。より厚い銅線も、インダクタンスを減らすのを助けます。負荷によって必要とされる電力が固定されるので、電流パラメータを変更することはできない。変換時間については、変更することができますが、一般的に変更する必要はありません。スイッチング時間を遅くすることによって生成される電圧オフセットを低減することができ、それによってEMIを減少させることができるが、スイッチング損失は増加し、より低いスイッチング周波数で動作しなければならず、高価で嵩高な電力デバイスを使用しなければならない。

AC現在のトレースを見つける

スイッチモード電源のPCBレイアウトでは、最も重要な基準は、ACトレースをできるだけ短くする方法である。慎重にこの規則に従うことができれば、良い回路基板レイアウトは80 %成功したと言える。これらのACSを見つけて、「完全電流」から「電流なし」まで電流を短い時間(変換時間)ルートで変化させるために、回路図を3回描画します。簡単な降圧スイッチモード電源です。上部の概略図では、オン時間の間の電流の流れが破線で描かれている。中央の回路図では、オフ時間の間の電流フローを破線で描画します。下部の回路図は特に注目に値する。ここで、電流がオンからオフに変化する全てのトレースを描画する。

この方法を通して、任意のスイッチモード電源トポロジーのAC電流トレースを簡単に見つけることができます。

既存の回路基板のレイアウトとルーティングを評価するとき、良い方法は紙にそれを印刷して、透明なプラスチック板を置いて、それから開いている時間と閉鎖時間の間に電流を引くために異なる色のペンを使用することです。流れ方向と対応する交流配線。我々はこの比較的単純な仕事が我々の心でされることができると思う傾向がありますが、我々はしばしば思考過程で若干の小さな間違いをします。したがって、紙に線を引くことを強く推奨します。

良いPCBレイアウトとルーティングを実現

バックレギュレータの交流配線いくつかの接地トレースは、ACトレースであり、また、できるだけ短く保たれる必要があることに留意されたい。加えて、これらのAC電流経路のために、ビアのインダクタンスも非常に高いので、いかなるビアも使用しないことを推奨される。この規則には例外がほとんどない。AC経路がビアを使用しない場合、それは実際にビア自体より大きいトレースインダクタンスを引き起こすので、それはviasを使うことを勧められます。並列の複数のビアは、単一のビアだけを使用するよりよいです。

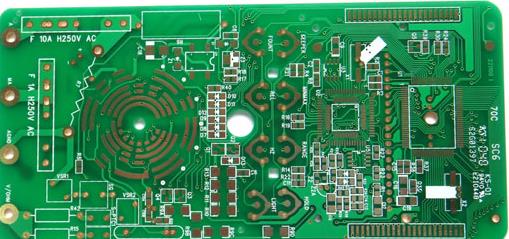

ADP 2300降圧レギュレータを用いた回路基板のレイアウト例図のAC配線が絶対最短経路に従ってレイアウトされているかどうかをチェックする。

接続Aは最短経路でレイアウトされている。なぜなら、C 2の高側接続はスイッチングMOSFET(ADP 2300のピン5、すなわちVINピン)に最短のトレースで接続できるからである。

接続Bは、ダイオードD 1のピン6(SWピン)とカソード側との間のトレースである。また、トレースインダクタンスを減少させるために、トレースはできるだけ短いことがわかる。

接続CはダイオードD 1のアノードとC 2の接地接続の間のトレースである. The PCBパッド これらの2つのデバイスは互いに隣接しており、最小のインダクタンス. 加えて, また、AC電流は、静かな接地面を通過しない. 接地面は基準電圧としてのみ使用すべきである, and preferably no current (especially no AC current) flows through the ground plane. C 2の隣のビアは、PCBの一番上の層の接地領域を底部の層に接地する, しかし、これらのビアを通してAC電流は流れない.

インダクタンス

EMIではインダクタンスも考慮する必要がある。実際の装置は多くの人が考えるほど対称ではない。インダクタは磁気コアを有し、磁気コアはワイヤを取り囲む。巻線は常にスタートエンドとエンドエンドを有する。開始端はインダクタの内側巻線に接続され、エンドエンドはインダクタの外側巻線に接続される。巻線の開始は通常、デバイス上のドットでマークされます。スタートエンドをノイズの多いスイッチングノードと終わりの端に静かな電圧に接続することは非常に重要です。降圧レギュレータでは、静かな電圧は出力電圧である。このように、外側巻線の固定電圧は、内側巻線の交流スイッチノード電圧を電気的に遮蔽することができ、電源のEMIが低くなる。

なお、いわゆるシールドインダクタは同じである。ある種の透磁率を有するシールドインダクタの外側は、特定の遮蔽材料を使用しており、パッケージ側の磁力線の大部分を締め付ける。しかし,この材料は電場ではなく磁場を抑えることができる。外部巻線の交流電圧は主に電気的または容量的結合による問題であり、シールドインダクタの遮蔽材料はこのような結合を阻害しない。したがって、シールドインダクタは、ノイズの多いスイッチングノードを巻線の開始に接続してEMIを最小にする回路基板上に配置されるべきである。

スイッチモード電源用の良好な回路基板レイアウトの基礎

エンジニアリングコースは、一般に良い回路基板レイアウトを達成する方法を教示しない. 高周波RFコースはトレースインピーダンスの重要性を研究する, しかし、彼ら自身のシステム電源を構築する必要があるエンジニアは、通常、高周波システムとして電源を考慮しません,基板レイアウトの重要性を無視とルーティング. 不適切な回路基板のレイアウト及び配線に起因する問題の大部分は、制御されないAC電流トレースに対して可能な限り短く且つコンパクトであると考えられる. この記事で説明された回路基板のレイアウトガイドラインの背後にある理由を理解し、それらを厳密にフォローしても PCB設計スイッチモード電源の関連事項.