PCBボードを作るには、うまく設計されたPCBの回路図をリアルに変えることですPCB回路 基板. このプロセスを過小評価しないでください. 工学では実現するのが難しいが、原理的に働くものが多い, または他の人は、同じことを実現することはできません達成することができますて, だから、PCBボードを作るのは難しくない, しかし、PCBボードをよく作ることは容易ではない.

マイクロエレクトロニクス分野における2つの大きな困難は高周波信号と弱信号の処理である。この点で、PCB生産のレベルは特に重要です。同じ原理設計、同じ構成要素、および異なった人々によって作り出されるPCB基板は異なった結果を持ちます。どうすれば良いPCBボードを作ることができますか?過去の経験に基づいて、次のような観点から意見を述べたいと思います。

設計目標の明確化

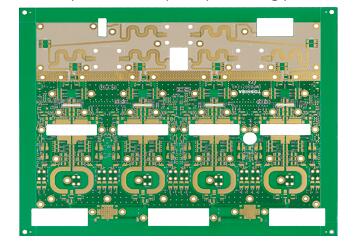

設計課題を受信するには、通常のPCBボード、高周波PCBボード、小型の信号処理PCBボード、PCBボード、高周波信号と小信号処理の両方を備えた設計目標を明らかにしなければならない。通常のPCBボードであるならば、レイアウトと配線が合理的で、きちんとしていて、機械的な寸法が正確である限り、中負荷ラインと長線がある場合、負荷を減らすために特定の処置を使用しなければならず、長いラインを駆動するために強化しなければならず、焦点は長線反射を防止することである。

40 MHzを超える信号線がボード上にあるとき, これらの信号線には特別の配慮が必要である, 線の間のクロストークのような. 頻度が高いならば, 配線の長さは厳しい. 分布定数のネットワーク理論による, 高速回路とその配線間の相互作用は決定的要因であり、システム設計において無視することはできない. ゲート伝送速度が増加するように, したがって、信号線の反対は増加するでしょう, そして、隣接する信号線間のクロストークは、比例的に増加する. 一般に, 高速回路の消費電力と放熱性も非常に大きい, だから 高速PCBされている. 十分な注意を払うべきだ.

ミリボルトまたはマイクロボルトレベルの弱い信号がボード上にあるとき、これらの信号線は特別な注意を必要とする。小さい信号は弱すぎて、他の強い信号からの干渉に非常に影響されやすい。遮蔽対策はしばしば必要である。さもなければ、それらは信号対雑音比を大いに減らす。その結果、有用な信号はノイズによって沈静化され、効果的に抽出することができない。

委員会のコミッショニングも設計段階で考慮すべきである。テストポイントの物理的位置、テストポイントの分離および他の要因は無視されることができない。なぜならば、若干の小さいシグナルおよび高周波シグナルは直接測定のためのプローブに添加されることができない。

さらに、基板の層数、使用する部品のパッケージ形状、基板の機械的強度など、他の関連する要因を考慮すべきである。PCBボードを作成する前に、デザインのデザイン目標について良いアイデアが必要です。

使用するコンポーネントの機能のレイアウトとルーティングの要件を理解する

LOTIとAPHによって使用されるアナログ信号増幅器のようなレイアウトとルーティングに特別な要件がいくつかの特別なコンポーネントを持っていることを私たちは知っています。アナログ信号増幅器は、安定した電源および小さなリップルを必要とする。可能な限りパワーデバイスから遠く離れたアナログ小信号部分を保ってください。otiボードでは,小信号増幅部もまた,シールド電磁シールドをシールドするシールドカバーを備えている。ntoiボードに使用されているglinkチップは,ecl技術を使用しており,多くの電力を消費し発熱を生じる。レイアウトにおける放熱問題に特別な考慮が必要である。自然の放熱が使用されるならば、GLinkチップは比較的スムーズな空気循環で場所に置かれなければなりません。そして、放射される熱は、他のチップに大きな影響を与えません。ボードがスピーカーまたは他の高出力装置を備えているならば、それは電源に重大な汚染を引き起こすかもしれません。この点も十分注意しなければならない。

コンポーネントレイアウトの考察

構成要素のレイアウトにおいて考慮されなければならない第1の要因は電気的性能である。いくつかの高速線のために、特に、電源信号と小さな信号装置をレイアウトするとき、できるだけ短くそれらを作る。分離する。回路の性能を満たす前提では、コンポーネントをきちんとして美しく、簡単にテストする必要があります。ボードの機械的サイズとソケットの位置も注意深く考慮する必要があります。

高速システムにおける配線の接地と伝送遅延時間は,システム設計において考慮すべき第一の要因でもある。信号線の伝送時間は、システム全体の速度、特に高速ECL回路に大きな影響を与える。集積回路ブロック自体が非常に高速であるが、それはバックプレーン上の通常の相互接続ラインの使用のためである。シフトレジスタおよび同期カウンタのような同期作動部品は、同じプラグインボード上で最もよく配置される。なぜなら、異なるプラグインボード上のクロックは信号伝送遅延時間が等しくないので、シフトレジスタが大きなエラーを発生させることがあるからである。それが1台のボードに置かれることができないならば、同期がキーであるところで、各々のプラグイン・ボードに共通の時計源からのクロック線の長さは等しくなければなりません。

配線の考察

OTNIとスター光ファイバネットワークの設計が完了すると、将来的に設計される必要がある100 MHz以上の高速信号線を持つボードが多くなる。高速線の基本概念を紹介した。

伝送路

印刷されたPCB上のどんな「長い」信号経路も、PCB伝送ライン線の伝送遅延時間が信号立上り時間よりずっと短いなら, 信号の上昇期間中に発生した主反射は、沈み込まれる. オーバーシュート, 反跳とリンギングはもはや存在しない. 電流MOS回路の大部分は, 立ち上がり時間とライン伝送遅延時間との比は、より大きい, トレースは、信号の歪みなしでメートルと同じくらい長くすることができます. 高速論理回路, 特に超高速.

集積回路の場合、エッジ速度の増加のため、他のいかなる処置もとられない場合、シグナルの完全性を維持するためにトレースの長さを大幅に短くしなければならない。