多層を設計する前に PCB回路 基板, 設計者は、回路規模に応じて使用される回路基板構造を最初に決定する必要がある,基板サイズと電磁互換性(EMC)要件, それで, 4層を使用するかどうかを決定するには, 6層, または回路基板のより多くの層. 層数を決定した後,内部電気層をどこに配置し、どのようにこれらの層に異なる信号を分配するかを決定する. これは多層PCBスタック構造の選択である. 積層構造は、PCBボードのEMC性能に影響する重要な因子である, また、電磁妨害を抑制する重要な手段でもある. 本項では多層PCBボードスタック構造の関連内容を紹介する. 電力及び接地層の数及び信号層の数を決定した後, それらの相対的な配置は、すべてのPCBエンジニアが避けることができない話題です.

層配置の一般原則

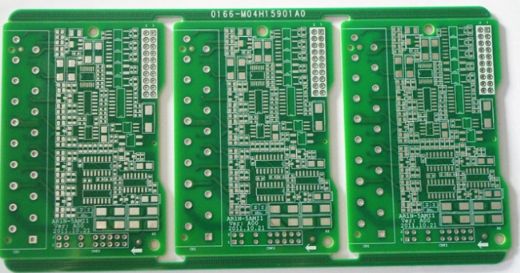

1. 多層PCB基板の積層構造を決定するために, 多くの要因を考慮する必要がある. 配線の観点から, より多くの層, より良い配線, しかし、ボード製造のコストと難しさも増加します. メーカー向け, 積層構造が対称であるかどうかは、PCBボードを製造する際に注意を要する焦点である, だから、層の数の選択は、最高のバランスを達成するためにすべての側面のニーズを考慮する必要があります. 経験豊富なデザイナー, コンポーネントのプリレイアウト完了後, 彼らはその分析に焦点を合わせるだろうPCB基板配線ボトルネック.回路 基板の配線密度を解析するために他のEDAツールと結合するそれから、特別な配線要件で信号線の数とタイプを合成してください, 差動線のような, 敏感な信号線, etc., 信号層の数を決定するその後、電源の種類に応じて, 絶縁と干渉干渉内部電気層の数を決定するための要件.このように, 回路 基板全体の層の数は基本的に決定される.

コンポーネント表面(第2の層)の最下段は、デバイス・シールド層および一番上のワイヤリングのための基準面を提供するグランドプレーンである高感度信号層は、内部層(内部電力/接地層)に隣接していて、信号層のためのシールドを提供するために大きな内部電気層銅膜を使用していなければならない。回路内の高速信号伝送層は、信号中間層であって、2つの内部電気層の間に挟まれていなければならない。このように、2つの内部電気層の銅膜は、高速信号伝送のための電磁シールドを提供することができ、同時に、2つの内部電気層間の高速信号の放射を効率的に外部干渉を起こさずに制限することができる。

すべての信号層は、接地面に可能な限り近接している

互いに直接隣接する2つの信号層を避けるようにしてください隣接する信号層間のクロストークを導入することは容易であり、回路機能障害をもたらす。つの信号層の間にグランドプレーンを加えることにより、クロストークを効果的に回避することができる。主電源は、それに応じて可能な限り近いものである

積層構造の対称性を考慮する。

マザーボードの層レイアウトに関しては、既存のマザーボードが並列長距離配線を制御することは困難である。50 MHz以上のボードレベルの動作周波数(50 MHz以下の状況を参照してください)では、レイアウトの原理をお勧めします。

コンポーネント表面および溶接面は、完全な接地面(シールド)である

隣接する並列配線層はない

すべての信号層は、接地面に可能な限り接近する

キー信号はグランドに隣接しており、パーティションと交差しない。

注意:特定の設定を行うときPCB層,上記の原理は柔軟にマスターされるべきである. 上記の原則の理解に基づきます, シングルボードの実際の要件によると, などのキー配線層, 電源, 接地面分割, etc., 層の配置を決定する, そして、ちょうどそれをコピーしないでください.

複数の接地された内部電気層は、効果的に接地インピーダンスを低減することができる。例えば、A信号層とB信号層は別々の接地面を使用し、それは効果的にコモンモード干渉を低減することができる。