電子システム設計の課題

システム設計の複雑さと集積化の大規模な増加に伴い,電子システム設計者は100 mhz以上の回路設計に従事し,バスの動作周波数は50 mhzに達し,あるいは100 mhzを越えた。現在、設計の50 %は50 MHz以上のクロック周波数を有し、設計のほぼ20 %は120 MHz以上のクロック周波数を有する。

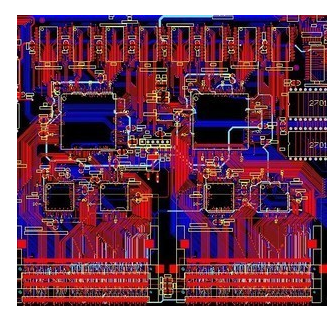

システムが50 MHzで働くとき, 伝送ラインの効果と信号の整合性の問題がありますシステムクロックが120 MHzに達すると, 高速回路設計知識を使用しない限り, 従来の方法に基づいて設計されたPCBは動作しません. したがって, 高速PCB 設計技術は電子システム設計者が採用しなければならない設計方法となった. 設計プロセスの制御性は高速回路設計者の設計手法を使用することによってのみ達成できる.

(2)高速回路とは

一般に、ディジタル論理回路の周波数が45 MHz〜50 MHzに達した場合、この周波数以上で動作する回路は、電子システム全体の一部(例えば1/3)を占有しており、高速回路と呼ばれている。

実際、信号エッジの高調波周波数は、信号自体の周波数より高い。信号伝送の予期しない結果を引き起こす信号(または信号ジャンプ)の立ち上がりエッジと立ち下がりエッジである。したがって、回線伝搬遅延がデジタル信号駆動端の立ち上がり時間の1/2よりも大きい場合には、高速信号と考えられ、伝送線路効果を生じることが一般的に認められる。

信号の伝送は、立ち上がりまたは立ち下がりのような信号状態が変化した瞬間に発生する。信号は駆動端から受信端まで一定時間経過する。送信時間が立ち上がりまたは立ち下がり時間の1/2未満であれば、受信端からの反射信号は信号が変化する前に駆動端に到達する。逆に、信号が状態を変化させた後、反射信号は駆動端に到達する。反射信号が強い場合、重畳波形は論理状態を変化させることができる。

高速信号の決定

以上で、伝送線路効果の発生条件を定義した, しかし、どのように我々はライン遅延が1/2ドライブ端の信号立ち上がり時間? 一般に, 信号の立ち上がり時間の典型的な値は、デバイス, そして、信号伝播時間は PCB設計. Correspondence between signal rise time and allowable wiring length (delay).

基板上の単位インチ当たりの遅延は0.167 nsである。しかし、多くのビア、多くのデバイスピン、および多くの制約がネットワークケーブルに設定されている場合、遅延は増加します。一般に、高速論理デバイスの信号立ち上がり時間は約0.2 nsである。基板上にgaasチップがある場合,最大配線長は7.62 mmである。

trは信号立ち上がり時間であり、TPDは信号線伝搬遅延である. TRが、4 TPDを引いてください, 信号が安全なエリアに落ちる. 2 TPDのアキノ奇形tr, 信号が不確定領域に落ちる. trが、2 TPD, 信号は問題領域に落ちる. 不確定領域と問題領域における信号の落下, high-speed PCB配線 methods should be used.