何か方法がありますか SMTパッチ いくつかの失敗問題を減らす?

SMTパッチは、PCBに基づいて処理される一連の技術プロセスの略称を指す。PCB(プリント回路基板)はプリント回路基板である。それで、いくつかの失敗問題を減らすためにSMTパッチのためのどんな方法もありますか?

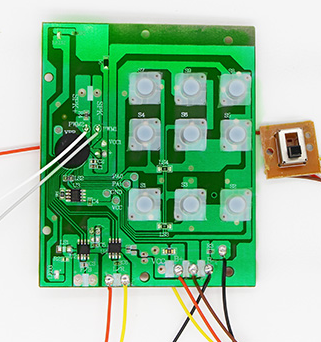

SMTパッチ

製法, 取扱い, and プリント回路アセンブリ(PCA)試験 すべてのパッケージは、機械的なストレスの多くにパッケージ, 失敗原因. グリッドアレイパッケージが大きくなるにつれて, これらのステップのセキュリティレベルを設定する方法はますます難しくなります.

長年にわたり,単調曲げ試験法はパッケージの代表的な特徴である。テストは、IPC / JEDEC - 9702「ボードレベル相互接続の単調な曲げ特性」で説明されます。この試験方法は,曲げ荷重下のプリント配線板の水平配線の破壊強度について述べた。

しかし, このテスト方法は最大許容張力を決定できません.

鉛フリーPCAの製造工程や組立工程においては、はんだ接合部の応力を直接測定することができない。相互接続されたコンポーネントのリスクを記述するために使用される最も広く使用されるメトリックは、コンポーネントに隣接するPCBプリント回路基板の張力であり、これはIPC/JEDEC−9704「プリント配線板歪み試験ガイドライン」に記載されている。

数年前、インテルはこの問題を実現し、実際に最悪の曲げ状況を再現するための異なるテスト戦略を開発し始めました。ヒューレットパッカードなどの他の企業はまた、他のテスト方法の利点を実現し、インテルに似た考えを検討し始めた。ますます多くのチップ製造業者および顧客は、製造、取扱いおよびテストの間の機械的故障を最小にするために使用される張力限界の決定が非常に価値があると理解するので、この方法はより多くの注意を引き起こした。インタレスト.

無鉛機器の使用が拡大するにつれて、ユーザはますます興味を持っている多くのユーザーが品質問題に直面しているので。

すべての関係者からの関心の増加に伴い、IPCは、他の企業がBGAが製造中とテスト中に破損しないことを保証する様々なテスト方法を開発するのを助ける必要があると感じています。本研究は、IPC 6 - 10 D SMTアタッチメント信頼性テストワーキンググループとJEDEC JC - 14.1パッケージ機器信頼性試験小委員会で共同作業を行い、完成した。

テスト方法は、円形配列に配置された8つの接点点を指定する。PCBプリント回路基板の中央に設置されたBGAを有するPCAはこのように配置されている。部品は支持ピン上にフェイスダウンされ、BGAの背面に負荷が印加される。IPC / JEDEC - 9704の推奨ゲージレイアウトに従って、部分に隣接する歪みゲージを配置します。

The PCA 関連する緊張レベルに曲げられるでしょう, そして、故障解析は、これらの張力レベルに対する偏向に起因する損傷の程度を決定することができる. 反復法は、損傷を引き起こさない張力のレベルを決定するために使用することができる. これがテンション限界.