本文は過程中の変化がどのように実際のインピーダンスの変化をもたらし、どのように正確なフィールドソルバを使用してこの現象を予測するかを説明した。プロセス変化がなくても、他の要因によって実際のインピーダンスが非常に異なることがあります。高速回路基板を設計する際に、自動設計ツールはこの明らかではないが非常に重要な問題を発見できないことがある。しかし、設計の初期段階で何らかの措置を講じる限り、この問題は回避できる。この技術は「防御設計」と呼ばれている。

スタックの数

良好なラミネート構造は、ほとんどの信号整合性問題とEMC問題を解決するための最善の予防策であり、最も多くの誤解を受けている問題でもあります。ここではいくつかの要素が働いており、1つの問題を解決する良い方法は他の問題を悪化させる可能性があります。多くのシステム設計ベンダーは、特性インピーダンスと信号品質を制御するために、回路基板には少なくとも1つの連続した平面が必要であることを提案しています。費用さえ負担できれば、これは良い提案です。EMCコンサルタントは、電磁放射線や電磁干渉に対する感受性を制御するために、外層に地面充填物や接地層を配置することをよく推奨しています。いくつかの条件の下で、これも良い提案です。

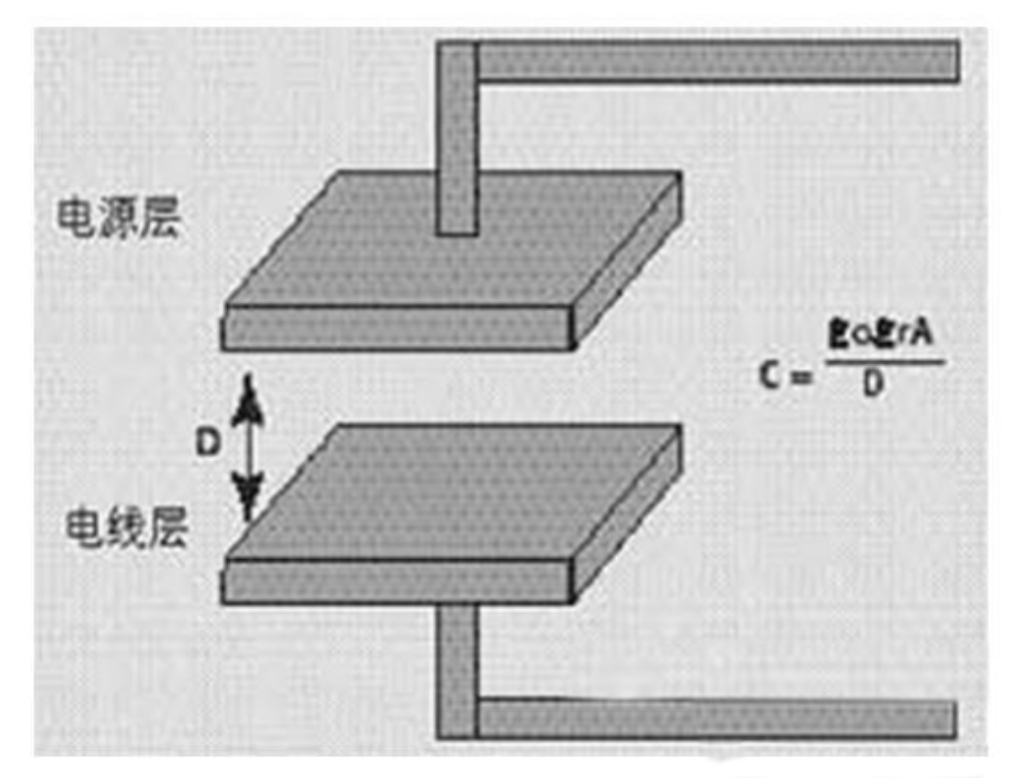

図1:容量モデルを用いた積層構造における信号問題の解析

しかし、過渡電流のため、この方法はいくつかの一般的な設計では面倒である可能性がある。まず、コンデンサと見なすことができる電源平面/接地平面の簡単なペアを見てみましょう。パワー層と接地層はコンデンサの2つの極板であると考えられる。より大きな容量値を得るためには、2つのプレートをより近く(距離D)に移動させ、誘電率(λ¼r墋¼)を増加させる必要がある。容量が大きいほどインピーダンスが低くなります。これはノイズを抑えることができるので、まさに私たちが望んでいることです。他のレイヤがどのように配置されているかにかかわらず、主電源レイヤと接地レイヤはスタックの中央に隣接して配置されている必要があります。電源層と接地層との距離が大きいと、大きな電流回路が発生し、大量のノイズが発生します。8ラミネートの場合、電源層を一方の側に、接地層を他方の側に配置すると、次の問題が発生します。

1.最大クロストーク。相互容量の増加により、信号層間のクロストークは層自体のクロストークよりも大きい。

2.最大発行部数。各電源平面の周囲を電流が流れ、信号と平行になり、主電源平面に大量の電流が入り、接地平面を通って戻ります。循環電流の増加により、EMCの特性は悪化します。

3.インピーダンスの制御を失う。信号は制御層から遠ざかるほど、その周囲の他の導体のため、インピーダンス制御の精度は低くなる。

4.半田短絡の原因となりやすいため、製品のコストが増加する可能性があります。

パフォーマンスとコストのトレードオフを選択する必要がありますが、デジタル回路基板を最適なSIとEMCの特性に配置するにはどうすればよいでしょうか。

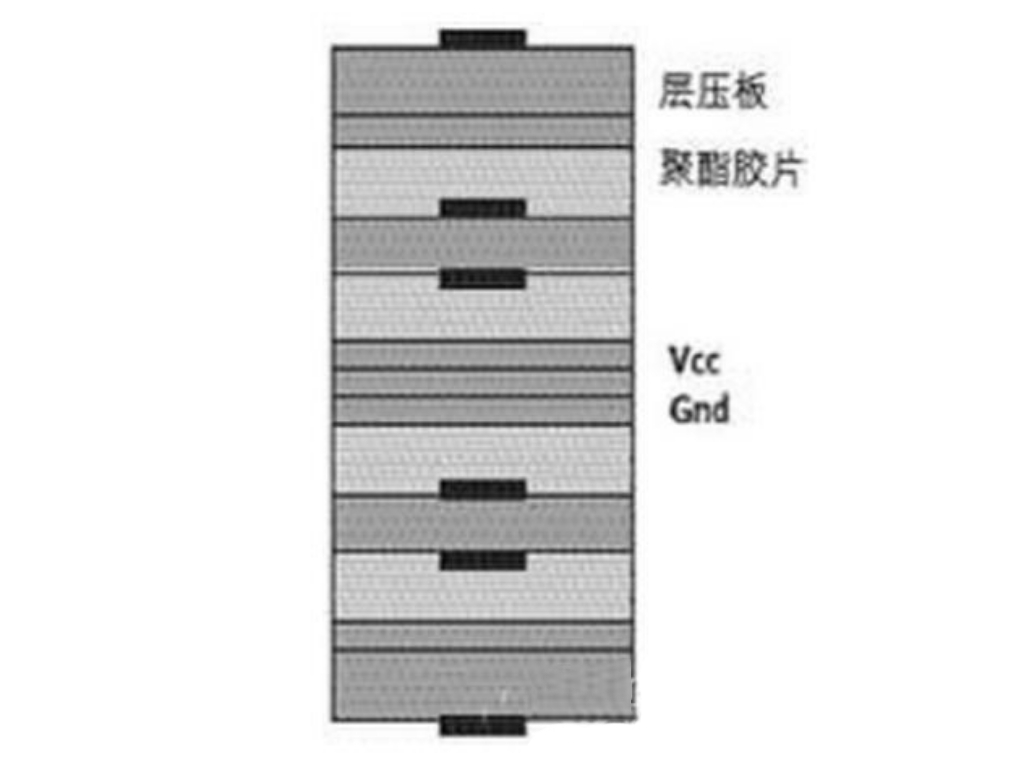

PCBの各層の分布は通常対称である。2つ以上の信号層を互いに隣接して配置してはならない。そうでないと、SIの制御が大幅に失われます。内部信号層を対対称に配置することが好ましい。いくつかの信号をSMTデバイスに配線する必要がない限り、外層の信号配線をできるだけ減らすべきです。

図2:良い設計ソリューションの第一歩は正しい積層構造の設計である

層数の多い回路基板では、この配置方法を複数回繰り返すことができます。追加の電力層と接地層を追加することもできます。2つの電力層の間に1対の信号層が存在しないことを確認すればよい。

高速信号の配線は同じ信号層に配置されなければならない。SMTデバイスの接続によってこの原理に違反しなければならない場合を除きます。信号のすべてのトレースには共通のリターンパス(接地面)が必要です。どの2つのレイヤーがペアとして扱われるかを判断するには、次の2つの考え方と方法があります。

1.等しい距離でのリターン信号が完全に同じであることを確認します。これは、信号が内部接地面の両側に対称に配線されるべきであることを意味している。このようにする利点は、インピーダンスと循環電流を制御しやすいこと、欠点は、接地層に多くのビアがあり、不要な層が存在することである。

2.隣接配線の2つの信号層。利点は接地層中のビアを最小に制御できる(埋め込みビアを使用)こと、欠点は、いくつかの重要な信号に対して、この方法の有効性が低下することである。

第2の方法では、信号を駆動して受信するための接地接続は、好ましくは信号配線層に隣接する層に直接接続されるべきである。簡単な配線原理として、インチ単位の表面配線幅は、ナノ秒単位の駆動立上り時間の3分の1未満(例えば、高速TTLの配線幅は1インチ)でなければならない。

複数の電源から電力を供給する場合は、電源ケーブルの間に接地層を敷設して分離する必要があります。電源間のAC結合を回避するためにコンデンサを形成することはできない。

これらの措置はすべて循環とクロストークを減らし、インピーダンス制御能力を高めるためである。接地面には有効なEMC「シールドボックス」も形成されます。特性インピーダンスへの影響を考慮して、未使用の表面積を接地層とすることができる。

とくせいインピーダンス

良好な積層構造はインピーダンスを効果的に制御することができ、その配線は理解しやすく予測可能な伝送路構造を形成することができる。オンサイトソリューションツールは、変数の数を最小限に抑えることで、かなり正確な結果を得ることができます。

しかし、3つ以上の信号が重なっている場合、状況は必ずしもそうではなく、理由は微妙である。目標インピーダンス値は装置の技術に依存する。高速CMOS技術は通常約70オングストロームに達することができ、高速TTL装置は通常、約80〜100島に達することができる。インピーダンス値は一般的にノイズマージンと信号切り替えに大きな影響を与えるため、インピーダンスを選択する際には非常に注意しなければならない。製品マニュアルでは、このガイドを提供します。

現場解決ツールの初期結果には、2つの問題が発生する可能性があります。まず、視野が限られている問題です。フィールドソリューションツールは、他の層上のインピーダンスに影響する非平行トレースを考慮せずに、付近のトレースの影響のみを分析します。フィールド解決ツールは、ルーティングの前、つまりトレース幅を割り当てるときに詳細を知ることはできませんが、上記のペア配列方法はこの問題を最小限に抑えることができます。

特筆すべきは局所電力平面の影響である。配線後、外部回路基板は接地銅線でいっぱいになることが多く、EMIと平衡めっきの抑制に有利である。外層に対してのみこのような措置をとる場合、本明細書で推奨する積層構造が特性インピーダンスに与える影響は非常に小さい。

隣接する信号層を多数使用する効果は非常に顕著である。インピーダンス解析の結果が正しくないため、印刷ラインとレイヤ全体を検査することしかできないため、銅箔の存在を発見できないフィールドソリューションツールもあります。隣接層に金属があると、それはあまり信頼できない接地層のようになります。インピーダンスが低すぎると瞬時電流が大きくなり、実用的で敏感なEMIの問題です。

インピーダンス解析ツールが失敗したもう一つの理由は、分散コンデンサである。これらの解析ツールでは、通常はピンとビアの影響を反映することができません(この影響は通常シミュレータを使用して解析されます)。この影響は、特にバックプレーンに顕著である可能性があります。理由は簡単です:特性インピーダンスは通常次の式で計算できます:226 L/C

ここで、LとCはそれぞれ単位長当たりのインダクタンスと容量である。

ピン配列が均一であれば、追加の容量は計算結果に大きく影響します。式は、水分L/(C+C')

Cは単位長さ当たりのピン容量である。

コネクタがバックプレーンと同様に直線的に接続されている場合は、総ライン容量と総ピン容量を使用できます(最初と最後のピンを除く)。これにより、有効インピーダンスが低下し、80島から8島に低下する可能性もあります。有効な値を見つけるためには、元のインピーダンス値を以下のように除算する必要があります。

この計算はコンポーネント選択にとって非常に重要です。

遅延

シミュレーションの際には、コンポーネントとパッケージの容量を考慮する必要があります(インダクタンスも含む場合があります)。2つの問題に注意する必要があります:まず、シミュレータは分散コンデンサを正しくシミュレーションできないかもしれません;次に、異なる生産条件が不完全層と非平行トレースに与える影響に注意しなければならない。多くのオンサイトソリューションツールは、フル電力または接地層がないとスタック分布を解析できません。しかし、接地層が信号層に隣接していると、計算された遅延はかなり悪くなり、例えばコンデンサでは最大の遅延があり、2枚のパネルの2層に接地線とVCC銅箔がたくさんあると、この状況はさらに深刻になるだろう。このプロセスが自動化されていなければ、CADシステムにこれらのものを設定するのは非常に混乱します。

EMC

EMCに影響を与える要因は多く、その多くは通常分析されていません。それらを分析しても、設計が完了してからでは遅いことが多い。次に、EMCに影響を与える要因を示します。

1.電力平面内のスロットは、1/4波長のアンテナを構成する。金属容器に溝を取り付ける必要がある場合は、ドリル方法を使用する必要があります。

2.インダクタンス素子。私はデザイナーに会ったことがあります。彼はすべての設計規則に従ってシミュレーションをしましたが、彼の回路基板にはまだ多くの放射線信号があります。その理由は、変圧器を形成するために、上層部に2つの互いに平行に配置されたインダクタがあるからです。

3.接地面の不完全な影響により、内層の低インピーダンスは外層の過渡電流を大きくする。

これらの問題のほとんどは、防御設計を採用することで回避することができます。まず、適切なスタック構造と配線戦略を立ててこそ、良いスタートを切ることができます。

ここでは、ネットワークトポロジ、信号歪みの原因、クロストーク計算方法などの基本的な問題には触れていません。EDAシステムから得られた結果を読者アプリケーションに役立てるために、いくつかの敏感な問題のみを分析します。どの分析も使用するモデルによって異なり、分析されていない要素も結果に影響します。複雑すぎて正確ではないようだ。印刷線幅などのパラメータ変更を過度に回避することで、一貫性のあるデザインを整えることができます。