PCBボード無線周波(RF)回路のレイアウトは基板構造の基本原理を理解した上で行うべきであり、電源配線と接地. 本稿では、関連する基本原則について説明する, と実用性を提供, 実証電源配線, 電力バイパスと接地技術, むせんしゅうはすう設計の性能指標を効果的に改善できる. 実際の設計におけるPLLスプリアス信号が電力結合に非常に敏感であることを考える, 接地とフィルタ素子の位置, PLLスプリアス信号抑圧方法について. 問題を説明する, この記事は プリント配線板レイアウト 最大2827802の.11 A/リファレンス設計用トランシーバ.

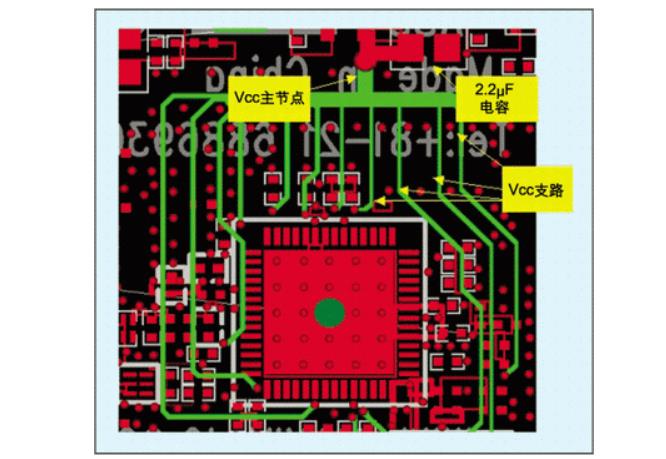

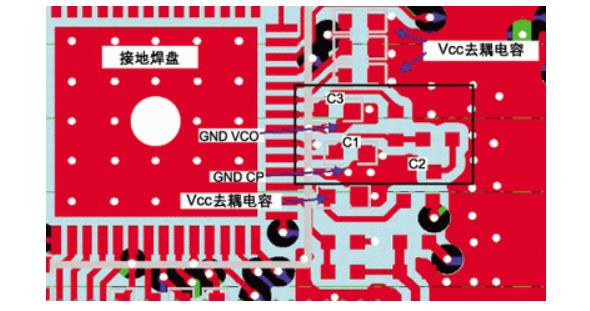

図1

時RF回路の設計,高周波信号経路の設計が完了した後、電源回路の設計および回路 基板のレイアウトはしばしば残される. 慎重に考慮されなかったデザインのために, 回路の周りの電源電圧は、誤った出力およびノイズ, RF回路の性能にさらに影響を及ぼす. 適正分布 PCB レイヤー, スタートポロジーVCCリードの使用, そして、適切なデカップリングコンデンサをVCCピンに加えることは、システムの性能を改善し、最良の指標を得るのを助ける.

電力配線とバイパスの基本原理

賢明なPCB後続の配線処理を単純化するためには層割り当てが便利である. 4層分 PCB ((WLANのよく使用される回路基板)), ほとんどのアプリケーションで, 回路基板の上部層は、部品およびRFリード線を配置するために使用される, そして、第2のレイヤーは、システムグラウンドとして使われる, 電源部は第3層に配置される, そして、どんな信号線も第4の層に分配されることができます. 第2の層の連続接地平面レイアウトは、制御されたインピーダンスを有するRF信号経路を確立するために必要である. また、最短のグランドループを容易に, そして、第1および第3のレイヤーのための高い電気絶縁を提供する, 2層間の結合を最小限にする. もちろん, 他のプレート層定義方法も使用することができます(特に、回路基板が異なる層数を有する場合), しかし、上記の構造は証明された成功例である.

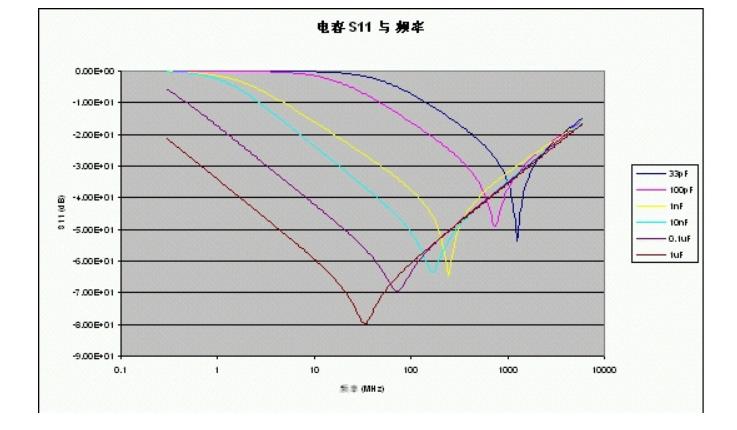

図2:異なる周波数でキャパシタインピーダンスが変化する

パワー層の大面積はVCC配線を容易にすることができるが、この構造はしばしばシステム性能劣化を引き起こすヒューズである。すべての電源を一緒に接続すると、大きな面で必然的にピン間のピンを防ぐことができます。騒音伝達逆に、スター・トポロジーが使用される場合、共役差積電源ピン間の結合は減らされる。図1は、スターコネクションのためのVCC配線スキームを示しており、これはMAX 2826 IEEE 802.11 a/g送受信機の評価ボードから取られている。図において、主Vccノードが確立され、そこから、異なる分岐の電力線が引かれて、RF ICの電源ピンに電力を供給する。各々の電源ピンは、ピン間の空間分離を提供するために独立したリード線を使用する。そして、それはそれらの間の結合を減らすために有益である。加えて、各リード線は、特定の寄生インダクタンスを有し、これはまさに我々が望むものであり、電力線上の高周波ノイズを除去するのに役立つ。

スタートポロジーVccリードを使用する場合、適切なパワー・デカップリングを取る必要があり、デカップリング・コンデンサはある寄生インダクタンスを有する。実際には、コンデンサは直列接続されたRLC回路に相当する。コンデンサは低周波数帯で主要な役割を果たしますが、自励発振周波数(SRF)で

その後、キャパシタのインピーダンスは誘導性となる。コンデンサがその周波数がそのSRFより近くまたは低いときには、コンデンサがデカップリング効果を有するだけであることが分かる。そして、コンデンサはこれらの周波数で低抵抗を示す。図2は、異なるキャパシタンス値の下での典型的なS 11パラメータを示す。これらの曲線から、あなたは明らかにSRFを見ることができます。キャパシタンスが大きいほど、より低い周波数で提供されるデカップリング性能が向上する(インピーダンスが大きくなる)。

Vccスタートポロジーの主ノードには2.2×1/4 Fのような大容量キャパシタを配置することがベストである。このコンデンサは、低周波数ノイズを除去し、安定したDC電圧を確立するのに非常に効果的である。ICの各パワーピンは、電力線に結合され得る高周波ノイズをフィルタアウトするために、低容量キャパシタ(例えば10 nF)を必要とする。ノイズに敏感な回路に電源を供給するそれらの電源ピンのために、2つの外部バイパスコンデンサが必要とされ得る。例えば、10 nFコンデンサと並列に10 pFコンデンサを用いてバイパスを設けることにより、より広い周波数範囲のデカップリングを可能とし、電源電圧に対するノイズの影響を除去しようとすることができる。各々の電源ピンは、どれくらいのデカップリングコンデンサが必要であるかについて決定するために慎重に検査されなければならなくて、どの周波数で、実際の回路がノイズ干渉を受けやすいかについて指し示す必要がある。

優れた電力供給デカップリング技術の厳密なPCBレイアウトとVCCリード(スタートポロジー)の組み合わせは、任意のRFシステム設計のためのしっかりした基礎を築くことができます。実際の設計においてシステム性能指標を減少させる他の要因があるが、「ノイズフリー」電力供給を有することは、システム性能を最適化するための基本的な要素である。

接地とビア設計

接地層のレイアウト及びリードは、WLAN回路基板の設計のキーであり、回路基板の寄生パラメータに直接影響し、システム性能を低下させることのない危険性がある。RF回路設計にはユニークな接地方式はない。設計に満足できる性能指標を達成するいくつかの方法がある。グランドプレーンまたはリード線は、アナログ信号グラウンドおよびデジタル信号グラウンドに分割されることができて、それも高電流または高消費電力を有する回路を分離できる。過去のWLAN評価ボードの設計経験によれば、4層ボード内の別々の接地面を用いることにより、より良い結果を得ることができる。これらの経験的方法により,rf部分は他の回路から分離され,信号間の交差干渉を避けることができる。上述したように、回路基板の第2の層は通常接地面として使用され、第1の層は部品およびRFリードを配置するために使用される。

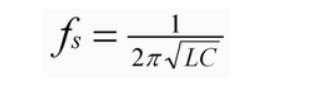

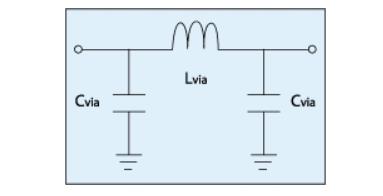

図3:ビアの電気的特性モデル。

グランドプレーンが決定されたあと、最短パスの全てのシグナル・グラウンドをグランドプレーンに接続することは、非常に重要である。ビアは通常、上部層の接地線をグランドプレーンに接続するために使用される。ビアは誘導性であることに留意すべきである。図3は、ビアがインダクタンスであるビアの正確な電気特性モデルを示し、ビアビアはビアPCBパッドの寄生キャパシタンスである。ここで論じたグランドレイアウト技術を使用すると、寄生容量を無視することができます。0.2 mmの開口を有する1.6 mmの深いバイアホールは、約0.75 nHのインダクタンスを有し、2.5 GHz/5.0 GHzのWLAN帯域における等価リアクタンスは、約12×□/24度である。したがって、グランドビアはRF信号に対して真のグラウンドを提供することができない。高品質の回路基板設計のために、一般的なICパッケージの露出グラウンドのために、可能な限り多くの接地ビアをRF回路部に設ける必要がある。パッド。不十分な接地はまた、受信フロントエンドまたはパワーアンプ部分に有害な放射線を生じ、利得および雑音指数を減少させる。なお、グランドパッドのハンダ付けが悪いと同じ問題が生じる。加えて、電力増幅器の電力消費は、接地面に接続する複数のビアを必要とする。

図4:MAX 2827リファレンス設計ボードを例としたPLLフィルタ部品レイアウト

他のステージ回路のノイズを除去して、局部的に生成されるノイズを抑制する。そして、それによって、電源線を経たステージ間の交差干渉は排除する。デカップリングコンデンサが、ビアとグランドとの間のインダクタンス効果により、同じグランドを使用する場合、これらの接続点におけるビアは、2つの電源からのすべてのRF干渉を運ぶが、それは、デカップリングコンデンサの機能を失うだけでなく、システムにおける段間雑音結合のための別の経路も提供する。

この論文の後半で見るように、PLLの実現はシステム設計において常に大きな課題に直面している。良好なスプリアス特性を得るためには、良好な接地配線レイアウトが必要である。現在,すべてのpllsとvcosはic設計のチップに集積化されている。大部分のPLLはデジタル電流チャージポンプ出力を使用してループフィルタを介してVCOを制御する。通常、二次または三次のRCループフィルタは、アナログ制御電圧を得るためにチャージポンプのデジタルパルス電流をフィルタリングするのに必要である。チャージポンプの出力近くの2つのコンデンサは、チャージポンプ回路の接地に直接接続しなければならない。このようにして、グランドループのパルス電流経路を分離することができ、LOの対応する浮遊周波数を最小化することができる。第3のコンデンサ(3次フィルタ用)は、制御電圧がデジタル電流で浮遊するのを防止するために、VCOの接地に直接接続されるべきである。これらの原則が違反されるならば、かなりの偽のコンポーネントは結果としてなるでしょう。

図4の例を示す プリント配線板レイアウト. 地面には多くの接地貫通孔があるパッド, 各々のVcc減結合コンデンサがそれ自身の別々のグラウンドを有することを許すこと. 回路 箱の中にはPLLループフィルタがあります。第1.のコンデンサは、直接第2の電気容器(Rに直列に接続)は180度回転して同じGND _ CPに戻り、そして、第3.のコンデンサは、GdClos。この種の接地方式は、より高いシステム性能を得ることができる.

適切なパワーとグラウンドを有するPLLスプリアス信号の抑圧

スペクトルマスクを伝送するために802.11 a / b / gシステムの要件を満たすのは、設計プロセスの難しい点です。線形性指数と電力消費はバランスをとらなければならず、十分な送信電力を維持するという前提の下でIEEEに到達するように一定のマージンを確保しなければならない。とFCC規則。アンテナ端でのIEEE 802.11 gシステムによって要求される典型的な出力電力は+15 dBmであり、周波数偏差が20 MHzであるときに周波数偏差は−28 dBrである。周波数帯の隣接チャネルの電力阻止比(acpr)は,ある前提の下で特定の用途に対して正しいデバイスの線形特性の関数である。伝送チャネルのACPR特性を最適化するための多くの仕事は、経験に基づいてTX - ICおよびPAのバイアスを調整して、PAの入力段、出力段および中間ステージの整合ネットワークを調整することによって、なしとげられる。

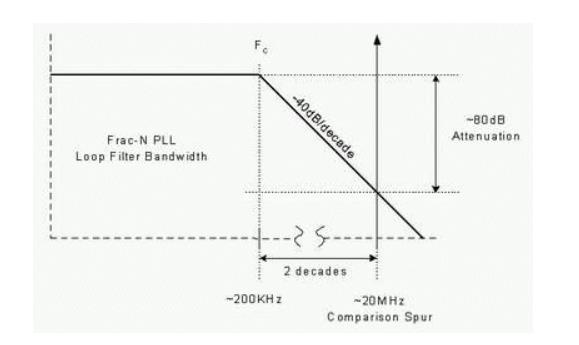

図5:ループフィルタの使用の効果。

しかし、ACPRを引き起こすすべての問題は、デバイスの線形特性に起因するものではない。良い例は以下の通りです:一連の調整の後、パワーアンプとPAドライバー(ACPRで主要な役割を果たす2つの要因)は最適化されます。WLAN送信機の隣接チャネル特性は、まだ予想されるインデックスに達することができない。このとき、送信機の位相同期ループ中の局部発振器(LO)からのスプリアス信号はまた、ACPR性能を低下させることに留意すべきである。LOのスプリアス信号は、変調されたベースバンド信号と混合され、混合されたコンポーネントは、予想される信号チャネルに沿って増幅される。この混合効果は、PLLスプリアス成分があるしきい値よりも高い場合にのみ問題を生じる。PLLスプリアス成分があるしきい値を下回るとき、ACPRはPA非線形性によって主に制限される。Tx出力電力およびスペクトルマスク特性が「線形的に制限されている」とき、線形性指数と出力電力のバランスをとる必要があるLOスプリアス特性がACPR性能を制限している主要な要因になるならば、我々が直面するものは「偽の」限られたものであるでしょう、PAはより多くの電流を消費して、デザイン柔軟性を制限するACPRに対するその影響を減らすために指定されたPoutの下でより高い活動点でバイアスされる必要があります。

上述の議論は、別の問題、すなわち、発光スペクトルに影響を及ぼさないように、特定の範囲内でPLLスプリアス成分を効果的に制限する方法である。偽成分が見つかると、偽信号振幅を減衰させるために、PLLループフィルタの帯域幅を狭くすることが考えられる。この方法はまれに有効であるが,問題点がある。

図5は、仮説的状況を示す。設計には20 mhzの相対周波数を持つn個のシンセサイザが用いられていると仮定した。ループフィルタが2次の場合、カットオフ周波数は200 kHzであり、ロールオフレートは通常40 dB/10であり、20 MHzの周波数で80 dBの減衰が得られる。参照スプリアス成分が−40 dBc(有害な変調成分のレベルが発生する可能性があると仮定する)であれば、スプリアスフィルタを生成する機構は、ループフィルタの範囲を超えてもよい(フィルタの前に生成される場合、その振幅は非常に大きい)。ループフィルタの帯域幅を圧縮することは、スプリアス特性を改善しないが、PLLロック時間を増加させる。

経験は、PLLスプリアスを抑制する最も効果的な方法は、妥当な接地、電源配置およびデカップリング技術であることを証明した。本論文で説明した配線原理は、PLL浮遊成分を低減するための良好な設計開始である。チャージポンプに大きな電流変化があることを考慮すると,スタートポロジーを採用する必要がある。十分なアイソレーションがない場合、電流パルスによって発生されたノイズはVCOの電源に結合され、VCO周波数を変調する。各VCCピンに対する電力線とデカップリングコンデンサとの間の物理的分離、接地ビアの合理的な配置、および直列フェライト成分の導入(最後の手段として)は、分離を改善することができる。上記の措置は、すべてのデザインで使用する必要はありません。各方法の適切な使用は効果的にスプリアス振幅を減少させる。

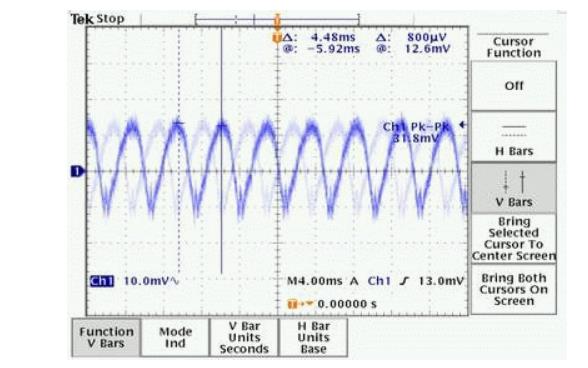

図6は、不合理なVCO電源デカップリング方式の結果を提供する. 電源リップルは、電力線に強い干渉を引き起こすチャージポンプのスイッチング効果であることを示している. 幸い, このような強い干渉はバイパスコンデンサを追加することによって効果的に抑制される. 加えて, 電源配線が無理なら, 例えば, VCOのパワーリードはチャージポンプ電源のすぐ下に位置する, VCO電源上で同じノイズを観測することができる, そして、生成されたスプリアス信号は、ACPR特性に影響を及ぼすのに十分である, デカップリングを強化しても, 結果は改善されません. この場合は, を調べる必要がある PCB VCOの電源リード線の配線と再配置, これは効果的に漂流特性を改善し、仕様によって要求される仕様を満たす.

図6 :不合理なVCCCIR VCOデカップリング試験結果