Teknik untuk memotong unit individu dari wafer dan kemudian mengepaknya telah lama menjadi norm untuk mengepakkan sirkuit setengah konduktor terintegrasi selama dekade. Namun, pendekatan ini tidak sedang diadopsi oleh pembuat setengah konduktor utama disebabkan biaya penghasilan yang tinggi dan komponen RF yang meningkat bagi modul hari ini. Oleh itu, muncul pakej aras wafer (WLP) telah menyebabkan perubahan paradigm a dalam pembangunan pakej dengan biaya rendah. WLP adalah teknologi pakej aras wafer sebelum memotong peranti pakej wafer.

Mengguna alat dan proses piawai, WLP bertindak sebagai sambungan proses penghasilan wafer. Akhirnya, WLP DIE yang dibuat akan mempunyai pad metalisasi di permukaan cip dan titik askar yang ditempatkan pad a setiap pad sebelum memotong wafer. Ini menjadikan WLP serasi dengan proses pengumpulan PCB tradisional dan membolehkan ujian peranti pada wafer sendiri. Sebagai hasilnya, ia adalah proses yang relatif rendah dan efisien, terutama semasa saiz wafer meningkat dan cip DIE berkurang. Saiz wafer telah meningkat selama beberapa dekade terakhir, dari 4, 6, dan 8 inci dalam diameter kepada 12 inci. Ini mengakibatkan peningkatan bilangan DIE per wafer, yang menurunkan biaya penghasilan. Dalam terma prestasi elektrik, WLP lebih baik daripada teknologi pakej lain, dalam makna bahawa apabila peranti WLP terpasang ke dalam modul RF yang padat, ia menghasilkan pengurangan yang signifikan dalam sambungan parasit EM kerana sambungan antara peranti dan PCB adalah relatif pendek, tidak seperti sambungan kabel-ikatan yang digunakan dalam beberapa jenis teknologi CSP.

Teknologi chip flip-chip WLP

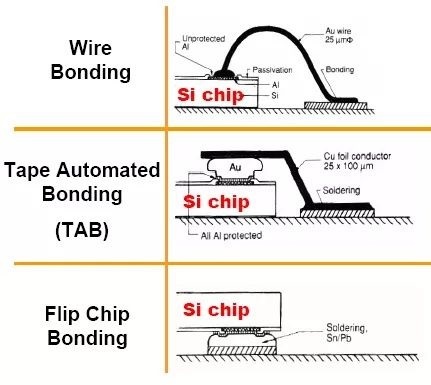

Teknologi Flip-chip, juga dikenali sebagai Sambungan Chip Collapse Controlled (C4), adalah salah satu daripada beberapa teknologi pemasangan cip yang dikembangkan oleh IBM pada tahun 1960-an. Walaupun teknologi pakej berdasarkan ikatan wayar lebih fleksibel dalam terma kemampuan induktif percuma untuk penyahpepijatan makmal selepas perkakasan dibina, dan juga menyediakan konduktiviti panas yang baik, penggunaan bulge solder dalam teknologi pakej flip-chip membuat sambungan elektrik antara substrat pakej dan cip menyediakan pengurangan saiz relatif, kecurangan kelemahan, - dan pengasingan yang lebih baik dalam terma input dan output pins. Figur 1 menggambarkan struktur asas cip DIE pada substrat, dengan bola tentera di atas lajur Cu tumbuh di permukaan cip. Perhubungan tentera biasanya dikumpulkan dengan komponen bentuk penuh untuk menyediakan sokongan mekanik untuk kumpulan tentera.

Pakej aras cip WLP

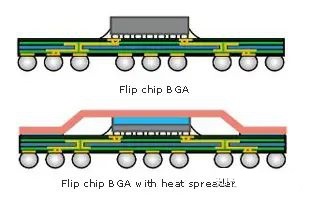

Pengimbangan skala Chip (CSP) adalah salah satu kaedah pengimbangan yang paling biasa digunakan dalam industri mikroelektronik dan setengah konduktor. Sementara beberapa jenis teknologi CSP sudah tersedia untuk penghasil cip mikro, jenis baru terus muncul untuk memenuhi permintaan untuk produk yang menyokong ciri-ciri baru dan produk khusus aplikasi baru. Keperluan pakej ini boleh berbeza bergantung pada aras kepercayaan yang diperlukan, kos, ciri tambahan, dan saiz keseluruhan. @ info Sebagaimana nama menunjukkan, saiz pakej CSP adalah kira-kira sama dengan saiz DIE cip, yang merupakan salah satu keuntungan utamanya. Dengan mengadopsi proses penghasilan WLP, CSP sentiasa dikembangkan untuk mencapai nisbah saiz pakej-mati yang paling kecil yang mungkin. Seperti yang dipaparkan dalam Gambar 2, gaya tata grid bola (BGA) CSP dalam pakej membolehkan beberapa sambungan sambungan sementara mempermudahkan kawat PCB, meningkatkan kelajuan pengumpulan PCB dan mengurangkan biaya penghasilan.

Teknologi encapsulasi lain

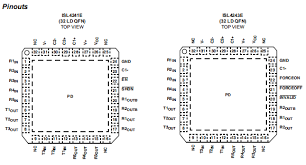

Terdapat beberapa bentuk lain pakej IC terintegrasi yang membenarkan integrasi tanpa senyap ke dalam pakej modul tersendiri-aplikasi. Pakej Flat Quad (QFP) merupakan salah satu teknologi pakej IC lapisan-permukaan terlebih awal, di mana struktur pakej terdiri dari empat sisi dengan petunjuk sambungan lanjutan, seperti yang dipaparkan dalam Figur 3(a). Pemimpin yang ditangkap disambung ke bingkai pakej untuk membentuk kondensator jenis logam-insulator-metal (MIM) antara pemimpin dan logam chip DIE, yang boleh digunakan sebagai unsur yang sepadan. Teknik ini sesuai untuk ICs saiz milimeter di mana bilangan pin periferik dalam pakej boleh mencapai lebih dari 100 pin. Terdapat beberapa derivat dari jenis ini encapsulasi, bergantung pada bahan yang digunakan, seperti pakej rata kuad keramik, pakej rata kuad tipis, pakej rata kuad plastik, pakej rata kuad plastik) dan pakej rata kuad metalik (MQFP). QFN, Quad Flat No Lead, dipaparkan dalam Fig. 3(b) adalah salah satu daripada beberapa teknologi pakej yang diletak permukaan terbentuk dari bingkai lead tembaga rata dan pakej plastik yang digunakan sebagai pad pemindahan panas untuk radiator. Pengikatan wayar juga boleh digunakan untuk sambungan, dan kerana garis ikatan bukan sahaja konduktor tetapi juga induktor, mereka biasanya mempengaruhi prestasi peranti di bawah teknik encapsulasi ini, kecuali ia dianggap sebagai sebahagian daripada rancangan keseluruhan. Walaupun QFN adalah satu sambungan yang terdiri dari empat sisi, petunjuk dua-pesawat yang tidak terbuka (DFN) juga muncul dan membentuk kedua-dua sisi petunjuk pesawat antara sambungan.