Definisi dan Fungsi Substrate IC

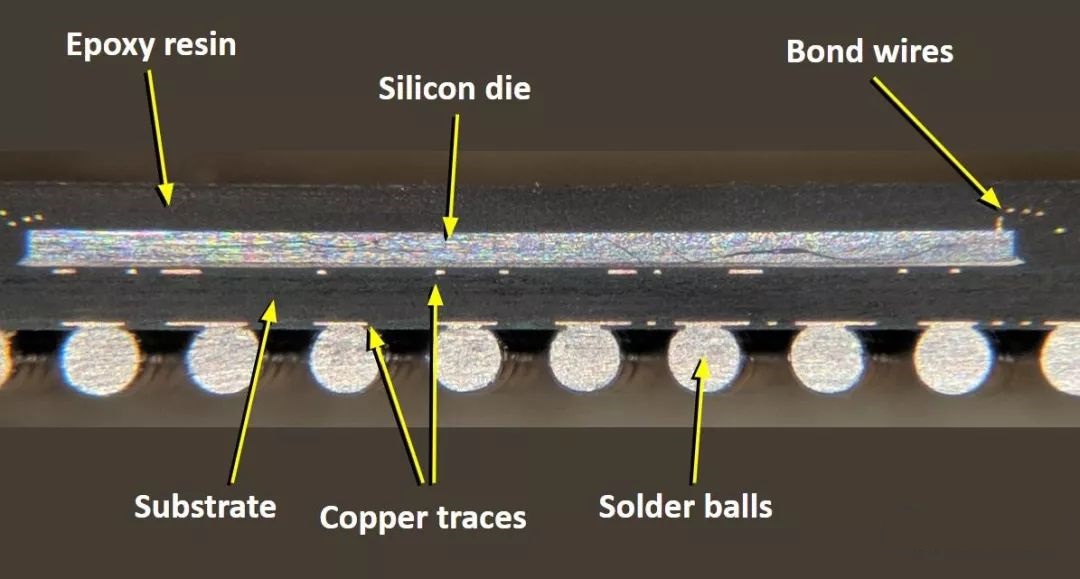

Definisi Substrate IC: Papan asas digunakan untuk mengincapsul cip IC kosong.

Fungsi Substrate IC

(1) Membawa cip IC setengah konduktor.

(2) Sirkuit dalaman diatur untuk sambungan antara cip dan papan sirkuit.

(3) Lindungi, baiki, sokongan cip IC, menyediakan saluran penyebaran panas, adalah produk sementara cip komunikasi dan PCB.

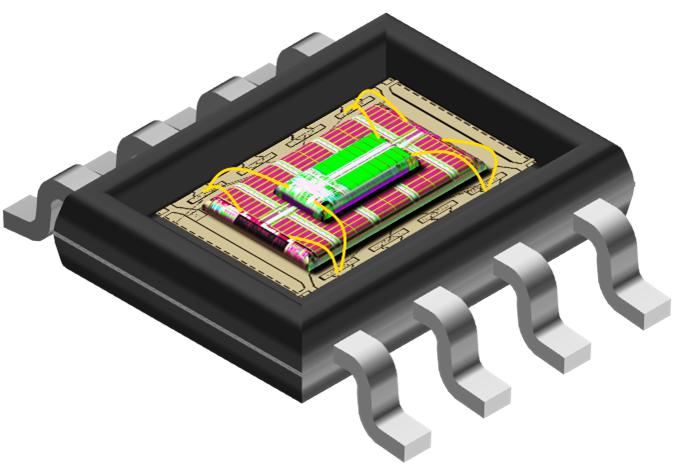

Pakej IC

IC Substrate dilahirkan: di tengah-1990-an, kurang dari 20 tahun. Kehadiran bentuk pakej densiti tinggi sirkuit terintegrasi (IC) baru, seperti BGA (pakej tata grid bola) dan CSP (pakej saiz cip), telah mengakibatkan pembawa baru yang diperlukan untuk pakej -- substrat pakej IC.

* Pembangunan Semiconductor: valve - Transistor - Through hole assembly - surface Packaging (SMT) - Chip level Packaging (CSP, BGA) - System Packaging (SIP)

* PCB dan teknologi setengah konduktor adalah interdependent, dekat, penetrasi, koordinasi dekat, PCB boleh mencapai pelbagai cip, komponen antara izolasi elektrik dan sambungan elektrik, untuk menyediakan ciri-ciri elektrik yang diperlukan.

Parameter teknikal Bilangan lapisan, 2 ~ 10 lapisan;

Lebar papan PCB, biasanya 0.1 ~ 1.5mm;

Toleransi tebal papan PCB minimum *0 mikron;

Buka minimum, melalui lubang 0.1 mm, lubang mikro 0.03mm;

* Lebar/jarak corak minimum, 10~80 mikron;

Lebar cincin minimum, 50 mikron;

* Toleransi contur, 0~50 mikron;

* Buried blind hole, impedance, buried resistance capacity;

* Surface coating, Ni/Au, soft gold, hard gold, Nickel/palladium/gold, etc.

* Saiz papan, 150*50mm (pembawa IC tunggal);

Ia bermakna, Substrate IC memerlukan lebih baik, densiti tinggi, bilangan kaki tinggi, volum kecil, lubang, cakera, garis lebih kecil, lapisan inti ultra-tipis. Oleh itu, perlu mempunyai teknologi penyesuaian antar lapisan yang tepat, teknologi gambar corak, teknologi elektroplating, teknologi pengeboran dan teknologi pengubahan permukaan. Keperluan yang lebih tinggi telah ditetapkan untuk kepercayaan produk, peralatan dan alat, bahan dan pengurusan produksi. Oleh itu, ambang teknikal Substrate IC tinggi dan penyelidikan dan pembangunan tidak mudah.

Kesulitan teknikal dibandingkan dengan penghasilan PCB tradisional, kesulitan teknikal yang perlu dikalahkan untuk Substrate IC adalah seperti ini:

(1) papan utama teknologi papan utama kurus, mudah untuk deformasi, terutama apabila tebal plat â¤0.2mm, dengan struktur plat, pengembangan plat dan kecerunan, parameter laminar, sistem kedudukan antar lapisan dan teknologi lain perlu membuat penerbangan, untuk mencapai peledak utama ultra-kurus merangkak dan menekan tebal kawalan yang berkesan.

(2) Teknologi mikroporos

* Termasuk: proses terbuka topeng solder, proses pengeboran laser lubang buta mikro, proses penuhian penutup tembaga lubang buta.

* Proses Conformalmask (Conformalmask) digunakan untuk membuat kompensasi yang masuk akal untuk pembukaan tetingkap lubang buta laser, dan langsung takrifkan terbuka dan kedudukan lubang buta melalui cincin tembaga terbuka.

* Indikator yang terlibat dalam lubang mikro pengeboran laser: bentuk lubang, nisbah terbuka atas dan bawah, erosi sisi, penyebaran serat kaca, lem sisa di bawah lubang, dll.

* Indikator yang terlibat dalam penutup tembaga lubang buta termasuk: kapasitas penutup, lubang buta lubang, sag, kepercayaan penutup tembaga, dll.

* Saat ini, saiz mikropori adalah 50~100 mikron, dan bilangan pori lapisan mencapai 3, 4 dan 5 arahan.

(3) Formasi grafik dan teknologi peletak tembaga

Teknologi dan kawalan pembayaran corak; Teknologi produksi corak yang baik; Teknologi kawalan keseluruhan penutup tembaga; Teknologi kawalan erosi mikro untuk corak yang baik.

* Keperluan jarak lebar corak semasa adalah 20~50 mikron. Keperluan keseluruhan penutup tembaga adalah 18* mikron, keseluruhan pencetak â¥90%.

(4) proses perlawanan penyeludupan * termasuk proses lubang penyeludupan, teknologi pencetakan perlawanan penyeludupan, dll.

* Perbezaan tinggi antara permukaan perlahan askar bagi Substrate IC kurang dari 10 mikron, dan perbezaan tinggi antara perlahan askar dan permukaan pad kurang dari 15 mikron.

(5) Teknologi rawatan permukaan

* kesesuaian tebal nikel/plating emas; Kedua-dua proses perlengkapan emas lembut dan keras pada piring yang sama; Proses nikel/palladium/plating emas.

* Lineable surface coating, selective surface treatment technology.

(6) Pengujian kemampuan dan teknologi pengujian kepercayaan produk

* Dipersediakan dengan sejumlah peralatan/alat ujian yang berbeza dari kilang PCB tradisional.

* Master reliability testing techniques different from conventional ones.

(7) Secara umum, produksi Substrate IC yang melibatkan lebih dari sepuluh aspek teknologi:

Pembalasan dinamik graf; Proses elektroplating grafik untuk keseluruhan tebal plating tembaga; Seluruh pengembangan bahan proses dan kawalan pengurangan; Proses perawatan permukaan, emas lembut dan emas keras elektroplating selektif, proses nikel/palladium/emas plating;

* Produksi wafer plat utama;

* Teknologi pengesan kepercayaan tinggi; Pemprosesan mikroporous;

* Jika mikro terpasang 3, 4, 5, proses produksi;

* Tekanan laminasi berbilang; Laminate ♥4 kali; Mengbor 5 kali; Elektroplat 5 kali.

* Formasi corak wayar dan pencetakan;

* Sistem penyesuaian ketepatan tinggi;

* Proses lubang penangkap penyelesaian, proses penuhian mikrolubang elektroplating;

Klasifikasi Substrate IC

Dengan bentuk penyampilan

Kebenaran Pakej

(1) BGA

*BallGridAiry, BGA, Spherical Array Package.

* Jenis pakej ini penyebaran panas papan, prestasi elektrik adalah baik, pin cip boleh meningkat jauh, dilaksanakan kepada nombor pin 300 (pincount) di atas pakej IC.

(2) CSP

*CSP, chipscalepackaging, chip level size packaging.

* Adakah pakej cip tunggal, berat ringan, kecil, saiz pakej dan saiz IC sendiri hampir sama atau sedikit lebih besar, digunakan dalam produk memori, produk komunikasi, nombor pin bukan produk elektronik yang tinggi.

(3) papan PCB kristal tertutup

* FlipChip (FC) adalah jenis pakej di mana sisi depan cip diputar (Flip) dan blok konveks secara langsung tersambung ke PCB.

Jenis substrat ini mempunyai keuntungan gangguan isyarat rendah, kehilangan sirkuit sambungan rendah, prestasi elektrik yang baik, penyebaran panas efisien dan sebagainya.

(4) Modul berbilang- cip

* Modul Multi-chip (MCM) Multi-chip dengan fungsi berbeza dalam pakej yang sama.

* Ini adalah penyelesaian terbaik untuk produk elektronik kepada cahaya, tipis, pendek, kurang daripada kelajuan tinggi tanpa wayar. Digunakan dalam komputer yang tinggi - perintahkan komputer besar atau produk elektronik prestasi istimewa.

* Kerana terdapat cip berbilang dalam pakej yang sama, gangguan isyarat, penyebaran panas, desain garis tipis, dan sebagainya, tiada lagi penyelesaian lengkap, yang termasuk dalam pembangunan aktif produk.

Oleh sifat bahan

(1) Papan PCB keras. mengunci memuatkan PCB

* Substrat pakej organik yang ketat dibuat dari epoksi, BT, resin ABF. Nilai output adalah kebanyakan substrat pakej IC. CTE (koeficien pengembangan panas) jangkauan dari 13 hingga 17ppm/ darjah Celsius.

(2) Penutupan plat lembut memuatkan PCB.

* Substrat pakej dibuat dari substrat resin PI (poliimid), PE (poliester), CTE 13 ~ 27ppm/ darjah Celsius.

(3) Substrat keramik

* Aluminum oxide, aluminum nitride, silicon carbide and other ceramic materials as the packaging substrate. CTE kecil, 6 ~ 8ppm/ darjah Celsius.

Dipecahkan oleh teknologi sambungan

(1) Main corak untuk melibatkan plat pembawa

* Kabel emas menyambung IC dengan PCB.

(2) PCB TAB

*TAB -- TapeAutomatedBonding

* Pin dalam cip tersambung dengan cip, dan pins luar tersambung dengan papan pakej.

(3) Overlay crystal bonding PCB.

*Filpchip, wafer adalah Filp bumped dan secara langsung sambung ke Substrate IC.