Proses Raka Chip IC

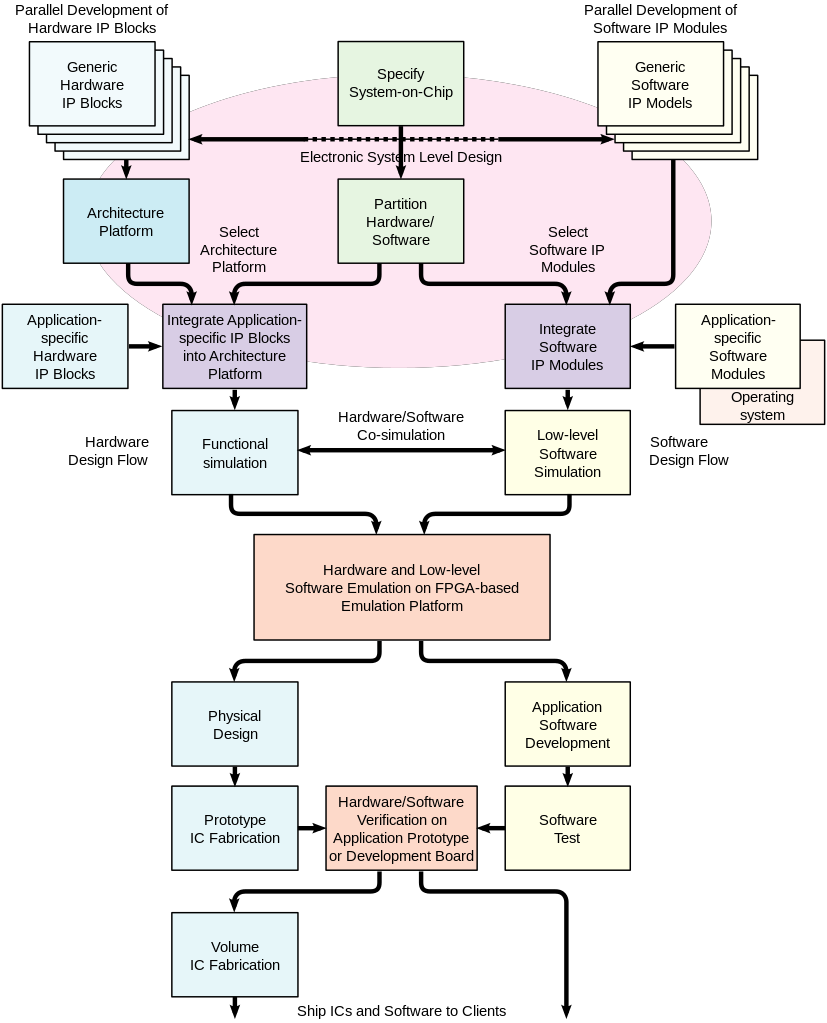

Desain IC Chip dibahagi ke desain bahagian depan dan desain bahagian belakang, desain bahagian depan (juga dikenali sebagai desain logik) dan desain bahagian belakang (juga dikenali sebagai desain fizik) bukanlah sempadan ketat bersatu, melibatkan desain berkaitan dengan proses adalah desain bahagian belakang.

Ciptaan bahagian depan IC Chip

1. Formulasi spesifikasi

Spesifikasi cip, seperti senarai ciri-ciri, adalah permintaan pelanggan kepada syarikat desain cip (dipanggil Fabless) yang termasuk keperluan fungsi dan prestasi khusus yang cip sepatutnya memenuhi.

2. Ralat terperinci

Kegagalan muncul dengan solusi desain dan arkitektur pelaksanaan berdasarkan spesifikasi pelanggan dan membahagi fungsi modul.

3. Pengkodan HDL

Penggunaan bahasa keterangan perkakasan (VHDL, Verilog HDL, syarikat industri biasanya digunakan dalam fungsi modul yang terakhir) untuk menggambarkan kod untuk mencapai, iaitu, fungsi sirkuit perkakasan sebenar diterangkan oleh bahasa HDL, bentuk kod RTL (aras pemindahan daftar).

4. Pengesahan simulasi

Pengesahan simulasi adalah untuk mengesahkan kebaikan desain pengekodan, dan piawai pengesahan adalah spesifikasi yang dibentuk dalam langkah pertama. Untuk melihat sama ada rancangan memenuhi semua keperluan dalam spesifikasi. Spesifikasi adalah piawai emas untuk rancangan yang betul, dan apa-apa yang tidak sesuai dengan spesifikasi perlu ditujukan semula dan dikod. Pengesahan desain dan simulasi adalah proses berulang sehingga keputusan pengeesahan menunjukkan keseluruhan persyaratan dengan spesifikasi. VCS Synopsys, dan NC-Verilog Cadence.

5. Sintesis logik -- Kompiler Design

Pengesahan simulasi telah lulus dan sintesis logik dilakukan. Hasil sintesis logik adalah untuk menerjemahkan kod HDL ke dalam senarai rangkaian. Sintesis perlu tetapkan keterangan, yang merupakan kriteria yang and a mahu litar integrasi untuk memenuhi dalam terma kawasan, masa dan sebagainya. Sintesis logik perlu berdasarkan perpustakaan sintesis khusus. Dalam perpustakaan berbeza, kawasan dan parameter masa bagi sel piawai asas sirkuit pintu berbeza. @ info Oleh itu, pemilihan perpustakaan yang meliputi bukanlah sama, sirkuit terintegrasi dalam masa, kawasan berbeza. @ info Secara umum, selepas sintesis selesai, pengesahan simulasi diperlukan lagi (ini juga dipanggil post-simulasi, dan yang terdahulu dipanggil pre-simulasi). Design Compiler untuk alat sintesis logik Synopsys.

6. STA

Analis Masa Statik (STA) : Analis Masa Statik (STA) : Analis Masa Statik (STA) : Analis Masa Statik (STA) : Analis Masa Statik (STA) : Analis Masa Statik (STA) : Analis Masa Statik (STA) : Analis Masa Statik (STA) : Analis Masa Statik (STA) : Analis Masa Statik (STA) : Analisi Masa Statik (STA) : Analisi Masa Statik (STA) : Analisi Masa Statik (STA) . Ini adalah pengetahuan asas sirkuit digital, register dengan dua pelanggaran masa ini, tiada cara untuk sampel data dan output dengan betul, jadi fungsi cip digital berdasarkan register pasti akan mempunyai masalah.

Alat STA mempunyai Synopsys Prime Time.

7. Pengesahan rasmi

Ini juga kategori pengesahihan, yang mengesahkan senarai rangkaian yang disintesis secara berfungsi (STA adalah masa). Kaedah yang biasa digunakan adalah pemeriksaan persamaan. Mengambil desain HDL selepas pengesahan fungsi sebagai rujukan, fungsi senarai rangkaian komprensif dibandingkan dengan menentukan sama ada ia secara berfungsi sama. @ info Ini dilakukan untuk memastikan tiada perubahan dalam fungsi sirkuit yang digambarkan awalnya dalam HDL semasa proses sintesis logik.

Formalitas Formalitas adalah alat Synopsys.

Proses desain bahagian depan ditulis di sini untuk masa ini. Dalam bentuk rancangan, hasil rancangan bahagian depan adalah untuk mendapatkan sirkuit netmeter pintu cip IC.

Cipta Cip IC desain belakang

1. DFT

Rancangan untuk Ujian. Chips sering mempunyai sirkuit ujian dalam, dan DFT dirancang dengan ujian masa depan dalam fikiran. pendekatan umum kepada DFT adalah untuk masukkan rantai imbas ke dalam rancangan untuk mengubah unit bukan-imbas (seperti register) ke unit imbas. Beberapa buku mempunyai maklumat terperinci tentang DFT, jadi mudah untuk memahaminya dengan membandingkan gambar.

Kompiler DFT bagi Sinopsi alat DFT

2. Rancangan Lantai

Perrancangan bentangan adalah untuk meletakkan modul unit makro cip dan menentukan kedudukan bagi berbilang sirkuit fungsional secara umum, seperti modul IP, RAM, pins I/O dan sebagainya. Perrancangan bentangan boleh mempengaruhi secara langsung kawasan cip akhir.

Alat adalah Astro untuk Sinopsis

3. CTS

Sintesis Pokok Jam, hanya diletakkan, adalah wayar Jam. Kerana fungsi arahan global isyarat jam dalam cip digital, distribusinya sepatutnya simetrik ke setiap unit daftar, sehingga jam dari sumber jam yang sama ke setiap daftar, perbezaan lambat jam adalah minimum. Inilah sebabnya isyarat jam perlu dihantar secara terpisah.

Alat CTS, Kompiler Fizik untuk Sinopsi

Kawalan di sini adalah wayar isyarat normal, termasuk wayar diantara pelbagai unit piawai (pintu logik asas). Contohnya, kita biasanya mendengar proses 0.13um, atau proses 90nm, sebenarnya lebar minimum kawat logam di sini, iaitu panjang saluran tabung MOS dari sudut pandang mikro.

Sinopsi alat Astro

5. Ekstrasi parameter parasitik

Kerana kebelakangan wayar sendiri, induksi antara wayar bersebelahan, kapasitasi terhubung di dalam cip boleh menghasilkan bunyi isyarat, saling bercakap dan refleksi. Kesan ini boleh menyebabkan masalah integriti isyarat, yang menyebabkan perubahan dan variasi tegangan isyarat, dan jika berat, ralat penyelesaian isyarat. Sangat penting untuk menganalisis masalah integriti isyarat dengan mengekstrak parameter parasit dan mengesahkan lagi.

Alat Sinopsis bintang-rCXt

6. Sahkan bentangan fizikal

Pada selesai pembatalan bentuk fizikal pengesahan fungsi dan masa, pengesahan banyak item, seperti pengesahan LVS (Skema Vs Bentuk), dalam pendek, adalah Bentuk dan sintesis logik pengesahan perbandingan sirkuit aras pintu; DRC (Pemeriksaan Peraturan Raka) : Semak Peraturan Raka, semak jarak garis, lebar garis untuk memenuhi keperluan proses, ERC (Semak Peraturan Elektrik) : Semak Peraturan Elektrik, semak sirkuit pendek dan sirkuit terbuka dan pelanggaran Peraturan Elektrik lainnya; Dan seterusnya.

Alat untuk Synopsys Hercules

Proses belakang sebenar juga termasuk analisis konsumsi kuasa sirkuit dan masalah DFM (Design Kemudahan Manufacturability) kerana proses pembuatan terus berkembang, yang tidak akan disebut di sini.

Pengesahan bentangan fizikal adalah selesai fasa reka cip keseluruhan, dan berikut adalah penghasilan cip. Bentangan fizikal diberikan sebagai fail GDS II kepada Foundry, atau Foundry, yang membuat sirkuit sebenar pada wafer silikon, mengepaknya dan mengujinya, dan and a mendapat cip sebenar yang anda lihat.

Dokumentasi proses untuk desain cip

Dalam pautan reka penting reka cip, seperti sintesis dan analisis masa, lukisan bentangan, dll., fail perpustakaan proses diperlukan. Namun, orang sering kurang memahami dokumen proses, jadi sukar untuk belajar sesuatu tentang desain cip sendiri. Contohnya, pembelajaran rancangan bentangan hanyalah projek kertas tanpa fail perpustakaan kad proses. @ info Artikel ini terutama memperkenalkan pengetahuan berkaitan perpustakaan proses.

Dokumentasi proses disediakan oleh pembuat cip, jadi perlu mempunyai pemahaman umum tentang pembuat cip domestik dan antarabangsa. Secara antarabangsa, terdapat pembuat semikonduktor utama seperti TSMC, Intel dan Samsung. Di China, terdapat kebanyakan SMIC, China Resources Shanghai, Shenzhen Founder dan syarikat lain. Syarikat-syarikat ini menyediakan dokumen perpustakaan proses yang berkaitan, tetapi premis adalah untuk bekerja sama dengan syarikat-syarikat ini untuk mendapatkan, dokumen proses ini adalah dokumen rahsia.

Fail perpustakaan proses lengkap kebanyakan terdiri dari:

1, perpustakaan proses simulasi, terutamanya menyokong dua spektrum perisian dan hSPICE, suffiks SCS -- Spectre, lib -- hSPICE penggunaan.

2, versi analog fail perpustakaan peta, terutamanya untuk perisian lukisan peta kadens, suffix tf, DRF.

3. Pustaka komprensif digital, terutamanya termasuk pustaka siri masa, komponen senarai jaringan asas dan analisis komprensif dan kronologi lain yang berkaitan memerlukan fail pustaka. Ia terutama digunakan untuk sintesis perisian DC dan analisis masa perisian PT.

4. Pustaka peta digital, terutamanya untuk perisian cadence Encounter untuk bentangan automatik dan routing, tentu saja, bentangan automatik dan alat routing juga akan menggunakan pustaka masa, fail kekangan terintegrasi, dan sebagainya.

5, perpustakaan pengesahan peta, terutamanya DRC, pemeriksaan LVS. Beberapa sokongan khusus Calibre, dan beberapa sokongan khusus Dracula, Diva dan alat pemeriksaan peta lain. Setiap fail perpustakaan mempunyai dokumen keterangan PDF yang sepadan.

Desain terbalik akan menggunakan fail perpustakaan proses 1, 2, 5, 3 dan 4 tidak akan digunakan. @ info Reka maju (reka maju yang bermula dengan kod) memerlukan semua fail. @ info Dokumen proses yang sepatutnya mengandungi kedudukan yang sangat penting dalam desain cip, desain kunci pada setiap pautan digunakan, ditambah sifat rahsia, jadi sukar untuk mencari dokumen proses lengkap dalam rangkaian untuk pembelajaran individu, mempunyai kadensi EETOP terbuka untuk fail perpustakaan proses pembelajaran peribadi boleh berguna bagi semua orang untuk belajar, tetapi juga kelihatan tidak lengkap.

Sintesis desain cip

Apa itu sintesis? Sintesis adalah proses untuk mengubah/memetakan kod Verilog aras RTL ke sirkuit yang diwakili oleh unit aras pintu asas menggunakan alat Kompiler Design. Unit gerbang asas adalah gerbang nand, atau gerbang nand, daftar, dll., tetapi unit gerbang ini telah dibuat ke perpustakaan piawai unit yang kita boleh panggil secara langsung dengan perisian, daripada perlu panggil unit gerbang sendiri untuk membina sirkuit. Dalam terma sederhana, perisian Design Compiler melakukan tugas untuk menerjemahkan kod ke dalam sirkuit sebenar, tetapi ia bukan hanya mengenai menerjemahkan, ia mengenai optimizasi sirkuit dan keterangan masa untuk membuat mereka sesuai dengan keperluan prestasi yang kita tetapkan. Seperti yang disebutkan sebelumnya, perisian dipandu kekangan, jadi dari mana kekangan itu berasal? Jawapannya ialah, spesifikasi rancangan. Setiap projek desain cip akan mempunyai spesifikasi projek, yang dikembangkan pada permulaan desain cip, dalam langkah keseluruhan perancangan (lihat di atas). Hadangan khusus perlu dipertimbangkan dengan berhati-hati semasa proses integrasi. Proses umum sintesis:

1. Proses prasintesis;

2. Memaksa proses penghalangan desain;

3. Proses sintesis desain;

4. Proses post-sintesis.

PS, syarat-syarat untuk menggunakan perisian Design Compiler adalah untuk belajar menggunakan skrip TCL DC.

Proses presintesis. Bahagian ini merupakan persiapan fail perpustakaan (termasuk perpustakaan proses, perpustakaan pautan, perpustakaan simbol, dan perpustakaan komprensif) yang digunakan oleh proses komprensif, fail input desain, dan tetapkan parameter persekitaran.

Mengeset keterangan desain pada proses. @ info: whatsthis Bahagian ini terutama mengenai menulis fail kekangan menggunakan skrip TCL DC. Item keterangan khusus boleh dibahagi ke tiga kategori:

A, keterangan kawasan, takrifkan jam, keterangan laluan input/output;

B. (atribut persekitaran), halang pemacu input, halang muatan output, tetapkan keadaan kerja (kes terbaik, biasa, terburuk), dan tetapkan model muatan baris;

C. (kekangan jam maju), kegelisahan jam, ofset, lambat sumber jam, jam berbilang-jam segerak, jam asinkron, laluan berbilang-siklus, kategori kekangan terperinci ini.

Begitu banyak untuk keterangan. Fail halangan skrip TCL terperinci mengandungi hampir semua halangan di atas. Ada keterangan di belakang model.

Rancangkan proses terintegrasi. @ info: whatsthis Ia terutama memperkenalkan perancangan modul sirkuit Raka (untuk keterangan yang lebih baik), proses optimasi kompiler Raka yang meliputi (tiga tahap optimasi, aras struktur, aras logik, aras pintu), proses spesifik analisis urutan masa dan maklumat terperinci lain dalam proses meliputi.

Proses sintesis pos. Bagaimana anda melihat hasil sintesis? Bagaimana anda menyelesaikan pelanggaran masa? Itulah apa yang proses post-sintesis semua tentang. Setelah sintesis, melalui analisis laporan sintesis, kita boleh tahu bagaimana hasil sintesis sirkuit, mengikut keperluan yang tidak memenuhi, mengendalikan semula, atau bahkan merencanakan semula sirkuit. Terutama pada tahap ini adalah ramalan yang meliputi, kerana apabila menulis keterangan yang meliputi skrip, and a perlu menentukan keterangan, spesifikasi secara umum tidak boleh melibatkan seksyen rincian, jadi perlu ramalan yang meliputi mengikut sirkuit sebenar, selepas langkah ini berada dalam kod, dan uji pada masa yang sama, - untuk kira-kira sirkuit adalah sesuai dengan keperluan, dalam kes ini, proses presintesis adalah sama dengan sintesis formal, tetapi keperluan adalah jauh lebih santai. Keperluan pelanggaran masa adalah kira-kira 10%-15%, iaitu, ia tidak penting jika 10%-15% sirkuit tidak memenuhi masa.

conclusion(iPCB.com)

Proses desain cip sangat kompleks, artikel ini juga merupakan proses merancang cip sederhana comb lagi, kompleks tidak akan berulang.