Saiz cip tahap Wafer Packaging (WLCSP) status aplikasi teknologi dan analisis prospek pasar pada tahun 2021.

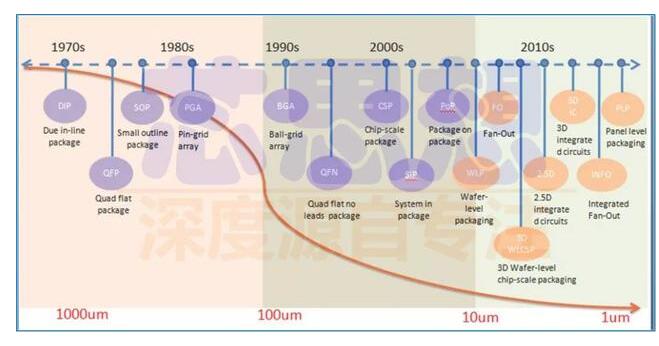

Pakej IC Lanjutan merujuk kepada bentuk pakej paling terbaik dan teknologi pada masa itu. Pada masa ini, pakej dengan struktur cip terbalik (FC), pakej aras wafer (WLP), pakej 2.5D, pakej 3D dianggap sebagai kategori pakej maju.

Diagram sirkuit pembangunan pakej lanjutan

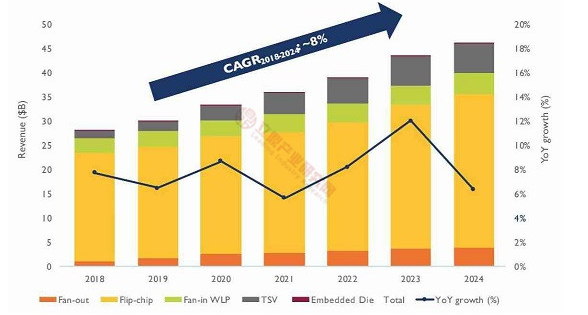

Pasar pembekalan setengah konduktor keseluruhan dijangka akan tumbuh dalam pendapatan dengan kadar pertumbuhan tahunan (CAGR) berkumpul 5.2% dari 2018 hingga 2024, sementara pasar pembekalan lanjut dijangka akan tumbuh pada CAGR 8% dan saiz pasar akan tumbuh kepada $40 bilion hingga 2023. Pasar pakej tradisional, pada sisi lain, tumbuh di cagR kurang dari 3.3%. diantara pelbagai platform pakej maju, silikon 3D melalui lubang (TSV) dan pakej fan-out (FAN-out) akan tumbuh 29% dan 15%, respectively. Pakej Flip-chip, yang mengandungi kebanyakan pasar pakej maju, akan tumbuh dengan kadar pertumbuhan tahunan berkumpul sekitar 8 peratus. WLP penggemar masuk, sementara itu, juga akan tumbuh pada CAGR 8 peratus, dipandu terutama oleh pasar bimbit.

Saiz Pasar Teknologi Pengepasan Lanjutan Global, ramalan 2018-2024 (kami $1 bilion)

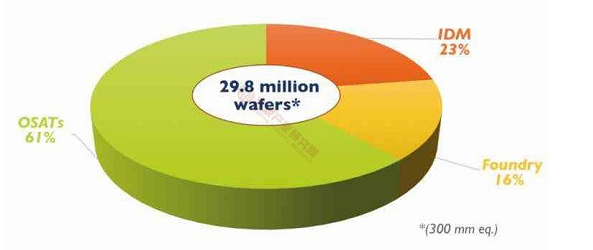

Selain itu, terdapat perkembangan yang berkembang untuk menggabungkan penghasilan wafer bahagian depan dengan pakej bahagian belakang yang maju. Pembuat wafer global utama (seperti Intel, TSMC dan Samsung) telah menggabungkan teknologi pembinaan wafer maju dengan bentuk pakej maju untuk menguatkan keuntungan integrasi teknologi pembinaan produk IC. Dipengaruhi oleh teknologi dan skala, konsentrasi industri penyegelan dan ujian global telah terus meningkat. Sebelum 2017, lapan perusahaan penyegerakan dan ujian (termasuk perniagaan pembekalan belakang penerbangan) memegang kira-kira 87% daripada bahagian pasar pembekalan lanjut.

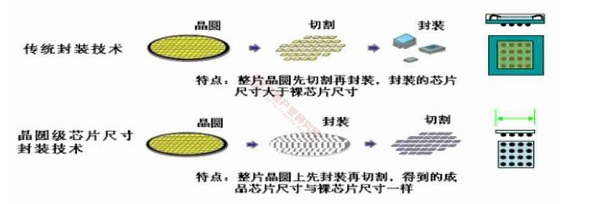

Pakej saiz cip aras gelombang (WLCSP), sebagai jenis teknologi pakej maju, memenuhi keperluan dan trends pembangunan elektronik konsumen (ringan, kecil, pendek, tipis dan harga rendah). Berbanding dengan pakej tradisional, pakej WLCSP mempunyai keuntungan utama berikut: (1) WLCSP optimize rantai industri pakej. Dalam kaedah pakej tradisional, wafer pertama dipotong ke dalam cip pelet. Selepas diuji sebagai cip berkualifikasi, wafer ditempatkan pada bingkai utama atau substrat pakej (substrat), kemudian ujian pakej dilakukan. Rantai industri melibatkan kilang wafer, kilang substrat, kilang penyegelan dan kilang ujian. Pakej saiz wafer adalah untuk menguji wafer, kemudian memotong wafer selepas encapsulation dan ujian. Compared with traditional packaging, WLCSP packaging can integrate the substrate factory, packaging factory and test factory in the traditional packaging industry chain into one, so that the chip production cycle is greatly shortened, the production efficiency is improved, and the production cost is reduced. Kedua, pakej WLCSP boleh mengurangi ujian cip berkualifikasi sebelum pakej, dan boleh mengurangi biaya pakej secara efektif; . Akhirnya, pakej WLCSP adalah sambungan teknologi penghasilan wafer, yang mengurangkan perbezaan teknikal antara segmen belakang semikonduktor (pakej) dan segmen depan (penghasilan wafer), yang memudahkan untuk menyedari docking teknikal antara segmen belakang semikonduktor dan segmen depan. Pakej WLCSP boleh menyertai desain IC, penghasilan wafer, ujian pakej, kilang substrat ke satu, optimize rantai industri, menyelesaikan masalah docking teknikal dan piawai dalam desain IC, penghasilan wafer, ujian pakej, kilang substrat dan pautan lain, dan lebih lanjut mempromosikan pembangunan mod penapis profesional.

Bilangan wafer menggunakan pakej lanjut (sama dengan 12 inci) dan distribusi mengikut model perniagaan pada 2018

2. Biaya pakej berkurang dengan meningkat bilangan cip di wafer. Pakej saiz cip aras wafer adalah untuk pakej seluruh wafer dan kemudian memotong cip, sementara pakej tradisional adalah untuk memotong wafer ke dalam cip dahulu, dan kemudian laksanakan pakej cip. Secara umum, biaya pakej WLCSP diukur mengikut bilangan wafer, dan bilangan cip selepas memotong tidak perlu berkaitan dengan biaya pakej tradisional diukur mengikut bilangan cip yang dikumpulkan. Oleh itu, biaya pakej WLCSP berkurang semasa saiz wafer meningkat dan bilangan cip meningkat. Dalam peningkatan pembangunan pasar elektronik konsumen cahaya, kecil, pendek, tipis, saiz cip tahap wafer keuntungan pengimbangan adalah lebih jelas, akan secara perlahan-lahan menggunakan bahagian pasar pakej tradisional.

3. WLCSP akan menjadi kaedah pembekalan aliran utama di masa depan. Industri percaya bahawa teknologi pakej 3d berdasarkan silikon melalui lubang (TSV) adalah penyelesaian utama di luar Hukum Moore, dan adalah trend pembangunan masa depan teknologi pakej setengah konduktor. Pakej WLCSP adalah asas silikon melalui teknologi lubang, dan kedua-dua proses sangat mirip. Dengan menguasai teknologi pakej WLCSP (terutama Shellcase series WLCSP), kita boleh cepat memasuki medan silikon melalui teknologi lubang dan bermain peran utama dalam teknologi pakej 3D masa depan.

Perbezaan antara pakej saiz cip tahap wafer dan pakej tradisional

Yole Development meramalkan pasar pakej WLCSP akan tumbuh dari kira-kira $1.4 bilion pada 2010 kepada $3.2 bilion pada 2018 dengan kadar pertumbuhan tahunan berkumpulan 12%, menganggap kira-kira 11% pakej maju dan kira-kira 6% industri beta tertutup global. Dipandu oleh permintaan untuk cip saiz kecil seperti elektronik konsumen dan elektronik kenderaan, kami mengharapkan pasar pakej WLCSP mencapai kira-kira $3.5 bilion pada 2019, dengan pertumbuhan lanjut dijangka.

WLCSP terutama mengadopsi pakej bump wafer dan teknologi pakej seri Shellcase WLCSP. Pakej bump gelombang adalah bentuk pakej WLCSP dengan kesulitan teknikal relatif rendah. Ciri utamanya ialah bahawa sirkuit dan pad penywelding boleh dihantar secara langsung ke depan cip. Serye Shellcase WLCSP tidak hanya boleh memimpin sirkuit dan pad penywelding langsung di hadapan cip, tetapi juga memimpin sirkuit cip ke belakang cip dan kemudian membuat pad penywelding. Pakej WLCSP series Shellcase mengandungi titik teknikal kunci pakej bump wafer, yang lebih sukar daripada pakej bump wafer, dan proses lebih kompleks daripada pakej bump wafer. Kerana perbezaan yang signifikan dalam kesulitan teknikal dan medan aplikasi, harga unit teknologi pembekalan bump wafer lebih rendah daripada teknologi pembekalan seri Shellcase. Serye Shellcase WLCSP mempunyai keuntungan yang baik dalam pakej sensor imej, sementara pakej bump wafer tidak boleh dilaksanakan pada sensor imej dan medan lain kerana pad penywelding di hadapan cip.

Circuit IPCB adalah pembuat papan litar PCB dengan ketepatan tinggi profesional, boleh mengeluarkan batch menghasilkan papan PCB 4-46 lapisan, papan litar, papan litar, papan frekuensi tinggi, papan kelajuan tinggi, papan HDI, papan litar PCB, papan kelajuan tinggi frekuensi tinggi,papan muatan segel IC, papan ujian setengah konduktor, papan litar berbilang lapisan,papan litar HDI, papan litar voltaj bercampur, - papan sirkuit frekuensi tinggi, papan lembut dan keras, dll.

Pada tahun 2018, saiz pasar substrat pakej adalah hampir $7 bilion