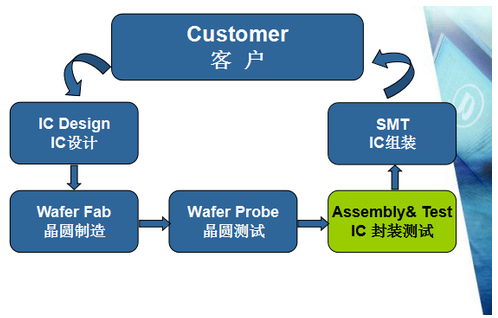

Pemakaian cip IC dan proses ujian:

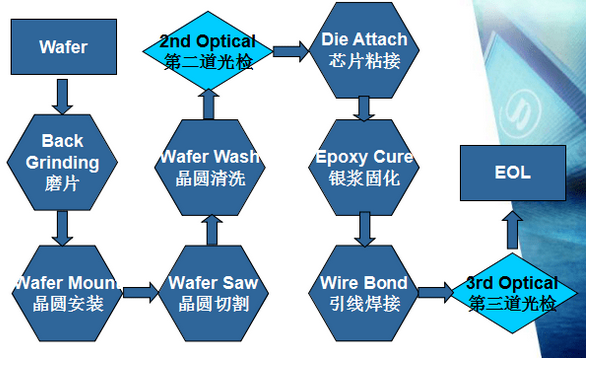

Proses

Pakej IC merujuk kepada cip (Die) dan jenis berbeza bingkai (L/F) dan bahan penyegelan plastik (EMC) yang dibentuk oleh bentuk berbeza tubuh Pakej.

Terdapat banyak jenis pakej IC, yang boleh diklasifikasikan sebagai berikut:

Menurut bahan pakej, ia boleh dibahagi menjadi:

Pakej logam, pakej keramik, pakej plastik

Pakaian logam terutama digunakan dalam teknologi tentera atau angkasa udara, tiada produk komersial;

Pakej keramik lebih baik daripada pakej logam, juga digunakan dalam produk tentera, sejumlah kecil pasar komersial;

Pakaian plastik untuk elektronik pengguna, biaya rendah, proses sederhana, kepercayaan tinggi dan menguasai kebanyakan bahagian pasar;

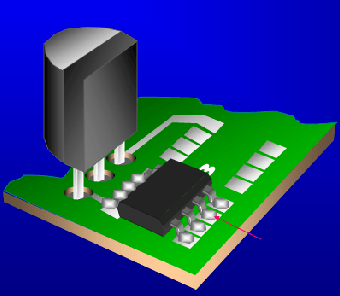

Menurut mod sambungan dengan papan PCB, ia boleh dibahagi ke:

Pakej PTH dan pakej SMT

PTH-Pin Melalui Lubang;

SMT-Surface Mount Technology.Sekarang, kebanyakan IC di pasar diterima untuk jenis SMT.

Menurut penampilan pakej, ia boleh dibahagi ke:

SOT, SOIC, TSSOP, QFN, QFP, BGA, CSP, dll.

Dua faktor kunci menentukan bentuk encapsulasi:

Efisiensi enkapsulasi. Kawasan/kawasan pakej Chip, sebanyak mungkin kepada 1:1;

Nombor Pin. Semakin banyak pin, semakin maju, tetapi kesukaran proses juga meningkat sesuai;

Di antara mereka, CSP, disebabkan penggunaan teknologi Flip Chip dan pakej Chip kosong, kawasan/pakej Chip =1:1, yang merupakan teknologi paling lanjut pada masa ini.

QFN -- Quad Flat Pakej tanpa-pemimpin QFN -- Quad Flat Pakej tanpa-pemimpin

SOIC - Pakej IC Garis Luar Kecil

TSSOP - Pakej Garis Luar Kecilan Kecil Gelap

QFP - Pakej Flat QuadStencils

BGA -- Pakej Array Grid Bola

CSP - Chip Scale Package Chip Scale Package

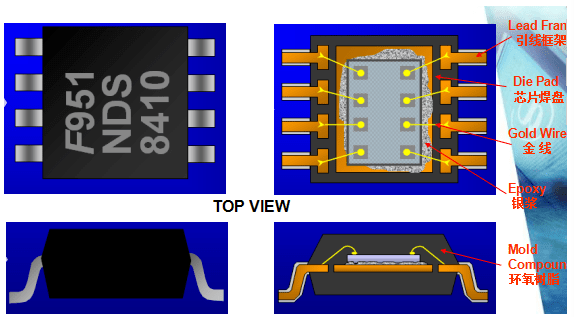

Struktur Pakej IC

Bahan Raw dalam Kumpulan Waferã

Bingkai Pemimpin

Memberikan sambungan sirkuit dan pemasangan Die;

Bahan utama ialah tembaga, yang akan ditutup dengan perak dan NiPdAu.

Proses L/F termasuk Etch dan Stamp;

Mudah untuk oksidasi, disimpan dalam kabinet nitrogen, kelembaman kurang dari 40%RH;

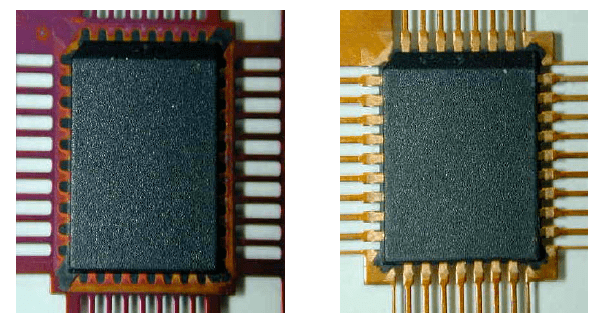

Kecuali BGA dan CSP, pakej lain akan menggunakan Bingkai Lead, sementara BGA akan menggunakan Substrate;

Kabel Emas

Untuk menyadari sambungan elektrik dan fizik antara cip dan bingkai utama luaran;

Benang emas 99.99% emas yang bersih;

Pada masa yang sama, kerana pertimbangan biaya, wayar tembaga dan proses wayar aluminum sedang digunakan. Keuntungan adalah bahawa biaya dikurangkan, dan kesulitan proses meningkat, hasil dikurangkan;

Diameter wayar menentukan arus yang boleh dihantar; - 0.8 mil, 1.0 mil, 1.3 mil, 1.5 mil dan 2.0 mil;

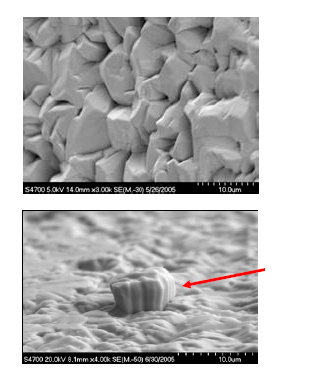

Komponen utama resin Mold Compound/epoxy adalah: resin epoxy dan pelbagai aditif (ejen penyembuhan, pengubahsuai, ejen pelepasan Mold, ejen penapis, ejen penapis api, dll.);

Fungsi utama adalah sebagai berikut: Bingkai Mati dan Pemimpin dibungkus dalam keadaan cair untuk menyediakan perlindungan fizikal dan elektrik dan mencegah gangguan luaran;

Keadaan penyimpanan: 5° di bawah sifar, 24 jam di bawah suhu normal;

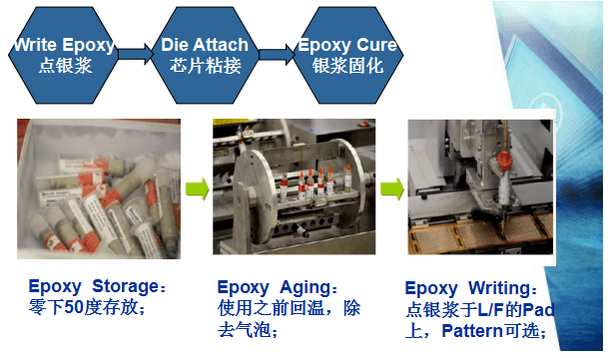

Epoksia.

Serbuk logam penuh resin epoksi (Ag); - Ia mempunyai tiga fungsi: memperbaiki Die pada Die Pad; - Pencerahan panas, kesan konduktif;

-50° dibawah penyimpanan, sebelum menggunakan suhu kembali 24 jam;

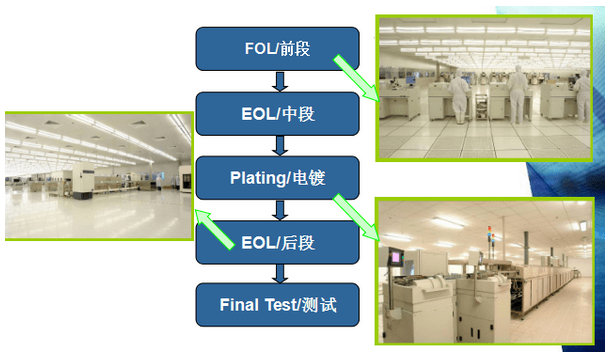

FOL-Front of Line

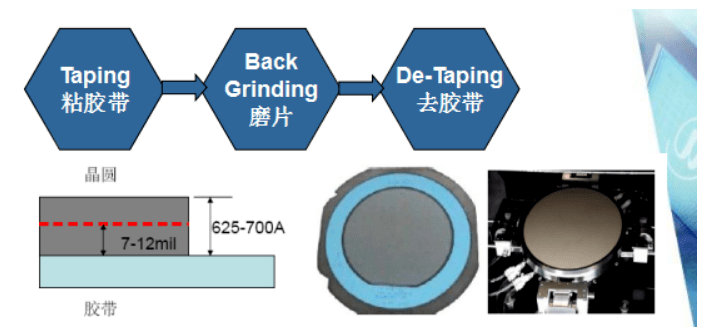

FOL-Back Grinding

Wafer dari kilang Wafer adalah tanah di belakang untuk mengurangi tebal Wafer yang diperlukan untuk pakej (8 mils~10 mils).

Apabila menggiling, perlu meletakkan pita pada Kawasan Aktif untuk melindungi sirkuit dan menggiling belakang pada masa yang sama. Selepas menggiling, buang pita dan mengukur tebal;

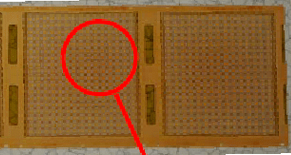

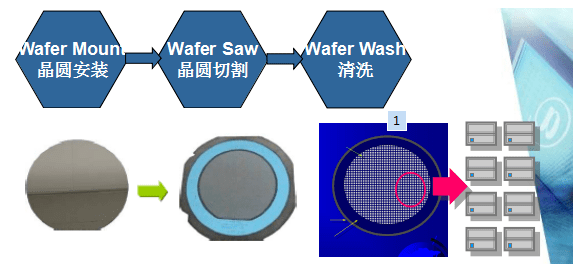

"Wafer Saw"

Wafer ditempatkan pada filem biru (Mylar) sehingga ia tidak akan hancur walaupun dibuka;

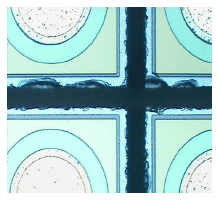

Potong seluruh Wafer menjadi Dice independen melalui Saw Blade untuk memudahkan Die Attach dan proses lain di belakang.

Bersihkan debu yang dihasilkan oleh Saw, dan bersihkan Wafer;

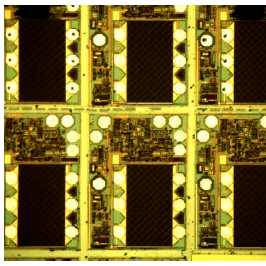

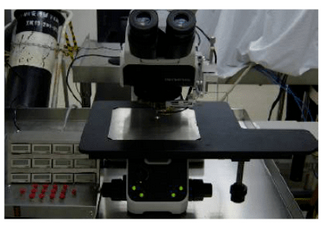

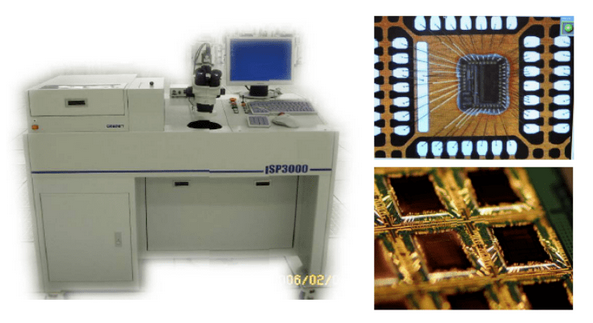

FOL -- Pemeriksaan Optik Kedua

Tujuan utama adalah untuk memeriksa penampilan Wafer di bawah mikroskop selepas Wafer Saw untuk melihat jika ada sebarang sampah.

Constellation name (optional)

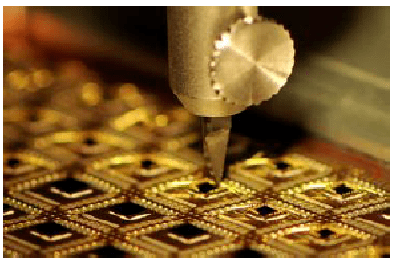

Proses pemilihan chip:

1. Ejector Pin mengangkat cip dari Mylar di bawah wafer, membuat mudah untuk berpisah dari filem biru;

2.Cip ditangkap dari atas untuk menyelesaikan proses pengangkutan dari Wafer ke L/F;

3. Kumpulkan Bond cip pada Pad L/F dengan paste perak dengan kekuatan tertentu, dan kedudukan tertentu boleh dikawal;

4, Resolusi Kepala Bond: x-0.2um; . Y - 0.5 um; - Z - 1.25 um;

5. Kelajuan Kepala Bond: 1.3m/s;

FOL "Epoxy Cure"

175°C, 1 jam; persekitaran N2, untuk mencegah oksidasi:

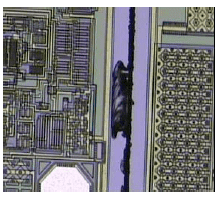

Semak kualiti Sambungan Mati:

Die Shear

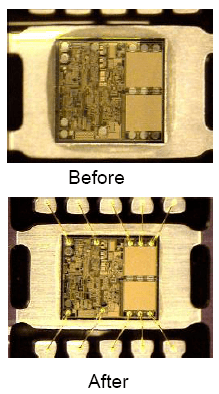

Pengikatan Kabel

Kabel emas yang bersih tinggi (Au), tembaga (Cu) atau aluminium (Al) digunakan untuk menyambung Pad dan Lead dengan penywelding. Pad adalah titik sambungan luaran sirkuit pada cip, dan Lead adalah titik sambungan pada Bingkai Pemimpin.

W/B adalah proses paling kritik dalam proses pakej.

Pemeriksaan Optik ke-3

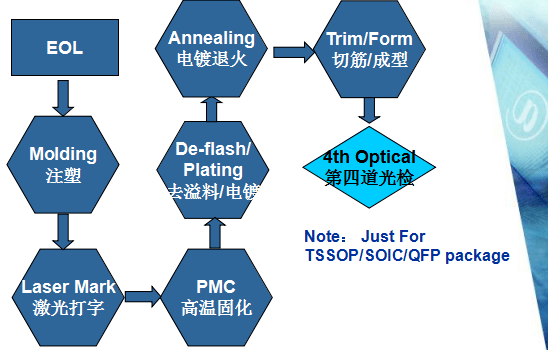

EOL â™ End of Line

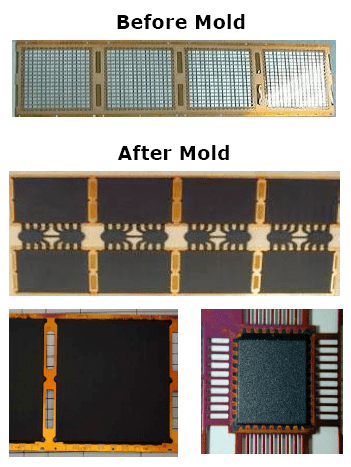

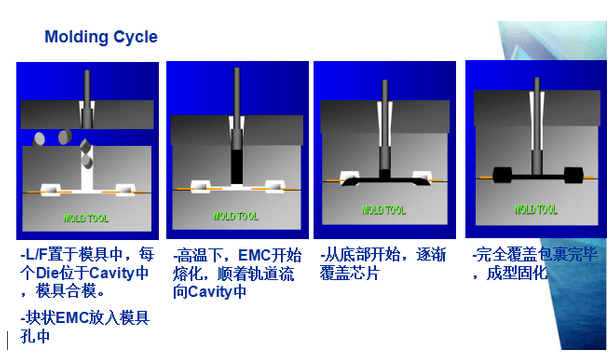

EOL â™ Molding

EOL â™ Laser Mark

Letter laser di hadapan atau belakang Pakej. Kandungan termasuk: nama produk, tarikh produksi, batch produksi, dll.

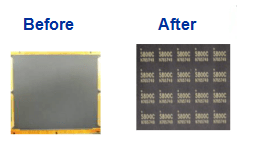

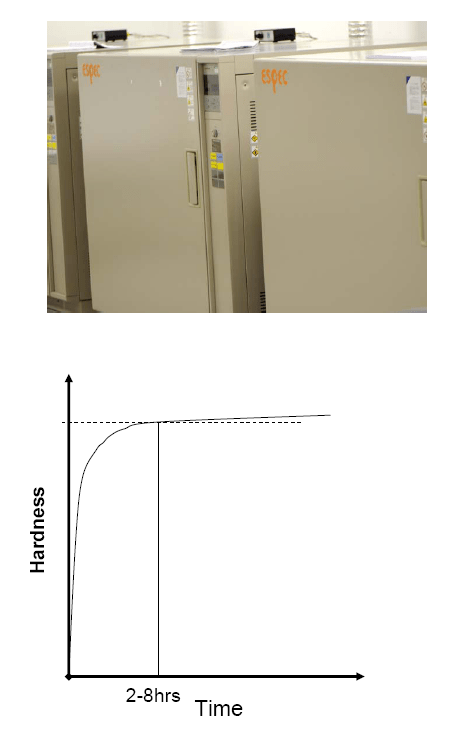

EOL â™ Post Mold Cure

Digunakan untuk menyembuhkan plastik selepas Molding untuk melindungi struktur dalaman IC dan menghapuskan tekanan dalaman. Temp penyembuhan: 175 + / - 5 ° C; - Masa penyembuhan: 8 HRS

EOL â™ De-flash

Tujuan: tujuan de-Flash adalah untuk menghapuskan melampaui batas Molding antara petunjuk di sekitar tubuh selepas Molding; - Kaedah: Soak dengan asid lemah dan cuci dengan air tekanan tinggi.

EOL â™ Plating

Dengan menggunakan kaedah metalik dan kimia, penutup diterapkan pada permukaan bingkai Lead untuk mencegah kesan persekitaran luaran (basah dan panas). Dan membuat komponen di papan PCB mudah untuk diseweld dan meningkatkan konduktiviti elektrik.

Biasanya terdapat dua jenis elektroplating:

bebas Pb: elektroplating bebas lead, menggunakan >99.95% Tin (Tin) yang bersih tinggi, untuk teknologi semasa yang digunakan secara luas, sesuai dengan keperluan RoHS;

Ia adalah liga tin-lead. Tin mengandungi 85%, dan Lead mengandungi 15%. Kerana ia tidak sesuai dengan RoHS, ia pada dasarnya dibuang pada masa ini.

EOL â™ Post Annealing Bake

Objektif: Biarkan produk selepas elektroplating bebas lead bakar pada suhu tinggi selama beberapa masa, untuk menghapuskan masalah pertumbuhan Whisker yang berpotensi elektroplating; Keadaan: 150 + / - 5 - c; . 2Hrs;

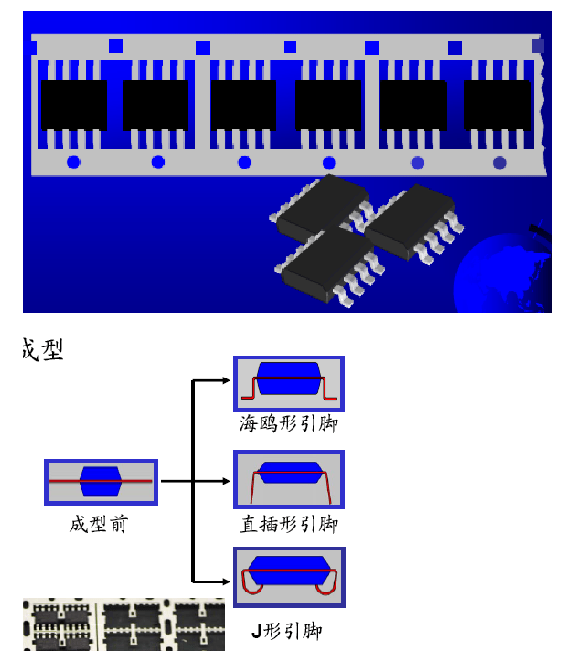

Proses untuk memotong Bingkai Pemimpin bagi potongan ke unit individu (IC); Bentuk: Bentuk produk IC selepas Trim, mencapai bentuk yang diperlukan oleh proses, dan meletakkannya ke dalam Tong atau Dulang;

EOL â™ Final Visual Inspection

Periksa penampilan produk di bawah kaca peningkatan kuasa rendah.

5. Fokus pada produk sampah yang berpotensi dari proses EOL seperti cacat Molding, cacat plating, cacat Trim/Form dll.