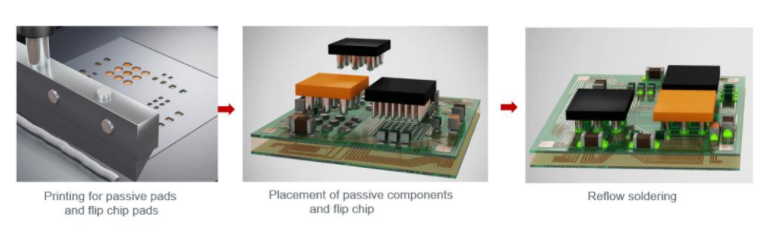

Putar cip, seperti nama menunjukkan, adalah kaedah pakej yang mana sisi depan cip (sisi di mana sirkuit IC dibuat) disambung ke bawah substrat. Terminal isyarat elektrik dibuat dari solder tradisional dan boleh disambung dengan substrat. Dalam jenis sambungan ini, terminal input dan output (I/O) boleh meliputi seluruh cip, jadi walaupun pada titik yang sama, ketepatan sambungan cip-balik jauh lebih tinggi daripada ikatan wayar. Dalam sambungan ikatan wayar, I/O hanya boleh diatur sekitar cip. Oleh itu, tidak peduli seberapa kecil lapangan, ketepatan I/O sambungan cip-putar tidak boleh dicapai. Kemudian teknologi bump adalah kunci untuk seluruh teknologi sambungan flip-chip.

Pandangan ringkasan teknologi PemberontakThe key to making wafer bumps is to deposit an under bump metal layer (UBM). Ia perlu dikatakan bahawa term a yang digunakan oleh IBM pada hari awal adalah lapisan metalisasi terhalang bola (BLM), yang berfungsi sebagai: untuk menyediakan lapisan ikatan untuk sambungan; untuk menyediakan lapisan penghalang penyebaran atom untuk mencegah penyebaran atom bahan bump ke struktur logam yang didasarkan; Material dielektrik dan logam yang didasarkan menyediakan lapisan melekat dan bertindak sebagai lapisan halangan untuk menghalang kontaminan dari migrasi ke logam yang didasarkan sepanjang arah mengufuk lapisan dielektrik. Kebanyakan UBM yang kini digunakan dibuat oleh proses sputtering. Proses pemutar adalah yang paling berkesan untuk membuat UBM. Terutama dibandingkan dengan proses penapisan. Faktor paling langsung yang mempengaruhi kepercayaan struktur bump askar adalah kualiti produksi UBM. Secara umum, struktur UBM mesti menahan kembali berbilang (sering sampai 20) tanpa kerosakan. Oleh kerana UBM adalah struktur yang digunakan untuk ikat bumps solder dan lapisan metalisasi pad bersama-sama, ia juga mesti lulus tekanan pemotong dan ujian tekanan tegang. Dalam ujian kerosakan mekanik, kriteria umum untuk gagal bump askar adalah kegagalan berlaku dalam askar sendiri. Oleh itu, UBM mesti mempunyai kekuatan yang cukup. Tiada kerosakan prestasi disebabkan faktor seperti masa, suhu, kelembapan, dan ketegangan bias.

Flip chip market trendsFlip chip packaging has become the mainstream packaging interconnection technology. Sejauh ini, cip terbalik sebenarnya dianggap jenis pakej, bukan teknologi sambungan. Contohnya, Flip Chip Ball Grid Array Packaging (FCBGA) terutamanya menggunakan teknologi substrat lapisan untuk menyelesaikan proses pengumpulan dan pengumpulan, tetapi ia terbatas kepada aplikasi sirkuit terintegrasi prestasi tinggi. Figur berikut menunjukkan kawasan aplikasi cip terbalik:

(1) Pitch bump: mengurangi pitch bump boleh meningkatkan ketepatan I/O; perkembangan perubahan landasan (perubahan berturut-turut dari 250 mikron ke 125 mikron);

(2) Kaedah tenggelam bump Solder: pencetakan-elektroplating skrin penguap;

(3) Komposisi solder bump: kandungan lead-eutectic-lead-free (Sn-Ag)-Cu lajur pitch<125 mikron;

(4) Komposisi pakej: substrat keramik substrat-densiti tinggi intersambung substrat-prepreg laminat substrat-rendah koeficient ekspansi panas substrat laminat? Substrat tanpa asas.

(5)Struktur pakej: penutup cip tunggal terkunci (SPL)-penutup cip tunggal tidak terkunci

Pasar aplikasi FCCSP tradisional adalah seperti ini:

Pasar aplikasi FCCSP:

(1) Kepadatan bump (I/O) relatif dengan saiz cip: digunakan untuk saiz cip >200 I/O atau >5.5 mm; produk densiti lebih rendah menggunakan WLCSP untuk biaya yang lebih baik dan lebih rendah.

(2) Kuasa rendah: kuasa umum<2w bergantung="" on="" chip="" board-level="" packaging="" can="" be="" used="" for="" power="" bare="" fccsp=">2W).

(3) Kawasan: Untuk peranti komputer telapak, teknologi 40nm/65nm mengurangkan saiz cip, tetapi lebih I/O membuat tidak ada kawasan yang cukup untuk mengatur I/O periferi, jadi perlu menggunakan substrat memimpin untuk mengeluarkan kawasan.

(4) Harga: Untuk cip saiz kecil I/O tinggi, kawasan periferik yang tidak cukup, kost Au garis, dan substrat saiz besar untuk peminat-keluar utama akan mendorong pembangunan FCCSP harga yang bersaing.

(5) Molding, mudah diuji dan memegang, bentuk umum sama dengan CABGA.

Ringkasan

Chip terbalik sentiasa teknologi pakej yang menarik. Tetapi dibandingkan dengan pakej ikatan wayar tradisional, had biayanya terbalik cip untuk menjadi teknologi utama. Namun, penghalangan biaya secara perlahan-lahan akan dibuang, dan penggunaan cip-cip berpakaian-strip telah mengurangi biaya mereka secara signifikan. Oleh kerana substrat laminasi menganggap sebahagian besar kos produk, mengurangi kos substrat laminasi adalah cara yang paling efektif untuk mengurangi kos pakej flip-chip.

Selain itu, untuk rancangan FPFC, Amkor telah melakukan banyak kajian untuk mengubah rancangan tata kawasan yang wujud flip-chip ke rancangan pitch-fine. 80% daripada kajian ditemukan bahawa rancangan periferik-lapisan halus boleh mengurangi kos substrat, yang disebabkan mengurangi lapisan logam dan mengurangi saiz luaran. Dengan mengurangi biaya pembekalan flip-chip substrat (biaya adalah yang tertinggi), ia mungkin untuk membuat pembekalan flip-chip digunakan dengan luas di pasar lain.