Via papan salinan PCB muncul sebagai titik henti pada garis pemindahan, yang akan menyebabkan refleksi isyarat. Secara umum, impedance yang sama dengan melalui adalah kira-kira 12% lebih rendah daripada garis penghantaran. Contohnya, penghalang garis transmisi 50 ohm akan menurun 6 ohm apabila melewati melalui (secara khusus, ia berkaitan dengan saiz dan tebal melalui, bukan pengurangan mutlak). Bagaimanapun, refleksi disebabkan oleh impedance berhenti melalui adalah sebenarnya sangat kecil. Koeficien refleksi hanya: (44-50)/(44+50)=0.06. Masalah disebabkan melalui lebih berkonsentrasi pada kapasitas parasit dan induktan. Impak.

Melalui dirinya sendiri mempunyai kapasitas parasit tersesat. Jika diketahui bahawa diameter topeng solder pada lapisan tanah melalui adalah D2, diameter pad melalui adalah D1, tebal papan PCB adalah T, dan konstan dielektrik substrat papan Untuk ε,

kapasitas parasit melalui adalah sama dengan: C=1.41ε Kapsitas parasit melalui akan mempunyai kesan utama pada sirkuit adalah untuk memperpanjang masa naik isyarat dan mengurangkan kelajuan sirkuit. Contohnya, untuk PCB dengan tebal 50Mil, jika diameter pad melalui ialah 20Mil (diameter lubang ialah 10Mil), dan diameter topeng askar ialah 40Mil, maka kita boleh kira-kira lubang melalui formula di atas Kapensiti parasit adalah kira-kira:

Perubahan masa naik disebabkan oleh bahagian ini kapasitasi adalah kira-kira:

Dari nilai-nilai ini, ia boleh dilihat bahawa walaupun kesan keterlaluan meningkat disebabkan oleh kapasitasi parasit satu melalui tidak terlalu jelas, jika melalui digunakan berbilang kali dalam jejak untuk bertukar antara lapisan, vias berbilang akan digunakan. Design mesti dipertimbangkan dengan hati-hati. Dalam rancangan sebenar, kapasitas parasit boleh dikurangkan dengan meningkatkan jarak antara melalui dan kawasan tembaga (Anti-pad) atau mengurangkan diameter pad.

Terdapat kapasitas parasit dalam botol dan induksi parasit. Dalam rancangan sirkuit PCB digital kelajuan tinggi, kerosakan disebabkan oleh induksi parasit vias sering lebih besar daripada kesan kapasitasi parasit. Induktansi seri parasitik akan lemahkan kontribusi kondensator bypass dan lemahkan kesan penapisan seluruh sistem kuasa. Kita boleh guna formula empirik berikut untuk menghitung induksi parasit melalui:

di mana L merujuk kepada induktan melalui, h ialah panjang melalui, dan d ialah diameter lubang tengah. Ia boleh dilihat dari formula bahawa diameter melalui mempunyai pengaruh kecil pada induktan, dan panjang melalui mempunyai pengaruh terbesar pada induktan. Masih menggunakan contoh di atas, induktan melalui boleh dihitung sebagai:

Jika masa naik isyarat adalah 1ns, maka kemudahan yang sama adalah: XL=ϢL/T10-90=3.19Ω. Kemudahan tersebut tidak boleh lagi diabaikan apabila arus frekuensi tinggi berlalu. Perhatian istimewa patut diberikan kepada fakta bahawa kondensator bypass perlu melalui dua vias apabila menyambung pesawat kuasa dan pesawat tanah, Sehingga induksi parasit dari botol akan meningkat secara eksponensial.

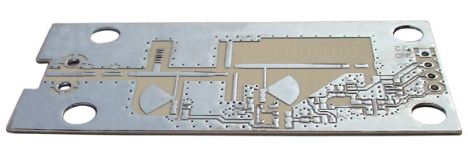

Melalui analisis atas ciri-ciri parasit vias, ia boleh dilihat bahawa dalam rancangan PCB kelajuan tinggi, tampaknya vias sederhana akan sering membawa kesan negatif besar kepada rancangan sirkuit. Untuk mengurangi kesan negatif disebabkan oleh kesan parasit vias, perkara berikut boleh dilakukan dalam rancangan:

·Dari pertimbangan kualiti kos dan isyarat, pilih saiz yang masuk akal melalui saiz. Jika diperlukan, anda boleh pertimbangkan menggunakan saiz yang berbeza vias. Contohnya, untuk saluran kuasa atau tanah, and a boleh pertimbangkan menggunakan saiz yang lebih besar untuk mengurangi impedance, dan untuk jejak isyarat, anda boleh menggunakan saluran yang lebih kecil. Sudah tentu, sebagaimana saiz melalui menurun, biaya yang sepadan akan meningkat.

·Dua formula yang dibincangkan di atas boleh dikatakan bahawa penggunaan PCB yang lebih tipis adalah bermanfaat untuk mengurangi dua parameter parasit melalui.

·Jejak isyarat pada papan PCB tidak patut diubah sebanyak yang mungkin, yang bermakna bahawa vial tidak perlu digunakan sebanyak yang mungkin.

·Pins bekalan kuasa dan tanah seharusnya dibuang dekat, dan memimpin antara laluan dan pin seharusnya sebagai pendek yang mungkin. Bertimbangkan bermain vial berbilang secara selari untuk mengurangi induksi yang sama.