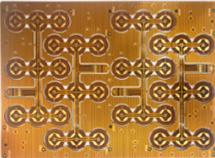

在電子產品的電磁干擾設計中,開發人員越來越意識到PCB電路中電磁干擾處理的重要性。 如果在此階段可以抑制EMI問題,則可以解决約60%的干擾問題。 那麼,如何在電路板設計過程中最大限度地抑制干擾?

規則1:高速訊號路由遮罩規則

在裡面 高速PCB 設計, 時鐘和記錄道等關鍵高速訊號線需要遮罩. 如果沒有盾牌或只是部分盾牌, 會導致電磁干擾洩漏. 建議遮罩線每1000密耳開一個孔接地.

規則2:高速訊號的閉環路由規則

由於PCB板密度新增, 許多PCB佈局工程師在佈線過程中容易出錯, 那就是, 高速訊號網絡(如時鐘訊號)在路由時產生閉環結果 多層PCB. 這種閉環的結果將產生環形天線,並新增電磁干擾的輻射强度.

規則3:高速訊號的開環路由規則

規則2提到,高速訊號的閉環將導致電磁干擾輻射,但開環也會導致電磁干擾輻射。

對於高速訊號網絡,例如時鐘訊號,當多層PCB佈線時,一旦出現開環結果,就會產生線性天線,這將新增EMI輻射强度。

規則4:高速訊號的特性阻抗連續性規則

對於高速訊號,在層間切換時必須確保特性阻抗的連續性,否則會新增EMI輻射。 換句話說,同一層佈線的寬度必須是連續的,不同層佈線的阻抗必須是連續的。

規則5:高速PCB設計的佈線方向規則

相鄰兩層之間的佈線必須遵循垂直佈線的原則,否則會導致線路之間的串擾並新增EMI輻射。 簡而言之,相鄰佈線層遵循水准和垂直佈線方向,垂直佈線可以抑制線路之間的串擾。

規則6:高速PCB設計中的拓撲結構規則

在高速PCB設計中,電路板特性阻抗的控制和多負載情况下的拓撲設計直接决定了產品的成敗。

規則7:軌跡長度的共振規則

檢查訊號線的長度和訊號的頻率是否構成共振,即當佈線長度是訊號波長1/4的整數倍時,佈線會共振,共振會輻射電磁波並造成干擾。

規則8:返回路徑規則

所有高速訊號必須具有良好的返回路徑。 盡可能確保時鐘等高速訊號的返回路徑最小化。 否則會大大新增輻射,輻射的大小與訊號路徑和返回路徑包圍的面積成正比。

規則9:設備去耦電容器放置規則

去耦電容器的位置非常重要。 不合理的佈局根本不會產生解耦效果。 其原理是:靠近電源引脚,由電容器的電源線和地線包圍的面積最小。

只要這九條規則在 PCB設計 過程, 在正式控制電磁干擾之前,可以成功避免大部分干擾, 為後續工作提供了極大的便利.