印刷電路板校對1 DSP系統 干擾產生分析,以建立穩定可靠的DSP系統, 必須從各個方面消除干擾, 即使不能完全消除, 它必須盡可能地最小化. 對於DSP系統, 主要干擾來自以下幾個方面:1. 輸入和輸出通道干擾. 指通過前向通道和後向通道進入系統的干擾, 例如DSP系統的資料獲取連結. 干擾通過感測器疊加在訊號上, 這新增了資料獲取的誤差. 在輸出連結中, 干擾會新增輸出數據誤差, 甚至犯了一個完全的錯誤, 導致系統崩潰. 可以合理使用光耦器件來减少輸入和輸出通道的干擾, 感測器和DSP主系統的干擾可用於電力隔離干擾. 2 電源系統干擾. 整個DSP系統的主要干擾源. 電源在向系統供電的同時,將其雜訊添加到電源中. 在電源晶片的電路設計過程中,電源線必須解耦. 3 空間輻射耦合干擾. 通過輻射的耦合通常稱為串擾. 電流流過導線時產生的電磁場中會發生串擾, 電磁場在相鄰導線中產生瞬態電流, 導致附近訊號失真甚至出錯. 串擾的强度取決於器件和導線的幾何尺寸和分離距離. DSP佈線中, 訊號線間距越大,離地線越近, 减少串擾越有效. 2設計 印刷電路板 對於干擾的原因. 下麵顯示了如何减少中的各種干擾 印刷電路板生產 DSP系統流程.

為了提高訊號質量, 降低佈線難度, 並提高系統的EMC, 在DSP高速數位電路的多層板的分層設計中 印刷電路板 proofing, 通常採用多層板的層壓設計. 堆疊設計可以提供最短的返回路徑, 减少耦合面積, 抑制差模干擾. 在堆疊設計中, 專用電源層和接地層的分佈, and the tight coupling of the ground layer and the power layer is good for suppressing common mode interference (using adjacent planes to reduce the AC impedance of the power plane). 以圖1所示的4層板為例,說明層壓設計. 採用這種方法有很多優點 4層印刷電路板設計結構. 頂層下麵有一個電源層, 組件的電源插腳可以直接連接到電源,而無需穿過接地層. The key signal is selected on the bottom layer (bottorn layer), 囙此,重要的訊號佈線空間更大, 並且盡可能將設備放置在同一層上. 如果沒有必要, 不要製作雙層零件板, 這將新增裝配時間和裝配複雜性. 比如頂層, 僅當頂層組件過於密集時, 高度有限,發熱量低, such as decoupling capacitors (patch) are placed on the bottom layer. 對於DSP系統, 可能有大量導線需要佈線, 採用分層設計, 導線可以在內層佈線. 如果傳統的通孔浪費了大量寶貴的佈線空間, 失明的/埋入過孔可用於新增佈線面積.

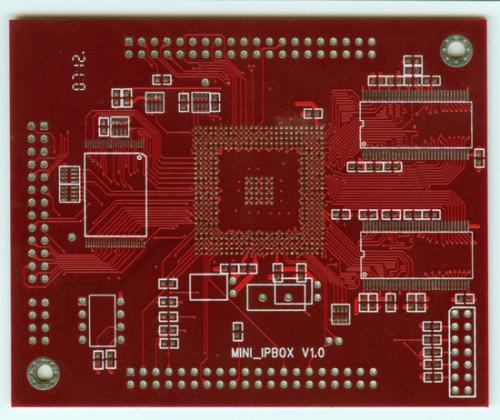

印刷電路板打樣佈局設計 為了獲得DSP系統的最佳效能, 組件的佈局非常重要. 放置DSP, 閃光, SRAM, 和可程式設計邏輯器件優先, 仔細考慮佈線空間, 然後根據功能獨立性原則放置其他集成電路, 最後考慮I的位置/O埠. 結合上述佈局,考慮 印刷電路板 尺寸:如果尺寸太大, 列印的行太長, 阻抗將新增, 雜訊阻力將降低, 董事會成本將新增; 如果 印刷電路板 太小了, 散熱不好, 空間有限, 相鄰線路容易受到干擾. 因此, 應根據實際需要選擇設備, 結合佈線空間, 並粗略計算 印刷電路板. 在佈置DSP系統時, 特別注意以下裝置的放置.

(1) High-speed signal layout In the entire DSP system, 主要的高速數位信號線位於DSP、閃光和SRAM之間, 囙此,設備之間的距離應盡可能近, and their connections should be as short as possible, 它們應該直接連接. 因此, 為了减少輸電線路對訊號質量的影響, 高速訊號軌跡應盡可能短. Also consider that many DSP chips with speeds up to several hundred MHz require a snake-shaped winding (delay tune). 這將在下麵的接線中強調.

(2) The layout of digital-analog devices is mostly not a single functional circuit in a DSP system. 使用了大量的CMOS數位器件和數模混合器件, 所以數位/類比佈局應分開. 類比信號設備盡可能集中, 囙此,類比地可以在整個數位地的中間繪製屬於類比信號的獨立區域, 以避免數位信號對類比信號的干擾. 對於一些數模混合設備, 例如D/A轉換器, 它們傳統上被視為類比設備, 置於類比地上, 並配備數位回路,允許數位雜訊迴響到信號源,以减少數位雜訊對類比地面的影響.

(3) The layout of the clock As far as possible from the clock, 晶片選擇和匯流排訊號, I/O線路和連接器應盡可能遠離. DSP系統的時鐘輸入極易受到干擾, 它的處理非常關鍵. 始終確保時鐘發生器盡可能靠近DSP晶片, 並使時鐘線盡可能短. 時鐘晶體振盪器的外殼優選接地.

(4) Decoupling layout In order to reduce the instantaneous overshoot of the voltage on the power supply of the integrated circuit chip, 集成電路晶片中添加了去耦電容器, 它可以有效地消除毛刺對電源的影響,並减少電源回路對電源的反射 印刷電路板 . 添加去耦電容器可以繞過積體電路設備的高頻雜訊, 也可用作儲能電容器,提供和吸收集成電路開門和關門的暫態充放電能量.

對於 印刷電路板打樣 in the DSP system, 為每個集成電路放置去耦電容器, 例如DSP, SRAM, Flash, 等., 並將其添加到晶片的每個電源和接地之間, and pay special attention to the decoupling capacitors as close as possible to the power supply terminal (source) and IC component pins (pin). Ensure the purity of the current from the power supply terminal (sotlrce terminal) and the IC, 並盡可能縮短雜訊路徑. 如圖2所示, 處理電容器時, 使用大通孔或多通孔, 過孔和電容器之間的接線應盡可能短且厚. 當兩個過孔之間的距離太長時, 這是不好的,因為路徑太大; 最好是去耦電容器的兩個過孔盡可能靠近, 使雜訊以最短的路徑到達地面.