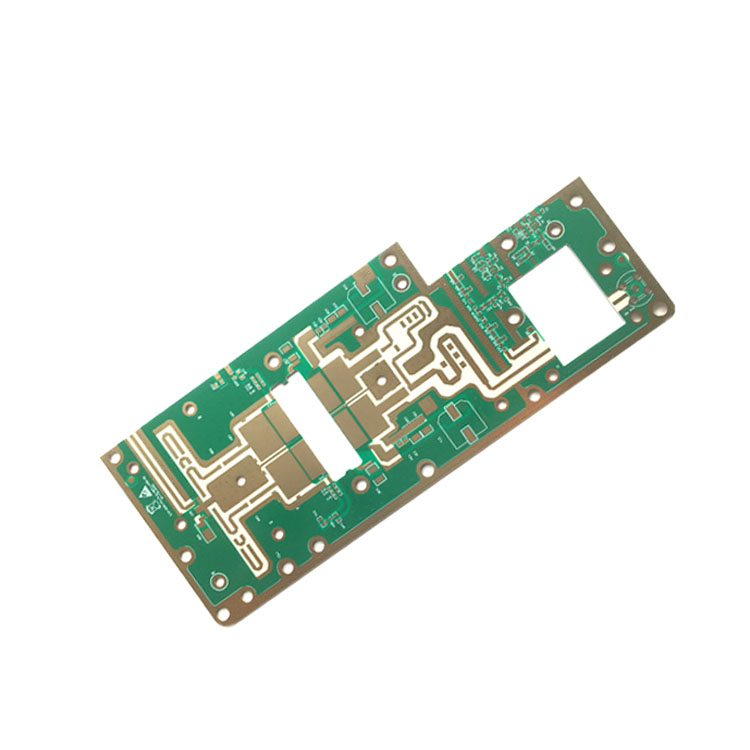

高頻PCB板是指頻率在1GHz以上的電路板,對各種物理性能、精度和技術參數要求非常高。 它經常用於汽車防撞系統、衛星系統、無線電系統等領域。 高頻PCB板是佈線中的一個重要環節,它直接影響高頻、高速的工作。 今天我將討論如何佈線高頻和高速PCB板。

高頻電路板應該如何佈線? 特別注意高頻電路板的接線。 基於微波技術的基本知識,當訊號的波長小到與傳輸線的長度成比例時,我們不能根據傳統的集總電路方法來分析電路,而是使用現場理論分析,這就是傳輸線理論。 當然,在正常情况下,我們設計的電路的訊號頻率不會太高。 波長=訊號傳送速率/訊號頻率。 通常,訊號的傳送速率與傳輸介質的介電常數有關。 我們不妨將訊號傳送速率設定為光速。 3*10^8m/s(實際小於)對於300Mhz訊號,波長為1m,通常PCB板上的線路長度不會達到1m。 由此可見,我們不必過於擔心低頻訊號。

高頻PCB佈線要求是什麼? 當高頻PCB板的訊號頻率高時,為了减少訊號的反射,需要在傳輸線上進行阻抗匹配。 通常,單端線路可以用於遠程匹配或端子匹配,並且差分訊號通常橋接在端子附近的差分線路之間。 電阻匹配。 就我最近的主題而言,LVDS訊號在差分線路上的傳輸需要在接收端放置一個100歐姆的電阻器以進行阻抗匹配。 根據傳輸線的知識,差分線的特性阻抗必須是100歐姆才能完全匹配。 囙此,差分線的線寬和線間距有著嚴格的要求。 差分線的特性阻抗與襯底的介電常數、襯底的厚度、導線的銅厚度、差分線的線寬、差分線距離、襯底的生油厚度等有關。計算公式也相當複雜。

高頻電路板接線技巧1。 高頻電路器件的引脚之間交替的引線層越少越好

所謂“引線的層間交替越少越好”,是指在元件連接過程中使用的過孔(Via)越少越好。 過孔可以帶來約0.5pF的分佈式電容,减少過孔的數量可以顯著提高速度並降低數據錯誤的可能性。

2.高速電子設備引脚之間的引線應盡可能少地彎曲

高頻電路佈線的引線最好採用全直線,需要轉彎。 它可以通過45度虛線或圓弧轉動。這一要求僅用於提高低頻電路中銅箔的固定强度,而在高頻電路中,這一要求得到了滿足。 一個要求可以减少高頻訊號的外部發射和相互耦合。

3.高頻電路器件引脚之間的引線越短越好

訊號的輻射强度與訊號線的跡線長度成比例。 高頻訊號引線越長,就越容易耦合到靠近它的部件。囙此,對於時鐘、晶體振盪器、DDR數據、LVDS線、USB線、HDMI線等訊號,要求高頻訊號線盡可能短。

高頻PCB板佈線規則首先,高頻PCB板的佈線需要注意訊號線的緊密平行佈線引入的“串擾”高頻電路佈線應該注意訊號線緊密平行佈線帶來的“串擾“。 串擾是指未直接連接的訊號線之間的耦合現象。 由於高頻訊號以電磁波的形式沿著傳輸線傳輸,訊號線將充當天線,電磁場的能量將在傳輸線周圍發射。 由於訊號之間的電磁場的相互耦合,產生了不期望的雜訊訊號。 稱為相聲。 PCB層的參數、訊號線的間距、驅動端和接收端的電力特性以及訊號線的端接方法都對串擾有一定的影響。 囙此,為了减少高頻訊號的串擾,佈線時需要盡可能做到以下幾點:

(1)在佈線空間允許的情况下,在串擾較嚴重的兩根導線之間插入接地線或接地平面,可以起到隔離作用,减少串擾;

(2)當訊號線周圍的空間存在時變電磁場時,如果無法避免平行分佈,可以在平行訊號線的對面佈置大面積的“地”,以大大减少干擾;

(3)如果佈線空間允許,新增相鄰訊號線之間的間距,减少訊號線的平行長度,並儘量使時鐘線與關鍵訊號線垂直,而不是平行;

(4)如果同一層中的平行佈線幾乎是不可避免的,那麼在兩個相鄰層中,佈線的方向必須相互垂直;

(5)在數位電路中,通常的時鐘訊號是具有快速邊緣變化的訊號,其具有高的外部串擾。 囙此,在設計中,時鐘線應該被地線包圍,並且應該使用更多的地線孔來减少分佈電容,從而减少串擾;

(6)對於高頻訊號時鐘,儘量採用低壓差分時鐘訊號和包地管道,並注意接地打孔的完整性;

(7)不要將未使用的輸入端子掛起,而是將其接地或連接到電源(電源也在高頻訊號回路中接地),因為懸掛的電線可能相當於發射天線,接地會抑制發射。 實踐證明,用這種方法消除串擾有時能立竿見影。

2.將高頻數位信號的地線與類比信號的地線隔離當類比地線、數位地線等連接到公共地線時,使用高頻扼流磁珠連接或直接隔離並選擇合適的地方進行單點互連。 高頻數位信號的地線的接地電位通常不一致。 兩者之間通常直接存在一定的電壓差。 此外,高頻數位信號的地線經常包含高頻訊號的非常豐富的諧波分量。 當數位信號地線和類比信號地線直接連接時,高頻訊號的諧波會通過地線耦合干擾類比信號。 囙此,在正常情况下,高頻數位信號的地線和類比信號的地線要隔離,可以在合適的位置使用單點互連方法,也可以使用高頻扼流圈磁珠互連方法。

3.在集成電路塊的電源引脚上添加高頻去耦電容器在附近的每個集成電路塊電源引脚上都添加高頻去耦合電容器。 新增電源引脚的高頻去耦電容器,可以有效抑制高頻諧波對電源引脚的干擾。

第四,要確保良好的訊號阻抗匹配在訊號傳輸過程中,當阻抗不匹配時,訊號會在傳輸通道中反射,反射會導致合成訊號形成過沖,導致訊號在邏輯閾值附近波動。

消除反射的基本方法是使傳輸訊號的阻抗匹配良好。 由於負載阻抗和傳輸線的特性阻抗之間的差越大,反射就越大,囙此訊號傳輸線的特徵阻抗應該盡可能地等於負載阻抗。 同時,請注意,PCB上的傳輸線不能有突然的變化或拐角,並儘量保持傳輸線每個點的阻抗連續,否則傳輸線的各個部分之間會有反射。 這要求在高速PCB佈線過程中,必須遵守以下佈線規則:

(1)LVDS佈線規則。 需要LVDS訊號差分跡線,線寬7mil,線路距離6mil,目的是將HDMI的差分訊號阻抗控制在100+-15%歐姆;

(2)USB接線規則。 需要USB訊號差分佈線,線路寬度10mil,線路間距6mil,地線和訊號線間距6mil;

(3)HDMI佈線規則。 需要HDMI訊號差分路由,線寬10mil,線間距6mil,每兩組HDMI差分訊號對間距超過20mil;

(4)DDR佈線規則。 DDR1跡線要求訊號盡可能不穿過孔,訊號線具有相等的寬度,並且線間隔相等。 跡線必須滿足2W原理,以减少訊號之間的串擾。 對於DDR2及以上的高速器件,還需要高頻數據。 這些線的長度相等,以確保訊號的阻抗匹配。

以上是對佈線規則、佈線技巧以及如何佈線高頻高速PCB板的詳細說明。 只有注意和避免,才能保持訊號傳輸的完整性,防止因地線分裂而引起的“接地反彈現象”。 “