1.引言

隨著 PCB板 設計複雜性, 除反射外的信號完整性分析, 串擾, 和EMI, 穩定可靠的電源已成為設計人員的重點研究方向之一. 尤其是當開關器件數量新增,核心電壓降低時, 電源的波動往往會給系統帶來致命的影響, 於是人們提出了一個新名詞:權力誠信, PI (power integrity). 在當今的國際市場上, IC設計更加成熟, 但電源完整性設計仍然是一個薄弱環節. 因此, 本文提出了電源完整性問題的產生 PCB板, 分析影響電源完整性的因素, 並提出了解决中電源完整性問題的優化方法和經驗設計 PCB板, 具有較强的理論分析和實際工程應用價值.

2、電源雜訊的原因及分析

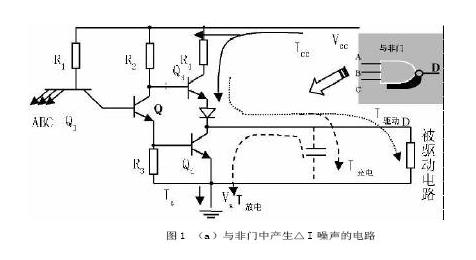

用反及閘電路圖分析了電源雜訊的來源. 電路圖顯示了3輸入反及閘的結構. 因為反及閘是數位設備, 它通過在“1”和“0”級別之間切換來工作. 隨著集成電路科技的不斷進步, 數位設備的切換速度越來越快, 這引入了更多 高頻 組件, 回路中的電感容易引起電源高頻波動. 如圖1所示, 當反及閘的輸入全部處於高壓時, 電路中的3極管接通, 電路瞬間短路, 電源對電容器充電,同時流入地線. 此時, 因為電源線和地線上的寄生電感, 我們從公式V=LdI知道/這將在電源線和地線上產生電壓波動, 以及由電平上升沿引入的δI雜訊,如圖2所示. 當反及閘的輸入處於低電流水准時, 此時電容器放電, 接地線上會產生較大的δI雜訊. 此時, 電源只有電路暫態短路引起的電流突變, 因為電容器沒有電荷, 當前突變小於上升沿. 從反及閘電路分析, 我們知道,電源不穩定的根源主要在於兩個方面:一是器件高速開關狀態, 瞬態交流電流過大.

第二個是電流回路中存在的電感. 所謂的地面電源完整性問題是指 高速PCB 當大量晶片同時打開或關閉時, 電路中將產生較大的瞬態電流, 由於電感電阻的存在,會在電源線和地線上產生電壓波動. 瞭解電源完整性問題的性質, 我們知道要解决電源完整性問題, 首先, 對於高速設備, 我們添加了一個去耦電容器,以消除其 高頻 雜訊分量, 减少訊號的瞬態時間; 對於回路中存在的電感, 我們必須考慮電源的分層設計.

3、去耦電容器的應用

去耦電容器在高速PCB設計中起著重要作用,其放置也非常重要。 這是因為當電源向負載短時供電時,電容器中的存儲電荷可以防止電壓降,如電容器放置不當會使線路阻抗過大,影響電源。 同時,電容器可以濾除設備高速切換過程中的高頻雜訊。 在高速PCB設計中,通常在晶片的電源輸出端和電源輸入端分別添加去耦電容器。 電源附近的電容值通常較大(如10mF)。 這是因為在PCB中通常使用直流電源,並且電容器的諧振頻率可以相對較低,以過濾電源的雜訊。 同時,大電容可以保證電源輸出的穩定性。 對於連接到去耦電容器引脚位置電源的晶片,其電容值通常較小(如0.1mF),這是因為在高速晶片中,雜訊頻率通常較高,這要求添加的去耦電容器諧振頻率較高,即去耦電容器的容量較小。

對於去耦電容器的放置,我們知道位置不當會新增線路阻抗,降低其諧振頻率,影響電源。 對於晶片或電源中的去耦電容和電感,我們可以通過公式進行計算。 五十:電容器與晶片之間的線路長度; R:線路半徑; D:電源線與地面之間的距離。 囙此,我們知道要减小電感L,必須减小L和D,即應减小去耦電容器和晶片形成的回路面積,即電容器和晶片應盡可能靠近晶片設備。

4.電源回路的設計

確保電源完整性, 我們知道,良好的配電網至關重要. 首先, for the 設計 of the power line and ground wire, we should ensure that the line width is thick (such as 40mil, while the ordinary signal line is 10mil), 盡可能降低其阻抗值. 隨著晶片速度越來越快, 根據5/5規則, 我們越來越多地使用 多層板, 由專用電源層供電,並由專用層進行電路連接, 從而降低線路的電感.